基于FPGA的新型雷達圖像處理系統設計與實現

達 平,張金林,谷京朝

(空軍預警學院,武漢430019)

0 引 言

隨著半導體器件的不斷更新換代及嵌入式系統的飛速發展,雷達信號的顯示技術也發生了翻天覆地的變化。傳統的雷達信號顯示大多數采用單片機控制,主要依靠硬件電路實現,技術成熟,靈活性好,但設備體積大,可移植性和通用性差。近年來,雷達組網系統向數字化、信息化、智能化不斷發展,越來越多的預警探測裝備接入情報網絡傳輸分發系統,這就對雷達信號的顯示終端提出了新的要求。本文針對雷達視頻信號數據量大、對處理速度要求高的特點,介紹了一種基于現場可編程門陣列(FPGA)的雷達視頻信號采集處理系統的設計方案,并在工程中得到了很好的應用。FPGA豐富的內部資源可以充分滿足高速視頻采集處理系統的要求。FPGA的硬件可編程性和可重構方面的應用也使得系統集成度更高,工作模式切換更簡單。

1 系統總體架構

本文設計的雷達視頻信號采集處理系統從功能上主要分為隔離與驅動模塊、模/數(A/D)轉換模塊、FPGA采集控制模塊、圖像顯示模塊等。其中,FPGA是該系統的核心器件,主要實現邏輯控制,與計算機之間保持通信。系統的總體架構框圖如圖1所示。

當系統工作時,首先將雷達模擬視頻信號輸入到隔離與驅動模塊進行緩沖放大及同步處理,FPGA通過I2C總線發出A/D控制信號,使A/D轉換模塊對其解碼,轉換為雷達數字視頻信號。然后將其送入FPGA中進行邊沿檢測、濾波及視頻壓縮等邏輯運算處理。FPGA通過地址總線和數據總線與PC/104計算機系統進行通信,計算機可以實時地給FPGA發送控制信號,完成雷達視頻信號的采集、處理和存儲等功能。最后FPGA將處理完畢的雷達數字視頻信號送回到A/D轉換模塊中,編碼為雷達模擬視頻信號后送至圖像顯示模塊進行雷達情報的顯示。

2 隔離與驅動模塊設計

隔離與驅動模塊是雷達模擬視頻信號前期必不可少的預處理過程,主要功能是將輸入的雷達模擬視頻信號經過隔離和驅動,送入A/D轉換模塊進行模數變換,主要分為緩沖放大電路、同步觸發電路和同步分離電路。

2.1 緩沖放大電路

緩沖放大電路主要是由射極跟隨器和多級放大器構成的。射極跟隨器的輸入阻抗高,對前級電路影響小,可以作為多級放大器的第一級。同時它的輸出阻抗低,帶負載能力強,可作為多級放大器的輸出級。因此射極跟隨器在多級放大器中應用非常廣泛,通常用作緩沖級,調整直流偏置。

2.2 同步觸發電路

視頻同步觸發電路主要是對放大后的雷達模擬視頻信號進行濾波,濾除毛刺、尖峰等,并且識別出脈寬信號,找到雷達視頻信號的起始點。

2.3 同步分離電路

同步信號分離電路要保證正確地重現雷達發送終端的視頻圖像,主要是從雷達模擬視頻信號中提取出復合同步信號(SYNC),可以用微積分電路計算出微分時間常數,與觸發器組合實現。復合同步分離電路主要由運算放大器、二極管、低通濾波器、比較器組成。本系統采用的視頻同步分離芯片是LM1881,可提取出復合同步、行場同步、奇偶場識別等信號。

3 A/D轉換模塊

數字視頻信號相對于模擬視頻信號來說,可以進行無數次復制且復制過程無失真,長時間存放后視頻質量不會降低,并且能夠進行非線性編輯。因此,模擬視頻信號通常都要轉換成數字視頻進行處理、存儲和傳輸。現今模數轉換技術與數模轉換技術都非常成熟,相關芯片設備等應用也十分方便,常用的有AD公司和TI公司的模數轉換器(ADC)與數模轉換器(DAC)等。

本系統選用飛利浦公司生產的視頻解碼芯片SAA7113及視頻編碼芯片SAA7121,它們內置了多標準編解碼器,能夠實現PAL、NTSC、SECAM復合視頻的數字編解碼,使用9位A/D轉換器,可以接收復合視頻和Y/C分量視頻,具有很好的圖像效果[1]。其主要作用是通過編解碼將模擬視頻信號與標準的視覺持久示波器(VPO)數字信號進行轉換。

解碼芯片SAA7113將隔離與驅動模塊送來的模擬視頻信號作為輸入,經過模數轉換為數字視頻信號后送入FPGA進行后續處理。編碼芯片SAA7121將FPGA處理完成的數字視頻信號作為輸入,經過數模轉換后送入圖像顯示模塊進行視頻顯示。

編解碼芯片的控制信號由FPGA產生,通過Xilinx公司的ISE集成開發軟件,運用超高級定義語言(VHDL)編寫控制程序,具體程序如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity AD is

Port(start:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

datain:in STD_LOGIC_VECTOR(8DOWNTO 0);

dataout:out STD_LOGIC_VECTOR (8 DOWNTO 0);

re:out STD_LOGIC;

res:out STD_LOGIC);end AD;

architecture Behavioral of AD is

signal c:STD_LOGIC_VECTOR(1DOWNTO 0);

begin

process(clk)

begin

if rst=‘1’then

if clk'event and clk=‘1’then

case c is

when“00”=>

re<=‘0’;

res<=‘1’;

dataout<=datain;

when“01”=>

re<=‘1’;

res<=‘0’;

when“11”=>

if start=‘0’then

c<=c-‘1’;

end if;

……

使用ISE軟件對程序進行綜合,得到的RTL級綜合圖如圖2所示。使用Modelsim仿真軟件對程序進行仿真,仿真結果如圖3所示。

4 FPGA采集控制模塊

FPGA是整個視頻處理系統的時序邏輯控制的核心,主要實現視頻信號的采集、分析、處理、存儲、輸出等功能。FPGA的規模比較大,適合于時序、組合等邏輯電路的應用。它具有設計開發周期短、設計制造成本低、開發工具先進、標準產品無需測試、質量穩定以及實時在線檢測等優點[2]。

按照系統的功能特點,可將FPGA的內部邏輯資源分為4個部分,即FPGA圖像處理單元、FPGA接口邏輯控制單元、I2C通信單元和數據緩存單元。如圖4中虛線框內所示。

圖4 FPGA的采集控制模塊的功能單元圖

4.1 FPGA圖像處理單元

該單元主要接收其他單元送來的數據,對其進行處理,經過運算產生A/D控制信號,通過I2C通信單元控制A/D轉換模塊的工作模式。按照信號處理流程,主要分為邊沿檢測、空域濾波及H.264壓縮3個步驟。

邊緣檢測是圖像處理和計算機視覺中的基本前提,主要是對數字圖像中亮度明顯變化的點做出標記。邊緣檢測去除了視頻信號中許多不相關、可有可無的信息,將展示圖像結構屬性所必需的重要的信息保留下來,顯著減少了視頻信號的數據量。

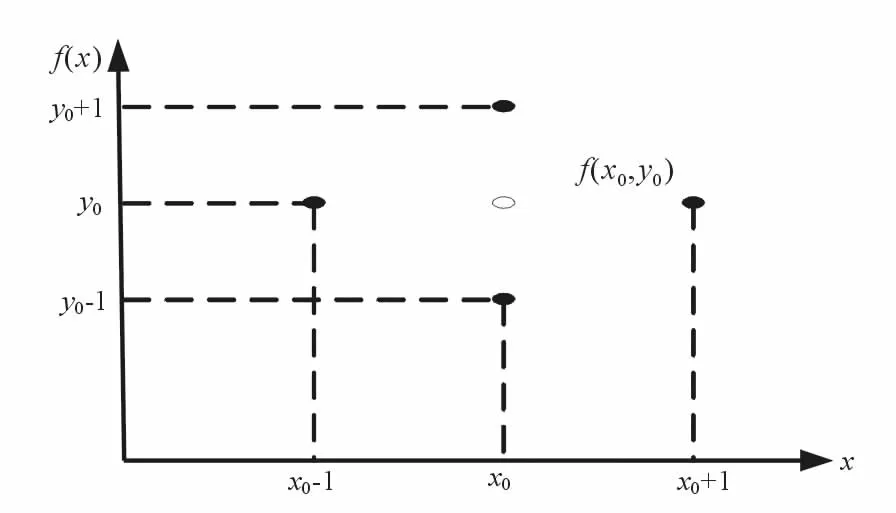

空域濾波是一種視頻信號的去噪平滑技術,它首先采用均值濾波方法,確定每一像素點附近4個點的像素值的中值,去除脈沖噪聲(采點位置如圖5所示);然后通過低通濾波器減小高斯噪聲、電子熱噪聲等;最后利用圖像銳化濾波對圖像的邊緣信息進行增強,補償壓縮引起的視頻信息衰減。

圖5 均值濾波采樣點分布圖

H.264視頻標準也稱為高等視頻編碼(AVC)標準,是一種面向塊的基于運動補償的編解碼器標準。H.264采用了幀內空間預測、整數變換與量化、環路濾波、熵編碼、幀間編碼中的運動補償預測等新技術,能夠在更低的帶寬下提供優質的視頻。它是以計算復雜度的增加為代價,換取編碼效率的提高。在同一重建圖像質量下,它的編碼效率比H.263和 MPEG-4提高了1.5~2倍[3]。

4.2 FPGA接口邏輯控制單元

本系統不僅要完成視頻信號的采集處理,還要進行時序邏輯控制,各個模塊間要協同工作,保持同步及通信暢通。因此在FPGA中設計此接口邏輯控制單元與PC/104計算機系統進行通信。計算機產生控制信號對FPGA進行實時的控制,通過地址總線和數據總線與其進行通信。

4.3 I2C通信單元

A/D轉換模塊中的解碼芯片SAA7113及編碼芯片SAA7121可以兼容全球各種視頻標準,在不同的國家應用時必須按照其使用的視頻標準對芯片內部的寄存器進行設置,否則就不能相應地輸出符合要求的信號。這個過程也稱為初始化過程,需通過I2C總線進行,遵從I2C總線協議[4]。

用VHDL編寫程序,燒寫在FPGA中,可控制SAA7113及SAA7121的工作狀態,準確調控各信號時序,可移植性好,能適應高速信號控制的需要。

4.4 數據緩存單元

FPGA斷電后數據丟失,每次工作時都需要在加電的情況下將程序重新下載到FPGA中,因此在系統設計的過程中,增加一個同步動態隨機存儲器(SDRAM)。將程序保存在SDRAM中,使每次加電后程序自動加載到FPGA中。

數字視頻信號經過FPGA邏輯運算單元處理后,在先進先出(FIFO)中以數據幀的形式暫存。由于FPGA的內部資源有限,且數據掉電丟失,故而也送至SDRAM中存儲。

5 結束語

針對目前雷達視頻信號的數據量大、信號格式類型繁多等問題,本文提出了基于FPGA的雷達視頻采集處理系統。該系統運用FPGA對雷達模擬視頻信號進行數字化,通過多級處理,實現雷達視頻信號的采集提取、去噪壓縮、高分辨率顯示。

與傳統的雷達視頻采集處理系統相比,本設計具有占用資源少、體積小、低功耗、可擴展性好、處理速度快等優點。目前,該設計已成功應用于某系統中,具有較高的工程應用價值,軍事經濟效益顯著。

[1]謝劍斌,徐暉.數字視頻處理與顯示[M].北京:電子工業出版社,2010.

[2]李林,謝代華,馮正勇.基于FPGA的數字光端機的設計與實現[J].重慶職業技術學院學報,2006,15(3):148-150.

[3]高文,趙德斌,馬思偉.數字視頻編碼技術原理[M].北京:科學出版社,2010.

[4]曾慶立,孟凡斌,陳善榮.基于CPLD的SAA7113的初始化及其控制設計[J].吉首大學學報,2009,30(6):66-70.