基于容柵傳感器和單片機的檢測系統

梁應選, 楊明亮

(陜西理工學院(北區)機械工程學院,陜西漢中723003)

0 引言

數顯式百分表大多采用容柵式傳感器,但由于大多未帶微機接口,使其應用受到限制。國內學者就如何應用容柵式傳感器和單片機構建檢測系統進行了研究,并取得了一定的研究和應用成果[1-2]。但大多都遵循:傳感器原理介紹→系統硬件構建→軟件編程等基本思路。以上思路固然無誤,但對于一線技術開發人員或單片機開發和應用的初學者來說,往往造成的結果是看得懂,做起來難。本文提出了結合容柵傳感器原理,先用數字示波器對數顯百分表輸出信號(CLK信號、Date信號)進行觀察,結合觀測到的信號加深對原理的理解,再結合原理介紹中數據信號的采樣過程,著重分析數顯百分表實際顯示數據與實際記錄的二進制數對應關系。在此基礎上,結合已有報道的容柵式傳感器數據采集系統成功的經驗就如何利用數顯百分表為前端傳感器,AT89S52單片機做為主控單元構建一個硬件結構簡單、實時性強的檢測系統,進行方案論證,并擇優方案,最終設計構建出較為理想的智能檢測系統。

1 容柵式傳感器輸出信號分析

容柵式傳感器輸出的電容信號經過容柵集成極芯片的處理可轉化為數字信號輸出。其中輸出信號有4根線,分別為電源線(+1.5 V)、地線(0 V)、時鐘控制線(CLK)和串行數據輸出線(Date)[3-4]。

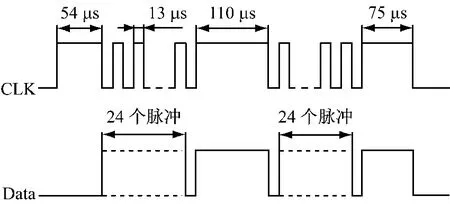

CLK為同步時鐘信號,在一次數據傳送中,開始為54μs的高電平,表示數據即將開始傳送。接下來是Date輸出兩組各有24個寬度為13μs的窄脈沖,前組為絕對數據;后組為相對數據。前后兩組數據之間有110μs的高電平作為間隔;最后是75μs的高電平,以示數據傳送結束,其輸出波形如圖1所示。

Date信號為數據信號,它包含了傳感器的位移信息。在數據采樣時,容柵芯片在CLK信號窄脈沖的下降沿對Date信號進行采樣,先后采樣兩組24位絕對數據和相對數據。

CLK時鐘脈沖串的第1組對應的信號是包含基準0的絕對數據;第2組是減去基準0后的實際的位移值,為相對數據。絕對數據計數范圍從000000H~FFFFFFH;相對數據有正負區分,可以進行清零。數據采用二進制編碼,低位在前,高位在后,最后位為符號位,數據采集以時鐘線每次CLK信號負跳變時刻為準進行數據采集。以上信號為非標準串行碼,幅值均為1.5 V。絕對數據不能清零(含基準0),相對數據可以清零,故本次我們將直接讀取相對數據進行研究。

2 數字示波器對輸出數據分析

2.1 數據的讀取

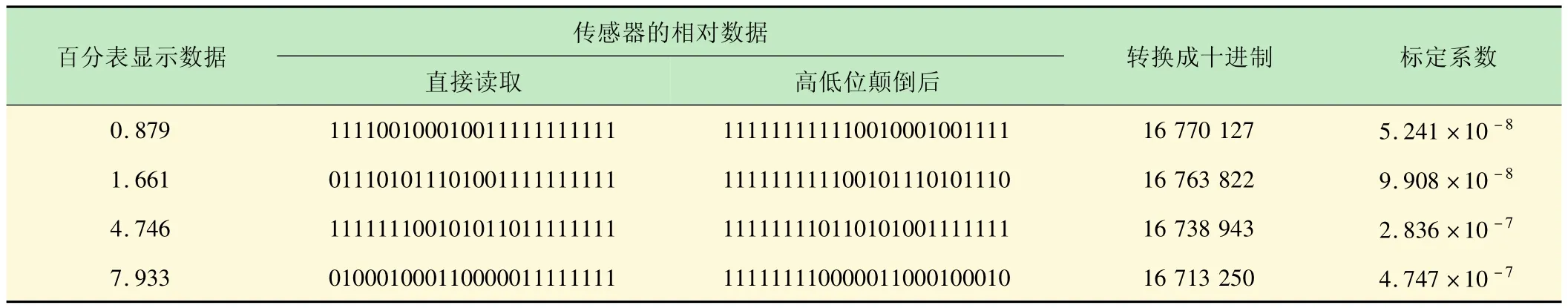

在數字示波器上可以觀察到如圖1所示數顯百分表輸出波形信號[5-6],CLK一個脈沖下降沿就可以讀對應這個脈沖寬度內的Date數據的狀態(高電平為1,低電平為0)。表1、2為測量時讀到的相對數據的二進制。

圖1 容柵式傳感器輸出脈沖時序圖

2.2 數據分析處理

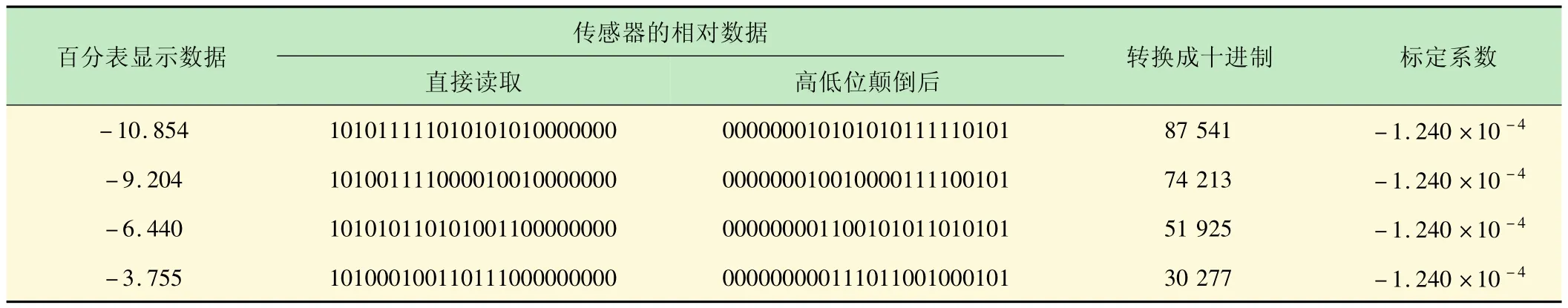

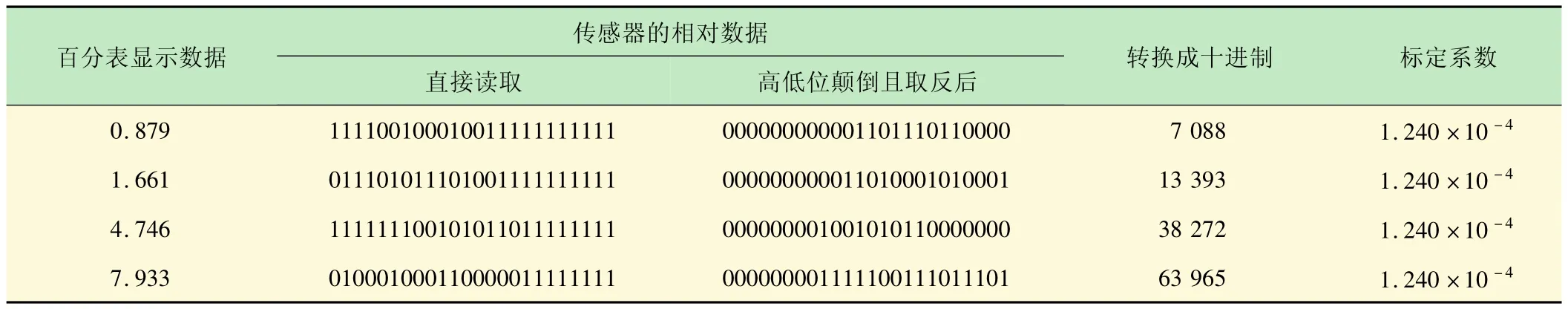

由表1、2可以看出,正數標定的系數為非常數;而負數的標定系數為常數。進一步觀察可以發現,傳感器輸出的相對數據為正數時,其二進制最高位都是“1”,負數的最高位都是“0”,如果給正數二進制取反,那么就會得到表3中的數據。

取反后可發現,正數標定的系數為常數。標定系數是用數顯表顯示的值除以傳感器正數的相對數據取反后的值(負數直接讀取的相對數據)。在后續的軟件編程時將數顯表的實際值擴大1 000倍變成整數,即將標定系數擴大1 000倍定為0.124,這樣便于數據處理顯示時數據的拆分。在數據采集編程時,首先判斷完讀取的數據的正負號(最高位為1是正號,最高位為0是負號)后,再選擇是否需要取反,再經過單片機對采集數據處理,最后就可直接顯示采集數據的正負及大小。

表1 直接讀取的傳感器的相對數據(正數)

表2 直接讀取的傳感器的相對數據(負數)

表3 對正數的相對數據取反后的數據

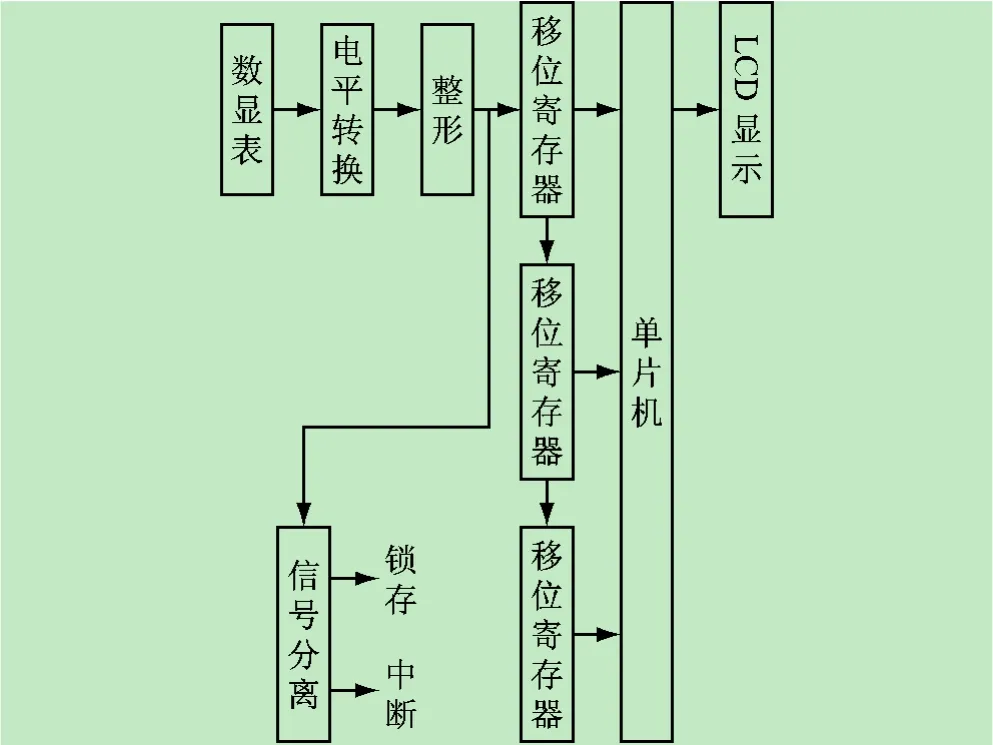

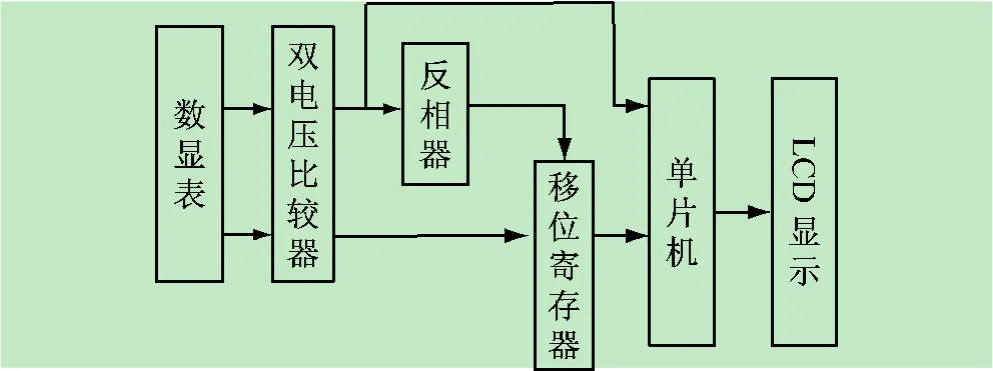

3 傳統測量系統硬件方案的論證

圖2為現有文獻報道的測量系統方案。它由3片8位移位寄存器接收24位數據信號,通過片選控制分3次讀入結果,為了準確無誤地讀取信號,必須使單片機在進入第2組數據時就產生中斷讀取數據。為了告訴單片機鎖存完畢進行正確的讀取還須分離出鎖存信號。系統通過中斷的方式對容柵式傳感器數據信號進行分組,它由單穩態觸發器產生的外部中斷進行控制,當產生中斷后就讀取單片機I/O口的數據;當串行數據經移位寄存器轉化為并行數據后經鎖存器鎖存,這時所有的24 bit可以全部通過單片機的某一I/O口,然而單片機只有8 bit口,系統則用片選法來控制數據的讀入,單片機的另一I/O口分別與3片鎖存器相連,在讀取數據時選通相應的鎖存芯片[7-9]。這種方案無疑是可行的,然而大部分工作靠硬件完成,沒有充分利用軟件的功能,測量系統硬件組成相對復雜,硬件成本較高。

圖2 傳統方案框圖

4 改進后測量系統硬件方案的論證及擇優

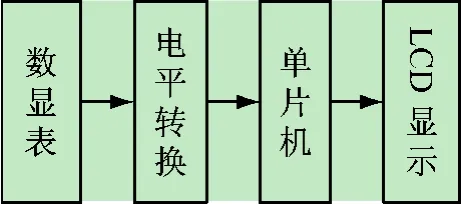

4.1 方案一

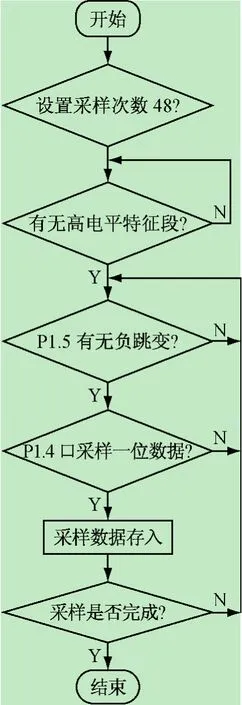

方案一框圖如圖3所示,將從傳感器出來的信號(CLK和Data)進行電平轉換后,分別送入單片機的2個I/O(假如CLK 接 P1.5,Data接 P1.4)。數據采集程序要解決的主要問題是確定數據采集的起始條件。根據圖1可知,容柵芯片在CLK信號窄脈沖的下降沿對Date信號進行采樣,CLK信號每次負跳變一次,即可采樣一位Date信號數字脈沖,共48次就可先后將兩組24位絕對數據數據和相對數據全部采樣完畢。計算時只采用后24位數據。在編程時要充分考慮指令執行的時間不能超過時鐘脈沖的周期間隔,故該部分程序擬采用匯編語言編程,以便保證數據采集的正確性。其他電平轉換電路部分及顯示部分軟硬件設計和采集數據處理子程序設計與下述方案二相同,在此暫不做敘述。采樣程序流程圖如圖4所示。

圖3 方案一框圖

該方案的優點是硬件電路少,比較直觀地體現信號的采集路徑及過程,經濟性能高,但缺點是軟件控制數據傳送速度較慢,占用的檢測時間長,不如硬件電路的實時性好,且采集數據處理較麻煩。

4.2 方案二

方案二框圖如圖5所示,用1片移位寄存器來進行數據的傳輸,省掉了傳統方案中兩片移位寄存器和信號分離電路,并結合軟件功能使硬件電路更為簡單,降低硬件成本的同時,仍能確保系統運行的可靠性。

采用一個8位移位寄存器成功與否在于軟件的正確編制,這里要解決好:① 怎樣確定要讀的數據組;②怎樣控制每次移入8位就讀取一次,若能控制好,顯然3次讀取就能采集24 bit完整信息。解決第一個問題的辦法是將CLK信號同時送移位寄存器和單片機的計數通道,檢測到一段持續的低電平就啟動計數器,計滿24個脈沖后就準備讀取P1口的后24位數值。解決好第一個問題,第二個問題就好解決了,將計數器置成連續裝載值為8的工作方式,每計數8個CLK脈沖就讀取一次數據,在這里只要保證在下一個脈沖到來之前的13μs內取走數據就能保證讀數正確。

圖4 數據采樣程序流程圖

圖5 方案二框圖

5 測量系統硬件原理

5.1 信號轉換部分

將數顯百分表輸出的CLK(1.5 V)和Date(1.5 V)信號接入 LM393雙電壓比較器[10]。當 CLK或Date信號是高電平時(1.5 V),它大于比較器的參考電壓(1 V),比較器就輸出一個5 V高電平信號(因為比較器的電源電壓是5 V);當CLK或Date是低電平時(0 V),小于比較器的參考電壓(1 V),則比較器就輸出一個0 V低電平信號。

5.2 串/并轉換部分及數據采集實施辦法

傳感器的Data信號是一個串行信號,在此先把這個信號輸入到一個串入并出帶鎖存的移位寄存器(74HC595)里。由于一個完整的數據是24 bit的,我們用一個8 bit的串入并出移位寄存器向單片機并行口P1進行傳輸一次讀進來8 bit,并進行鎖存則不影響后面數據的移位,這樣單片機讀3次就將24 bit讀完,既避免了硬件電路的繁瑣和純采用軟件編程實時性差的缺點。

5.3 顯示部分

單片機應用系統最常用的顯示器是發光二極管顯示器(LED)和液晶顯示器(LCD),可顯示數字、字符及系統的狀態。由于LED顯示信息量少,形式比較單一,人機交互性差,而LCD液晶顯示內含有控制驅動器,使得它和單片機的接口電路實現比較簡單,還具有功耗低、體積小、質量輕,超薄和可編程驅動等其他顯示方式無法比擬的優點,故本系統選用1602液晶顯示屏。

6 系統軟件設計

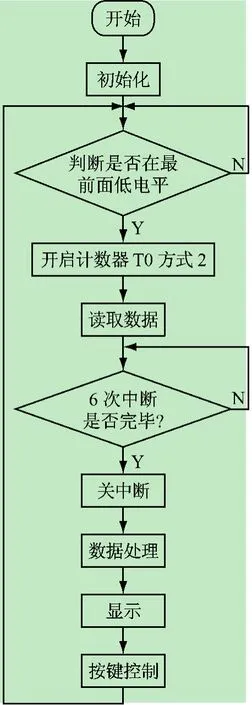

6.1 主程序

主程序流程圖如圖6所示。結合圖1闡述數據采集的具體的實施過程為:首先完成系統的初始化[11-15],其次將經電平轉換后的CLK信號接到單片機的P3.5來檢測CLK電平的變化,當連續檢測到低電平時就用P3.4口進行外部脈沖計數中斷。在此用定時器/計數器0,并將其設定為自動裝載的方式2進行計數,每計數到8中斷一次。由于前24為絕對數據是不需要的,可以讓單片機接收但不用讀出,當前24 bit數據傳輸完(前3次中斷完),后面每次中斷接收到的數據再讀出,三次中斷就可以將全部24位相對數據讀出了。最后采集數據經過單片機處理后將測量結果顯示在LCD液晶顯示屏上。

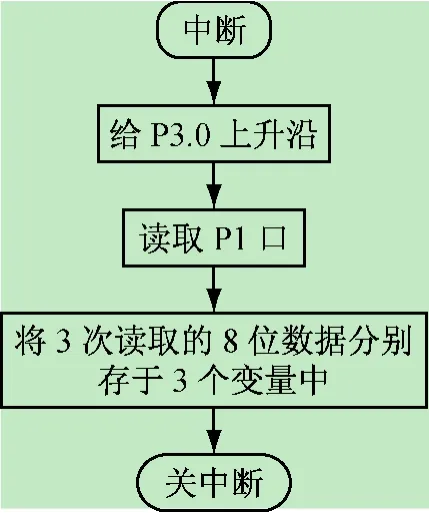

6.2 中斷子程序

中斷子程序流程圖如圖7所示。當定時器/計數器計滿8個時鐘脈沖時就中斷,這時就將進入移位寄存器的8位數據鎖存,鎖存器工作時需要提供一個上升沿鎖存時鐘才能進行鎖存,所以就用軟件給P3.0一個上升沿控制移位寄存器鎖存并行輸出到P1口,然后讀取P1口并將讀完之后的數據另存,以防止后一組數據覆蓋,當3組數據存儲完畢后就關閉中斷。

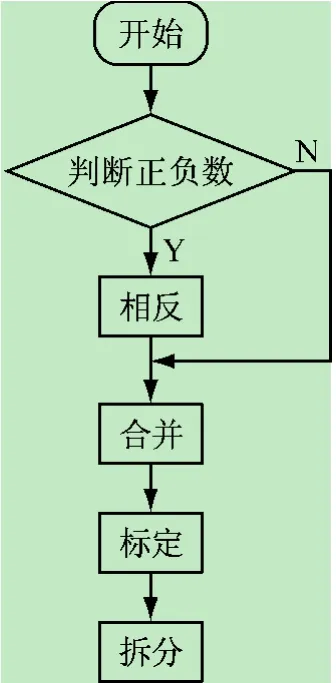

6.3 數據處理子程序

數據處理子程序流程圖如圖8所示。在讀取完之后就進行數據處理,先判斷采集到數據的正負,最高位若為1(正數)則先取反再進行合并;若為0(負數)就直接合并,最后將合并后的數據進行標定然后拆分出各位。

6.4 顯示子程序

圖6 主程序流程圖

圖7 中斷程序流程圖

圖8 數據處理子程序流程圖

常用的數據顯示程序編程較為經典,利用單片機C語言可移植性好的特點,可對其稍加更改直接移植到應用程序當中。

7 硬件設計時注意問題

CLK信號經過比較器后同時送移位寄存器和單片機的計數通道,目的在于移位寄存器能在CLK時鐘控制下進行正確的移位,并在每次中斷后給P3.0口一個上升沿的脈沖作為74HC595的鎖存時鐘,從而將串行信號轉換成并行信號進入單片機;為了讓單片機能直接運算,將74HC595的輸出端的高位(Q7~Q0)接到單片機P1口的低位上(P1.0~ P1.7),避免高低位顛倒,簡化數據處理軟件流程。

8 結語

借助數字示波器分析數顯百分表輸出信號與其顯示數據之間的關系,有助于對容柵式傳感器原理的理解和軟件編程;合理選擇相關硬件搭建電路可有效地保證系統運行穩定性的同時降低成本。文中介紹的數據采集檢測系統是我校機械學院研究生綜合實驗教學內容的一部分,通過該實驗的開設大大提高了學生綜合應用能力和創新精神的培養。目前該測量系統也初步應用于省教育廳科研項目下位機數據采集系統試驗當中。

[1] 王煜東.傳感器應用技術[M].西安:電子科技大學出版社,2006:100-102.

[2] 徐科軍.容柵傳感器的研究與應用[M].北京:清華大學出版社,1995:6-10.

[3] 王習文,齊 欣,宋玉泉.容柵傳感器及其發展前景[J].吉林大學學報(工學版),2003,33(2):89-94.

[4] 楊雪芳,蔡 萍,王衛鋼,等.全數字式容柵位移傳感器[J].儀表技術與傳感器,2005(7):5-6.

[5] Dwight Larson.用于輔助電路分析的示波器數學功能[J].電子設計技術,2012,19(7):40-40,42,44.

[6] 胥京宇.泰克推出專為教育行業而設計的示波器[J].世界電子元器件,2012(5):69-69.

[7] 李佳列,丁國清,顏國正,等.多路電子數顯百分表測量系統的研制[J].儀表技術,2002(1):23-24,26.

[8] 王安敏,王辛立,崔 偉.基于AT89C52單片機的容柵傳感器測距系統[J].儀表技術與傳感器,2008(9):86-90.

[9] 王輝林,李莎莎.基于LabVIEW的數顯百分表測量系統[J].計量技術,2008(6):37-39.

[10] 張國雄.測控電路[M].3版.北京:機械工業出版社,2008:40-78.

[11] 孫永泉,王振清.基于容柵傳感器和單片機的變形檢測系統[J].微計算機信息,2007,23(12-2):103-104.

[12] 陸 雯,王道波.容柵傳感器及其在目標運動轉臺中的應用[J].計算機仿真,2005,22(8):250-252.

[13] 鄔玉亭,李 勇.電容式數顯內徑測微儀[J].工具技術,1995,29(6):46-48.

[14] 胡 超,王 耀.鑒相式位移傳感器的計算機檢測[J].寧波大學學報,1996,9(1):27-28.

[15] 凌銳鴻 王 佶.容柵角度測量裝置的精度分析[J].工具技術,1996,30(4):24-27.