一種基于FPGA的USB3.0 HUB的研究與設計

彭 丹,張勁松,張 特

(1.武漢郵電科學研究院,湖北 武漢 430074;2.武漢群茂科技有限公司,湖北 武漢 430074)

一種基于FPGA的USB3.0 HUB的研究與設計

彭 丹1,2,張勁松1,2,張 特1,2

(1.武漢郵電科學研究院,湖北 武漢 430074;2.武漢群茂科技有限公司,湖北 武漢 430074)

HUB(集線器)是USB體系中不可或缺的一部分,它是USB的最新規范,由英特爾等公司發起。首先介紹了USB3.0 HUB的原理、基本功能和枚舉過程;然后提出USB3.0 HUB的總體設計方案;重點描述了此方案中關鍵模塊的設計和實現;并對該方案進行FPGA仿真與驗證,驗證結果表明該方案的可行性以及它所達到的效果。

USB3.0;集線器;高級加密標準;FPGA

【本文獻信息】彭丹,張勁松,張特.一種基于FPGA的USB3.0 HUB的研究與設計[J].電視技術,2013,37(11).

USB總線是目前最為成功,應用最為廣泛的外設接口。隨著時代的進步和發展,電子產品、手持設備、超大容量的高清視頻設備以及千萬像素的數碼相機等設備的需求越來越高,USB接口規范也需要相應地進行不斷地更新和升級。USB3.0的最高理論速度達到了5 Gbit/s,向需要更大電力支持的設備提供更好的支持和電力供應,它在USB2.0的基礎上增加了新的電源管理功能,采用全雙工數據通信,提供更快的傳輸速度,并且向下兼容USB2.0和USB1.1設備。USB體系主要包括三個部分:主機,設備和物理連接。主機通常是PC或者主機控制器;設備是指常用的U盤、帶USB的攝像頭、相機等設備;物理連接就是通常用的傳輸線,在USB3.0系統中,采用了對偶單純形四線制差分信號線,因此可以支持雙向并發數據流傳輸,這也是USB3.0相比于USB2.0設備速度提升的關鍵因素[1]。

HUB是USB系統中的重要組成部分,且能夠應用在大多數操作系統,它是建立主機與USB設備之間的橋梁。作為一類特殊的USB設備,可以同時將一個接口轉換為多個接口,為用戶提供了效率和便捷。

1 USB3.0 HUB的簡介

1.1 USB3.0 HUB的基本組成

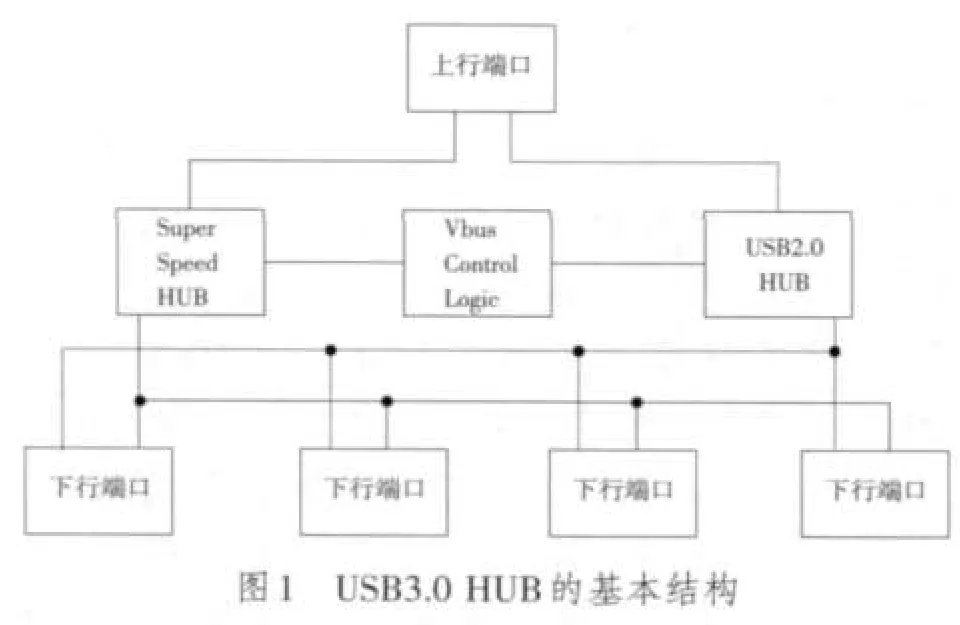

根據最新USB3.0的協議規定,USB3.0 HUB主要由Super Speed HUB,Vbus Control Logic,USB2.0 HUB以及上下行端口組成[2]。由于USB3.0是向下兼容的,所以它有完整的USB2.0HUB設計,而Super Speed HUB部分就是 USB3.0 HUB 區 別 于 USB2.0 HUB 的 主 要 部 分 。USB3.0 HUB基本結構如圖1所示。

1.2 USB3.0集線器的功能

USB3.0 HUB是USB系統中的重要部分,它的基本功能如下:

1)基本連接功能。

2)電源管理功能。USB3.0能夠提供900 mA的電源,這樣就可以給那些連接USB3.0的設備更快更好地完成充電。由于新的接口提供了額外的兩條線,900 mA的電力支持能夠驅動無線適配器,這樣在900 mA的高電力支持下可以擺脫靠線纜連接的必要性。在大量數據傳輸的同時,空閑的設備可以自動進入低功耗狀態,給正在傳輸的設備提供更好更快的性能支持。

3)設備連接和斷開檢測。

4)總線的錯誤檢測和恢復。

5)HUB3.0的自動掛起和恢復功能。

6)向下兼容,下行端口同時支持高/低/全速設備。

2 Super Speed HUB的設計

USB3.0 HUB是一種便攜的低成本的USB3.0擴展接口,它的下行端口面向USB設備,上行端口面向PC主機或者嵌入式主機控制器,速度由上行端口的主機來決定,同時它在下行端口給設備提供連接和斷開的檢測,根據USB3.0最新協議規范,要實現上節所述各項功能設計。Super Speed HUB的整體構架如圖2所示,包括SIE、控制、處理轉換、中繼、路由、AES加解密等部分。

2.1 SIE(Serial Interface Engine)模塊

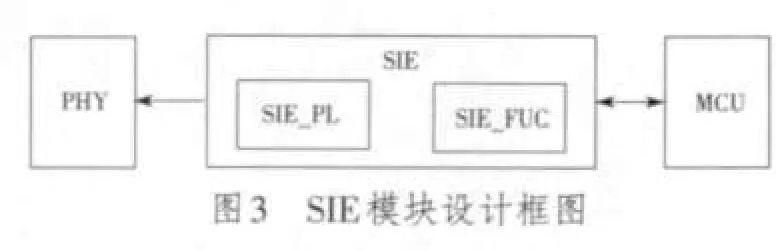

Super Speed HUB中的SIE模塊處理USB規范中物理層和協議層的協議解析,它主要實現包的識別與產生、比特填充和提取、時鐘與數據分離、NRZI編碼和解碼、PID(包標識符)的產生和檢測、CRC校驗碼的識別和產生、地址檢測等。SIE模塊設計中,分為SIE_PL和SIE_FUC兩個部分。SIE_PL模塊負責數據包的解析與組織,PID(包標識符)產生與檢測、CRC校驗識別與產生、地址檢測等。SIE_FUC模塊主要實現SIE模塊與MCU的接口邏輯功能。另外,為了使本系統設計更加穩定,SIE模塊中采用跨時鐘域的設計,一個是本地的48 MHz的全局時鐘,另外一個是USB主機從接收到的數據流中采樣接收的12 MHz數據時鐘(即將48 MHz本地全局時鐘4分頻得到)[3]。SIE模塊設計框圖如圖3所示。

2.2 HUB控制器模塊

HUB控制器主要完成HUB的管理及控制,實現與主機的交互。主機端通過類請求與HUB控制器模塊通信,取得HUB端口的描述符,并且完成USB HUB及其下行端口的管理和控制。主機通過向端點0發送類請求和標準請求來實現HUB的枚舉過程。

2.3 AES模塊

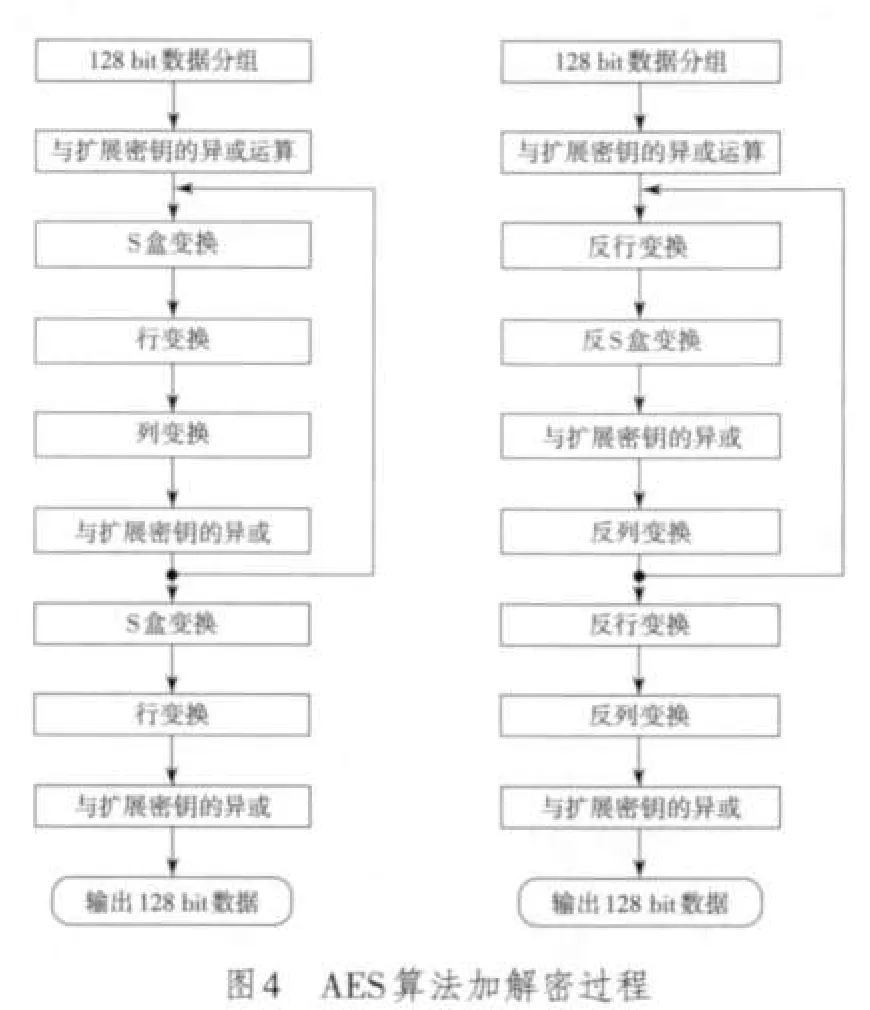

AES是一種基于置換和代替的算法,它實現加解密功能。在USB3.0 Super Speed模式下,根據用戶的需求,當數據從上行端口向下行端口傳輸時,對數據進行加密,以防止信息竊取。同樣,在數據由下行端口向上行端口傳輸時實現其解密過程。AES算法加解密過程如圖4所示。

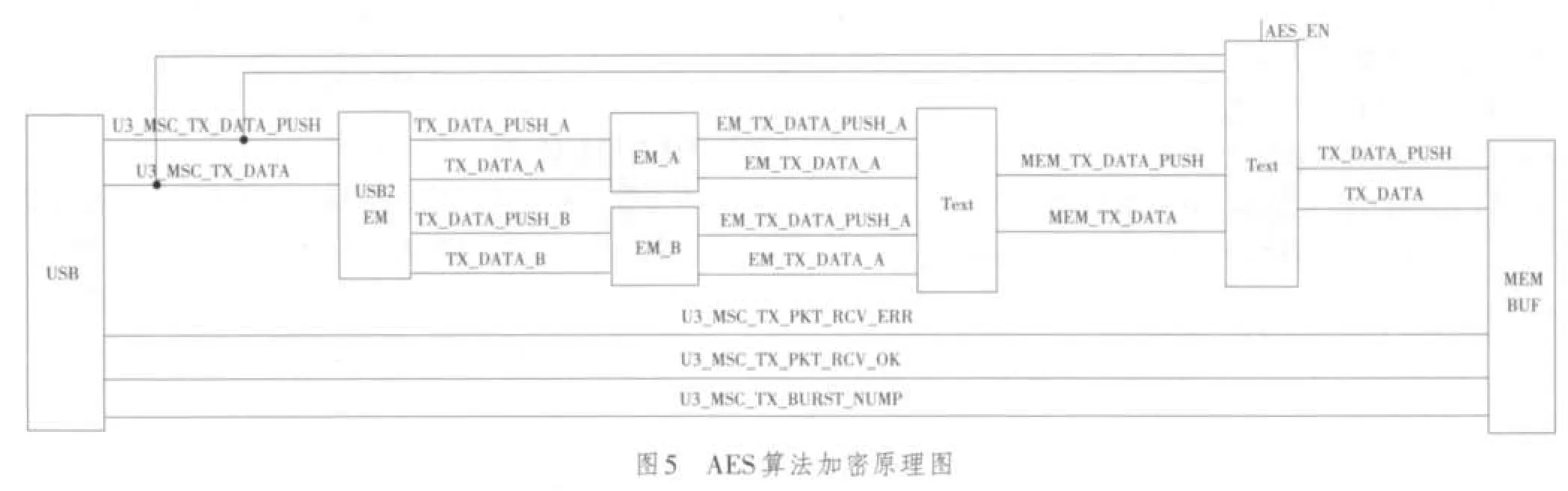

在加解密的過程中,由于USB3.0 HUB的傳輸速度可達到3 200 Mbit/s,但是AES的加解密IP在250 MHz的吞吐率下最高速率只能達到2 400 Mbit/s,因此在加解密的過程中需要2個AES來實現其功能。圖5是USB3.0 AES加密原理圖,從圖中可以看到上行端口會向EM_A發送奇數128 bit數據,向EM_B發送偶數128 bit數據,同時,Mem_buf模塊也會輪詢地從EM_A模塊和EM_B模塊接受數據。而在以前的USB2.0的模式下,數據位寬只有8 bit,全速的帶寬為480 Mbit/s,所以只需要1個AES就可以。

2.4ROUTING模塊

ROUTING模塊即路由邏輯模塊,它的作用是根據連接到下行端口設備的速度來決定將下行端口連接到中繼模塊還是連接到TT模塊。由于在USB3.0 HUB的上行端口中的速度是高速的,而下行端口則不確定為高速、全速或者低速,所以當下行端口設備的速度為高速時,ROUTING模塊連接到中繼模塊,如果下行端口設備的速度為全速或者低速時就連接到TT模塊。

2.5 Repeater中繼模塊

集線器中繼模塊在HUB的數據轉發中起到建立和拆除上行端口和下行端口之間的連接,并且處理集線器的掛起和喚醒的作用。中繼器把上行端口的數據發送到下行端口,把下行端口的數據發送到上行端口,并且要用本地時鐘來從端口上發送和接受數據。它以數據包為單位控制端口的建立和連接以及HUB的喚醒和掛起[4]。如圖6所示為Repeater的連接狀態機。

2.6PHY模塊

PHY模型就是通常所說的USB物理收發器模型[5],它的作用是實現數據的串并轉換。因為在上行端口是并行數據,而在面向設備和電纜中的下行端口是串行數據。

2.7 TT處理轉換器

TT模塊的作用是完成傳輸事務轉發和速度的匹配[6]。當上行端口在高速環境下運行而下行端口在全速或者低速下運行時,TT處理轉換器就是將高速事務轉換成低速事務。由于要滿足速度的匹配,因此TT處理器必須采用緩存的方式來存儲,在緩存的上行端口是一個高速處理器,用來處理高速數據的收發;緩存的下行端口是全速和低速處理器,用來處理全/低速數據的接受和發送。

3 FPGA仿真與驗證

為了更好地完成仿真和驗證,采用Modelsim SE和Navos公司的Debussy軟件。首先搭建仿真環境,包括編譯測試文件、仿真調用文件、引導文件、宏定義文件以及激勵文件。首先將C語言的驅動程序在Linux環境下轉換為二進制的kvout激勵文件,把二進制的kvout文件存儲在外掛的Flash中然后再存儲到內置的RAM中,使其成為發出指令的源頭;同時USB Device的行為級模型也會裝載部分命令以達到仿真的目的。如圖6所示為USB3.0 HUB高速數據批量傳輸仿真結果。

圖6中數據包的總大小為4 096 byte,rst_n為系統復位信號,clk30為主機端12 M時鐘,pci_clk為本地時鐘,cpu_datao是從主機發送出的數據,utm0_data,utm1_data,utm2_data,utm3_data分別為經過USB3.0 HUB擴展后的4路高速信號,Utm_rxready,utm_rxvalid,utm_rxactive分別為端口的控制信號。

為了加強整個設計的可靠性,必須進行FPGA驗證,FPGA驗證選擇的是Altera的StratixII S180開發板,采用QuartusII將RTL級的verilog代碼進行變異并且綜合成網表,然后通過USB-blaster下載線下載到FPGA測試版中,另外激勵文件是在Linux環境下編譯產生的,并且通過EJTAG下載到測試版中。把激勵文件下載到FPGA板子中后,把HUB的上行端口連接到USB的主機,此時如果主機檢查出有USB HUB連接,會產生1個復位信號;在HUB復位后,USB主機向USB Device發送令牌包,并且對HUB進行枚舉,主機識別出該HUB;當主機對USB3.0 HUB成功枚舉后按照USB協議進行數據傳輸。

在傳輸速率上,可以通過USB3.0HUB傳輸1個比較大的文件,并且用ATTO DISK BENCHMARK軟件來測試其讀寫速度,通過ATTO可以顯示出讀取數據可以提高到1 088 Mbit/s,寫入速度可以達到840 Mbit/s(USB2.0 HUB的讀寫速度分別為240 Mbit/s和184 Mbit/s);很顯然這個讀寫速度比USB2.0的提高了5~6倍。當然由于軟件和硬件的各種原因,這個實際的傳輸速度離其理論最大值5 Gbit/s有一定的差距,但已基本實現其高速傳輸的功能。

從verilog的功能仿真、時序仿真和FPGA驗證表明,USB3.0 HUB基本實現了高速數據的傳輸,達到了預期的效果。

4 總結

USB及HUB接口是目前計算機以及微控制器中最常用的通用高速接口,它可以連接串口、U盤、音頻、視頻、手機、相機等絕大多數的外設設備。USB3.0正在以其高速度、高性能、高可靠性、低成本等特點逐漸代替更多的USB2.0產品,成為通信電子市場的主要接口。本文中設計的USB3.0 HUB實現了多媒體數據的高速同步及時傳輸;更佳的電源管理功能以及支持AES加密解密等功能,這些都將促使它在市場上迅速普及。但是USB3.0及其HUB依舊有自己的瓶頸,比如在某些應用中需要盡可能高的吞吐量時,線纜的長度會受到限制;同時電纜的材質以及信號的質量也會在整體上影響傳輸的效果,所以在傳輸百兆以上數據流時,所用線纜最好不要超過3 m。

:

[1] 黃輝.USB3.0技術發展和展望[J].大眾硬件,2008(10):37-140.

[2] 范垂榮.USB集線器設計與開發[J].大眾科技,2005(11):145-148.

[3] 占揚林.基于FPGA的USB3.0 HUB的設計與實現[D].北京:北方工業大學,2011.

[4] 胡錦,胡立琴,陳訓亮.一種嵌入式USB2.0主機控制器IP核的研究與設計[J].微電子學與計算機,2009,26(1):133-137.

[5] ENGBRETSON M.USB3.0 physical layer measurements[J].Evaluation Engineering,2009,48(1):14-19.

[6] The Fujitsu USB 3.0-SATA Bridge IC Earns USB-IF Compliance Certification for SuperSpeed USB[EB/OL].[2012-09-01].http://www.fujitsu.com/us/news/pr/fma_20100106-1.html .

Resarch and Design of USB3.0 HUB Based on FPGA

PENG Dan1,2,ZHANG Jinsong1,2,ZHANG Te1,2

(1.Wuhan Research Institute of Post&Telecommunication,Wuhan 430074,China;2.Wuhan Trimode Technology,Wuhan 430074,China)

HUB is an integral part of the USB system,USB3.0 is the latest USB specification,initiated by Intel and other companies.USB3.0 HUB principles,basic functions and enumeration process are introuduced in this paper.And the overall design of the USB3.0 HUB is proposed.The design and implementation of key modules of this program are described.The results of FPGA simulation and verification demonstrate the feasibility of the program.

USB3.0;HUB;AES;FPGA

TP303

A

彭 丹(1984—)女,碩士生,主研IC設計;

張勁松(1970—)博士,碩士生導師,主要從事通信終端設計研究;

張 特(1987—)碩士生,主研光模塊設計。

責任編輯:魏雨博

2012-10-08