基于LEON3的SoC平臺搭建與流水燈控制驗證

陳榮軍,劉松勁,譚洪舟,丁顏玉

(1.中山大學 南方學院,廣東 廣州 510197;2.中山大學 信息科學與技術(shù)學院,廣東 廣州 510006;3.廣州市加信電子技術(shù)有限公司,廣東 廣州 510663)

當前芯片設計業(yè)正面臨著一系列的挑戰(zhàn),系統(tǒng)芯片SoC已經(jīng)成為IC設計業(yè)界的焦點,SoC性能越來越強,規(guī)模越來越大。LEON是Gaisler Research公司研發(fā)的基于SPARC V8(IEEE-1754)架構(gòu)的開源處理器IP核。它的源碼為可綜合的VHDL代碼,并且是開源的,符合SPARC標準。LEON系列處理器主要包括 3 款:LEON1,LEON2,LEON3。 目前,LEON3 憑著其諸多優(yōu)勢在FPGA和ASIC上有著巨大的應用場景[1]。相比傳統(tǒng)的處理器IP核,LEON3配置靈活,成本低,性能高,更適宜SoC平臺開發(fā),文中為基于LEON3的SoC平臺設計提供一個良好的參考方案。

1 主流免費處理器IP核

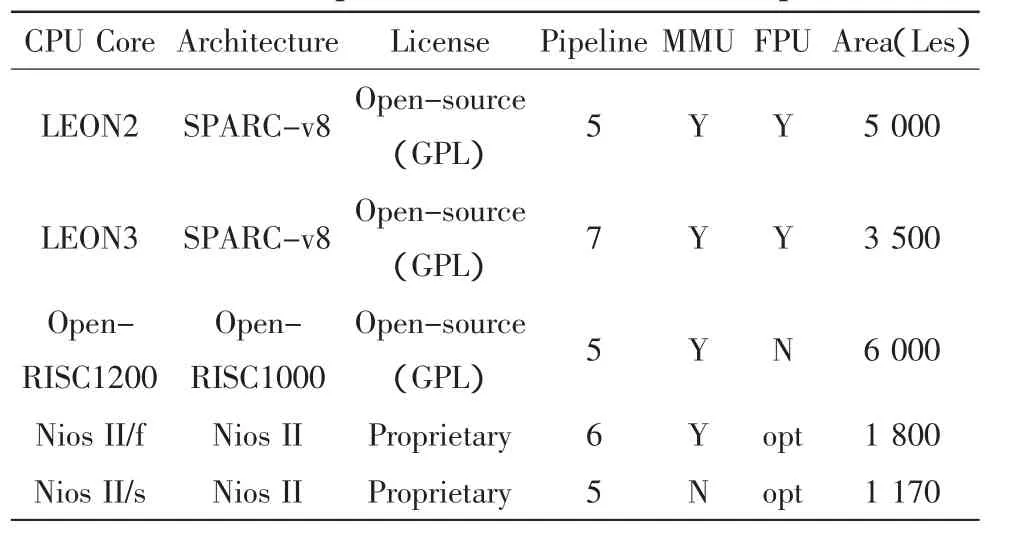

目前開放性源碼已經(jīng)從軟件 (Linux、GCC等)擴展到硬件,對于嵌入式軟核處理器來說,出現(xiàn)了像OpenCores這樣專門發(fā)布免費的IP核源代碼的組織。目前,免費的32位嵌入式軟核處理器有:Gaisler Research公司的 LEON2/LEON3、OpenCores組織公布的OR1200和Altera公司的Nios II。這3種開放性處理器憑借其高性能,低成本,良好的可配置型和完善的開發(fā)環(huán)境,受到了學術(shù)界和工業(yè)界的普遍重視[2],表1對這3種軟核進行比較[3]。

表1 主流32位免費處理器比較Tab.1 Comparison of mainstream 32 free processor

由表1可以看到,對比OR1200和Nios II,LEON3擁有7級流水線,指令周期短,內(nèi)存管理單元(MMU)和浮點運算單元(FPU)等,性能優(yōu)越。此外它還是開源代碼,配置、移植靈活,占用資源比較少,綜合考慮,可以看出LEON3相比其他處理器IP核,有著明顯優(yōu)勢。

2 基于LEON3的SoC平臺的搭建

2.1 系統(tǒng)設計框架

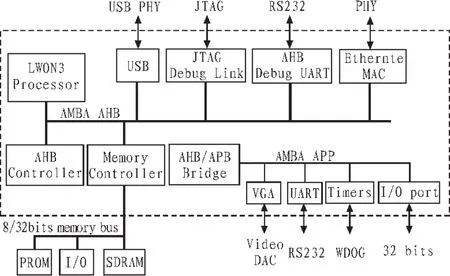

LEON3內(nèi)部包含7級整數(shù)流水線。支持硬件乘/除法器以及分立的指令與數(shù)據(jù)緩存(Harvard結(jié)構(gòu))。LEON3通過高速的AMBA AHB總線連接內(nèi)存控制器、USB接口、JTAG接口等高速外部接口,低速的AMBA APB總線實現(xiàn)片上外設的接口,如定時器、串口、VGA等[4]。其系統(tǒng)框圖如圖1所示。

圖1 系統(tǒng)框圖Fig.1 System block diagram

2.2 系統(tǒng)設計方法

2.2.1 系統(tǒng)開發(fā)環(huán)境

確定LEON3平臺系統(tǒng)框架后,接下來配置硬件平臺搭建環(huán)境,其開發(fā)環(huán)境如下:

1)硬件條件 使用開發(fā)板:DE2-115,F(xiàn)PGA芯片為:Cyclone II, EP2C70, Altera Inc.

2)軟件條件 在 win 7系統(tǒng)安裝虛擬機:VMware 7.0,然后再虛擬機上安裝Linux系統(tǒng):Red Hat Enterprise Linux 5。在linux環(huán)境下進行硬件配置。安裝grmon2-eval,用其下載硬件sof文件,查看硬件信息。

2.2.2 硬件平臺搭建步驟

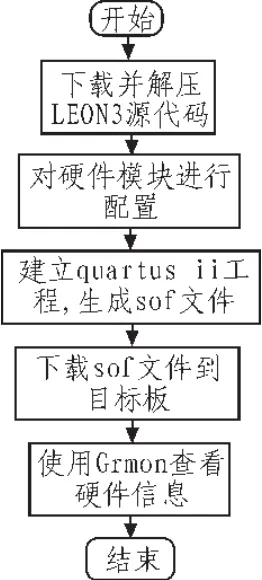

在配置好硬件平臺開發(fā)環(huán)境后,接下來按照步驟進行平臺搭建,其流程圖如圖2所示。

圖2 硬件平臺搭建步驟Fig.2 Procedure of designing hardware platform

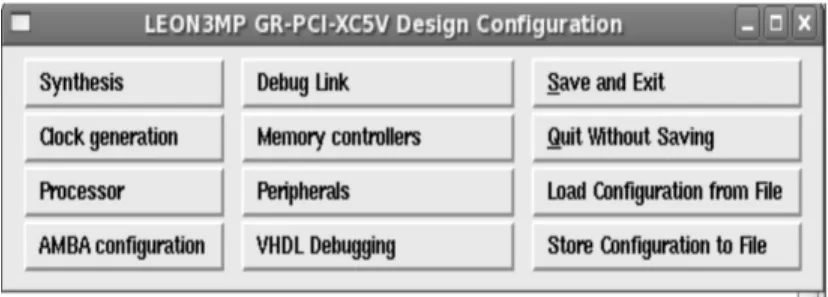

在Gaisler Research官網(wǎng)上下載LEON3源代碼,然后解壓,在Linux環(huán)境下,找到目標板的文件目錄,使用命令make xconfig進行各個硬件模塊的配置,界面如圖3所示,配置信息會寫入config.vhd文件中[5]。

圖3 LEON3配置界面Fig.3 Configuration interface of LEON3

然后使用命令make quartus建立工程(PC機上需要預先安裝quartus ii這個軟件),使用軟件quartus ii編譯整個工程生成sof文件,最后把sof文件下載到FPGA開發(fā)板。

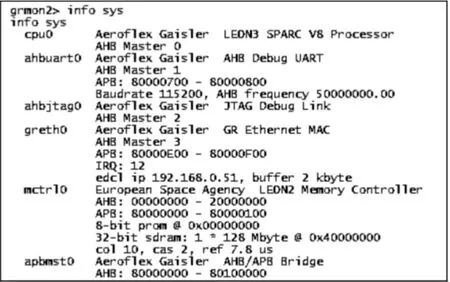

安裝軟件GRMON并打開,使用命令info sys,可以看到LEON3內(nèi)核的硬件地址信息,如圖4所示,說明LEON 3硬件平臺搭建完成。

圖4 LEON3硬件地址信息Fig.4 Hardware address information of LEON3

3 基于LEON3的SOC平臺流水燈控制驗證

在搭建好LEON3硬件平臺后,我們在windows平臺,編寫流水燈程序,使用sparc-elf-3.4.4-mingw進行編譯[6],再用grmon2-eval下載到FPGA目標板,使用命令go,運行程序,可以看到LED燈依次閃爍,說明驗證成功。

3.1 硬件平臺驗證環(huán)境

1)硬件條件

① 開發(fā)板:DE2-115

② FPGA:Cyclone II,EP2C70,Altera Inc.

2)軟件條件

①Cygwin

②sparc-elf-3.4.4-mingw

③grmon2-eval

3.2 編寫流水燈程序

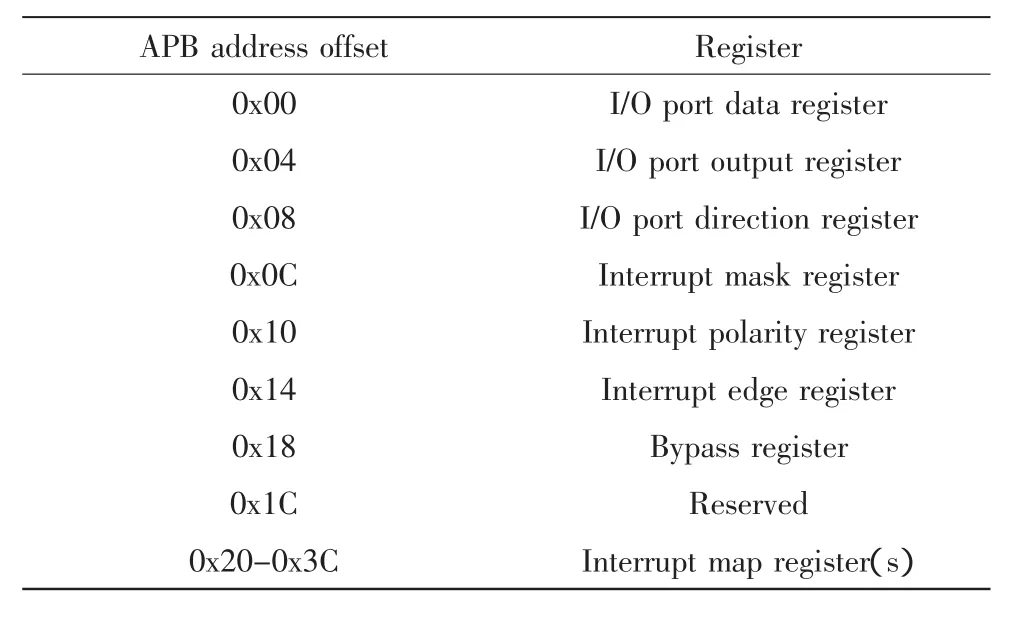

使用grmon2-eval得到的LEON3各個模塊以及PIO的地址信息,編寫流水燈程序。LEON3的PIO偏移地址信息如表2所示。

表2 PIO偏移地址信息Tab.2 Offset address information of PIO

硬件地址信息映射PIO部分代碼:

3.3 編譯并下載流水燈程序

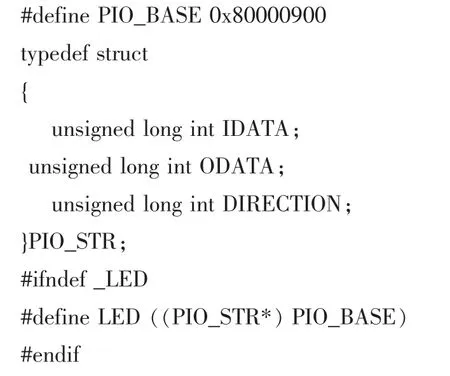

安裝sparc-elf-gcc,使用命令:sparc-elf-gcc-g-O2 LED.co LED-msoft-float編譯代碼LED.c生成可執(zhí)行程序LED。

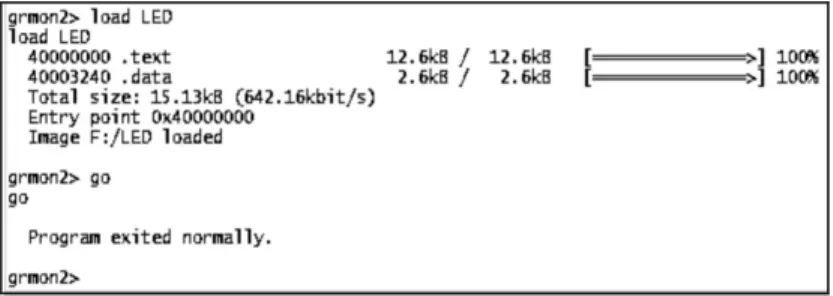

打開軟件GRMON,使用命令:load LED把可執(zhí)行程序LED下載到目標系統(tǒng)。最后使用命令:go,運行程序,如圖5所示。

圖5 下載并運行程序Fig.5 Download and run the program

運行程序后,如圖6所示,可以觀察到測試平臺上8盞LED燈依次閃爍,SOC平臺驗證成功。

4 結(jié)束語

LEON3處理器以其高性能,低成本和配置靈活等優(yōu)勢在SoC應用上有著廣泛的應用。本文使用開源的硬件代碼,提出了一個比較詳細的基于LEON3平臺的精簡的,靈活的SoC平臺開發(fā)流程,并編寫流水燈程序,驗證平臺搭建成功,為LEON3開發(fā)提供了很好的參考[7]。

圖6 LED燈Fig.6 LED lights

[1]LUO Pei,ZHANG Jian.A high reliable SOC on-board computer based on Leon3[C]//IEEE International Conference on Computer Science and Automation Engineering (CSAE),2012.

[2]徐敏,孫愷.開源軟核處理器OpenRisc的SOPC設計[M].北京:北京航空航天大學出版社,2008.

[3]1-CODE TECHNOLOGIES.Soft CPU Cores for FPGA.1-CODE TECHNOLOGIES.[EB/OL].(2012).http://www.1-core.com/library/digital/soft-cpu-cores/

[4]LI Xue-mei,HOU Li-gang.The FPGA prototyping implementation of LEON3 SoC[C]//IEEE Conference Publications on Industrial Control and Electronics Engineering (ICICEE),2012.

[5]ZHOU Zhong-hua,WU Wu-chen.A SoPC design based on LEON3 SoC platform [C]//1st Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics,2009.

[6]李林,張曉林,楊希.基于LEON開源軟核的SoC平臺構(gòu)建與測試[J].單片機與嵌入系統(tǒng)用,2007(1):32-35.

LI Lin,ZHANG Xiao-lin,YANG Xi.Construction and testing of SoC platform based on the LEON open source soft-core[J].Microcontroller and Embedded Systems Applications,2007.

[7]熊來紅,高健,汪皓鈺.COM技術(shù)和遺傳算法在無功優(yōu)化軟件開發(fā)中的應用[J].陜西電力,2011(12):22-26,75.

XIONG Lai-hong,GAO Jian,WANG Hao-yu.Application of com technology and genetic algorithms in power reactive optimization software design[J].Shaanxi Electric Power,2011(12):22-26,75.