多通道高速ADC電路PCB設計技術淺談

李軍輝 簡育華 袁子喬

(西安電子工程研究所 西安 710100)

0 引言

隨著芯片技術的不斷發展,ADC的采樣頻率已經從以前的MHz發展到當前的GHz。伴隨著ADC采樣頻率的不斷提高,ADC的模擬輸入信號頻率和帶寬也在不斷提高,從視頻信號到現在的中頻甚至射頻信號。因此,用于低速ADC采樣電路的一些設計方法已經不適用于高速ADC的采樣電路[3]。如何在高速ADC采樣電路設計中提高ADC模擬輸入信號各通道之間的隔離度變得尤為關鍵,對于數字地平面和模擬地平面的處理方式也非常關鍵。

對于高速ADC而言,模擬通道PCB上的每個過孔和走線都通過空間、電源平面和地平面對外進行電磁波的輻射;另一方面,由于高速ADC芯片的帶寬都在GHz,它不僅容易受到其它通道模擬信號的干擾,也容易受到系統內或外界高速數字信號的電磁干擾。所以,在多通道高速ADC電路的設計中,首要的問題就是解決多通道之間的互耦問題,這其中就主要是解決模擬部分地平面的傳導耦合以及各通道之間的輻射干擾問題。其次,還得解決外界和系統內數字部分對模擬輸入信號的輻射干擾。

下面就以E2V公司的EV10AQ190這款芯片為例,先介紹一下此款芯片的主要特點,然后分別從模擬輸入信號的處理,模擬電源、數字電源、數字和模擬地平面的隔離,數字輸出信號的處理以及采樣時鐘的處理四個方面進行討論[1],最后給出一個應用的實例。

1 EV10AQ190介紹

EV10AQ190是英國E2V公司的一款低功耗的高速ADC,其主要特點如下:

·四通道、10位分辨率的ADC,使用了e2v單

核技術;

四通道、1.25GHz的采樣率;

兩通道、2.5GHz的采樣率;

單通道、5GHz采樣率;

內置四通道高速交錯采樣電路;

·單個2.5GHz差分輸入采樣時鐘;

·500mVpp的模擬輸入信號(交流或直流耦合方式);

·高達3.2GHz的輸入信號帶寬;

·通道間的隔離度大于60dB;

·DDR-LVDS數據輸出方式;

·SPI配置接口;

·3.3V模擬電源和1.8V的數字電源;

·每通道1.4W功耗。

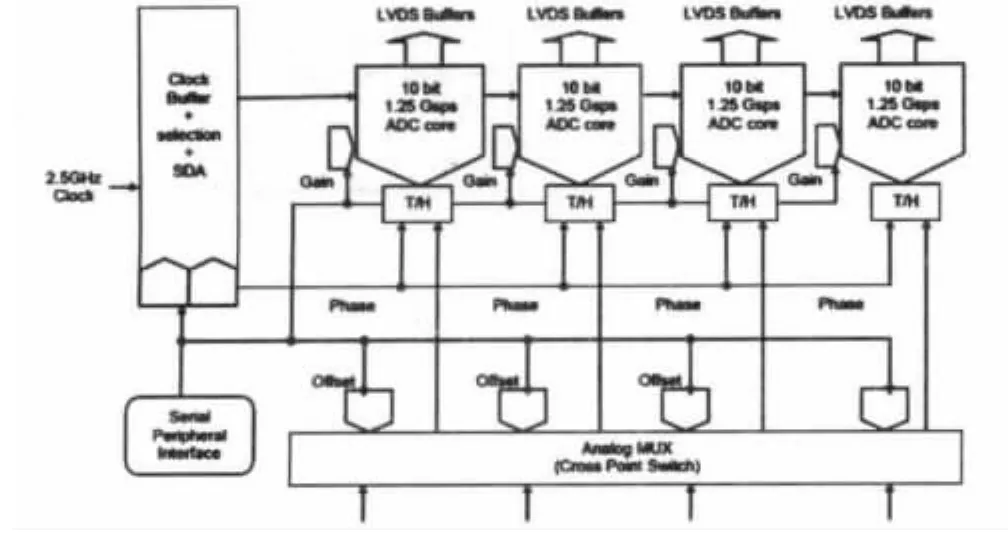

其內部結構如圖1所示。

圖1 EV10AQ190內部結構圖

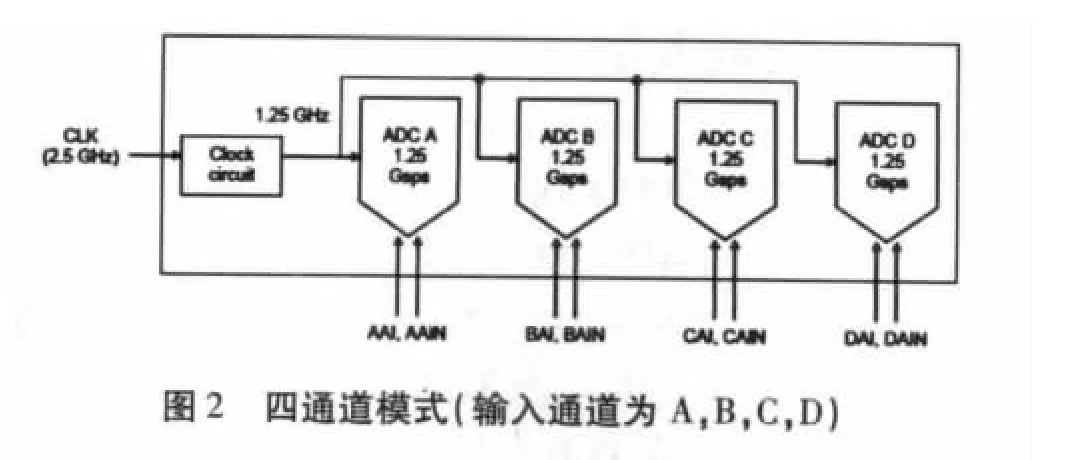

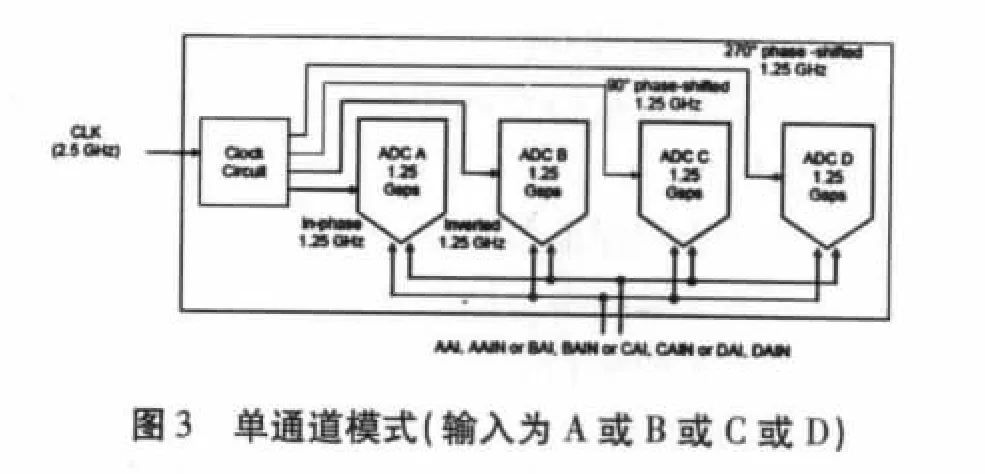

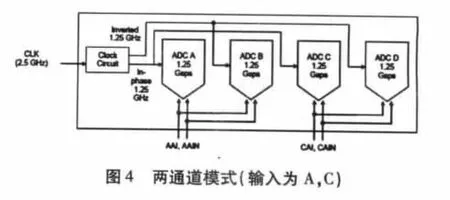

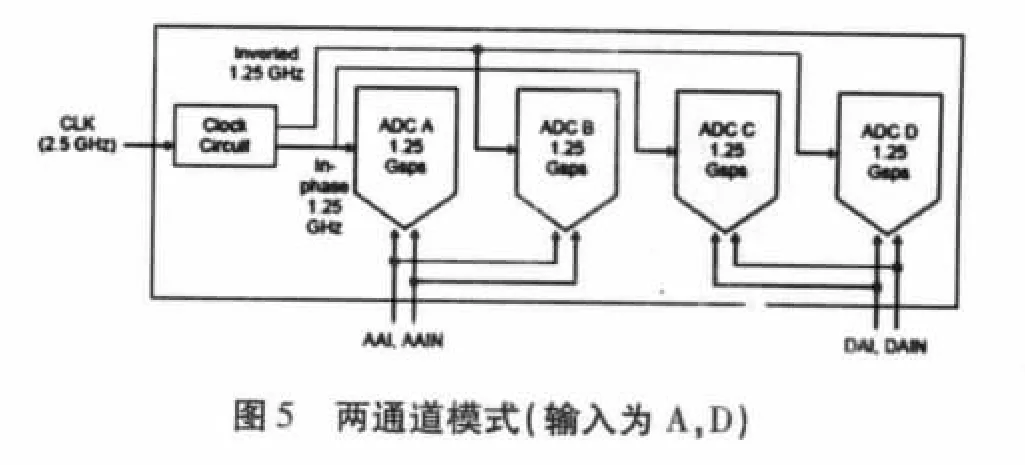

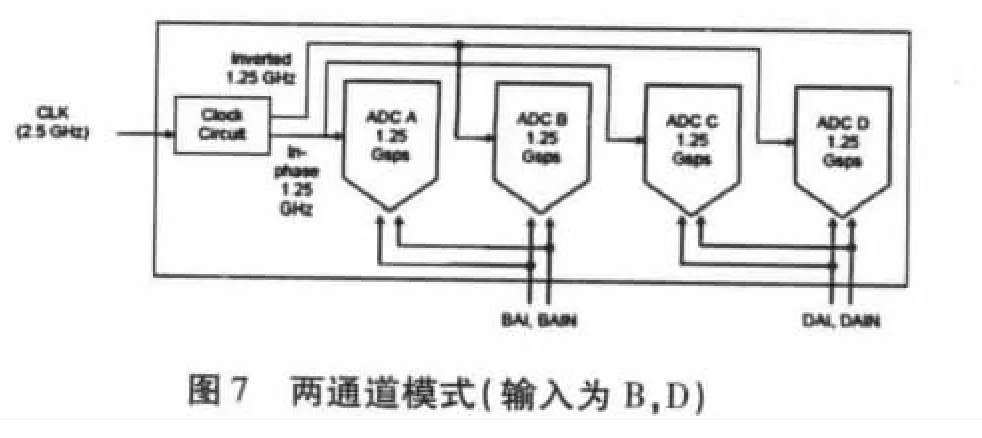

通過SPI口,它可以靈活的配置為四通道1.25GHz采樣率,或者兩通道2.5GHz采樣率,或者單通道5GHz采樣率的ADC,不同的配置模式見圖2~7。

2 模擬輸入信號的處理

前端接收機對天線接收到的微弱信號進行多級放大后輸出到ADC,ADC前端采用與ADC相匹配帶寬的射頻變壓器將單端模擬信號轉換為差分信號后直接輸入到ADC。為了保證多路模擬輸入信號之間的隔離度,在PCB布局時就要對模擬信號的走線方式和布局等方面進行多重考慮:

a.在允許的布局空間內盡可能擴大各模擬通道之間的距離;

b.盡可能的保證各通道模擬信號走線的等長;

c.電源盡量遠離模擬信號的走線;

d.對整個模擬信號所在區域以及各模擬信號之間加以屏蔽處理;

e.模擬信號盡量在TOP層走線,以減少模擬信號線的過孔數量;

為了盡量降低模擬信號的空間輻射,提高通道間的隔離度,需要在模擬信號走線周圍鋪設地平面。

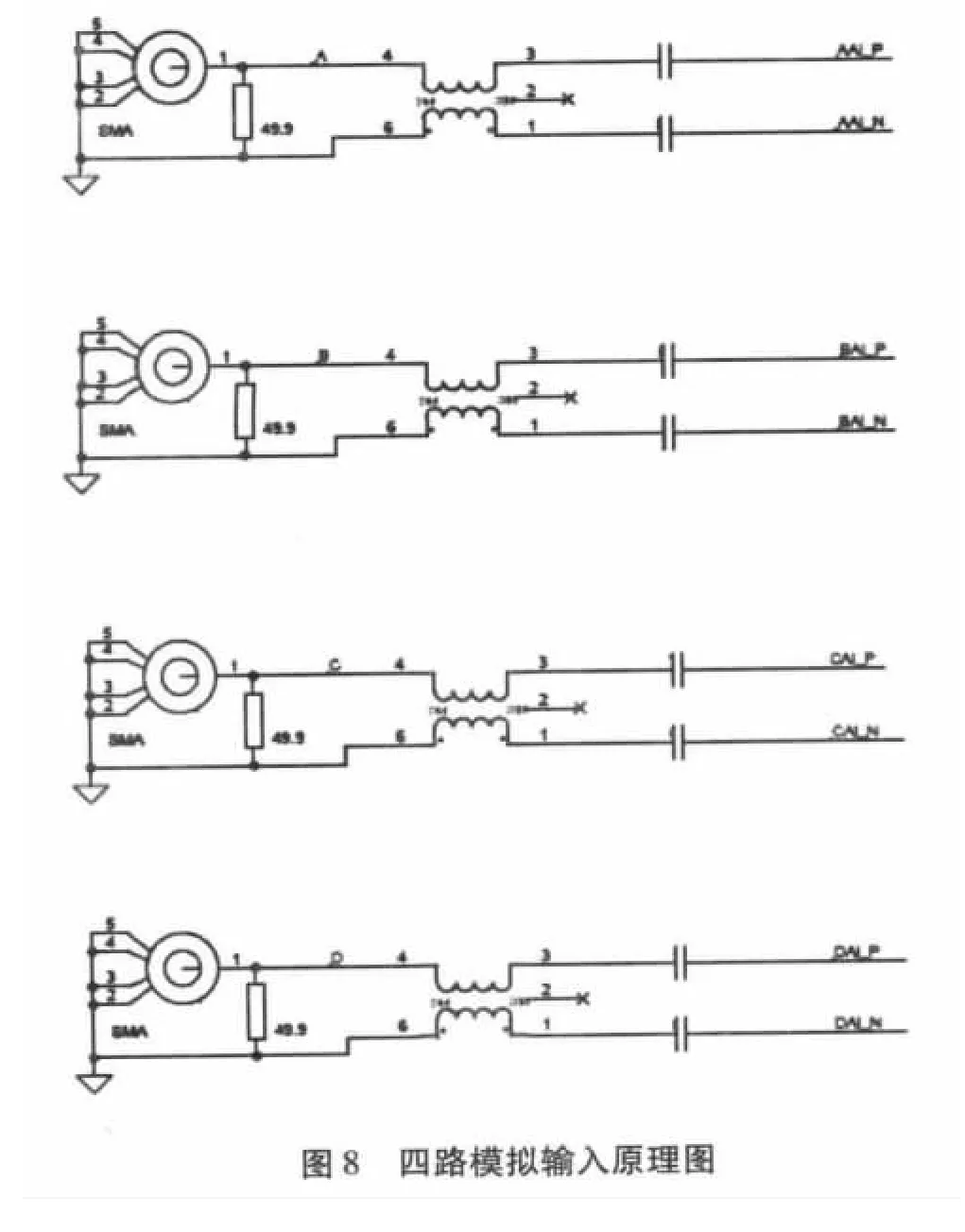

EV10AQ190的輸入信號帶寬達到了3.2GHz,因此在ADC輸入的前端選擇變壓器的帶寬范圍為4.5MHz~3GHz。通過變壓器將單端模擬輸入信號轉換為差分信號后送給ADC的輸入端,原理圖設計和PCB的布局見圖8和圖9。

圖9 模擬輸入信號布局

3 模擬電源、地和數字電源、地的處理

模擬電源、地和數字電源、地的處理在高速ADC的PCB設計中至關重要[1]。在高速混合信號處理的電路設計中,必然存在模擬電源和數字電源。但隨著高密度、高復雜系統需求的不斷發展,PCB板的供電方式已經由模擬和數字電源分別供電的方式轉變為單獨的數字供電方式[4]。

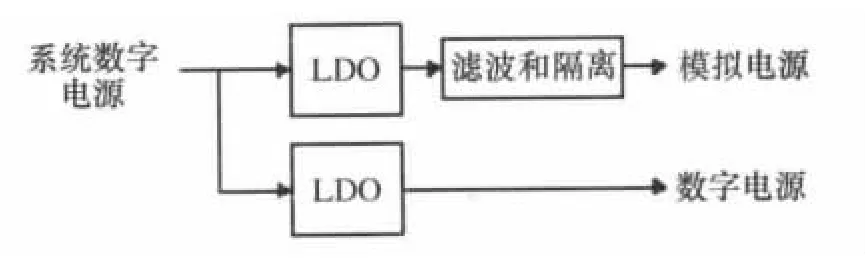

EV10AQ190的電源有兩種:模擬電源3.3V和數字電源1.8V。模擬電源3.3V采用了線性電源芯片(LDO)從數字電源取電,再經過電容濾波和磁珠的隔離后給ADC的模擬電源供電。同時為了提高ADC芯片的性能,ADC的數字電源1.8V也采用了線性電源供電的方式,從系統的數字電源取電后直接供電,如圖10所示。此外,還需對模擬電源和數字電源進行良好的去耦處理,靠近模擬電源和數字電源的管腳附近都需要放置適量的去耦電容。

圖10 電源供電方式

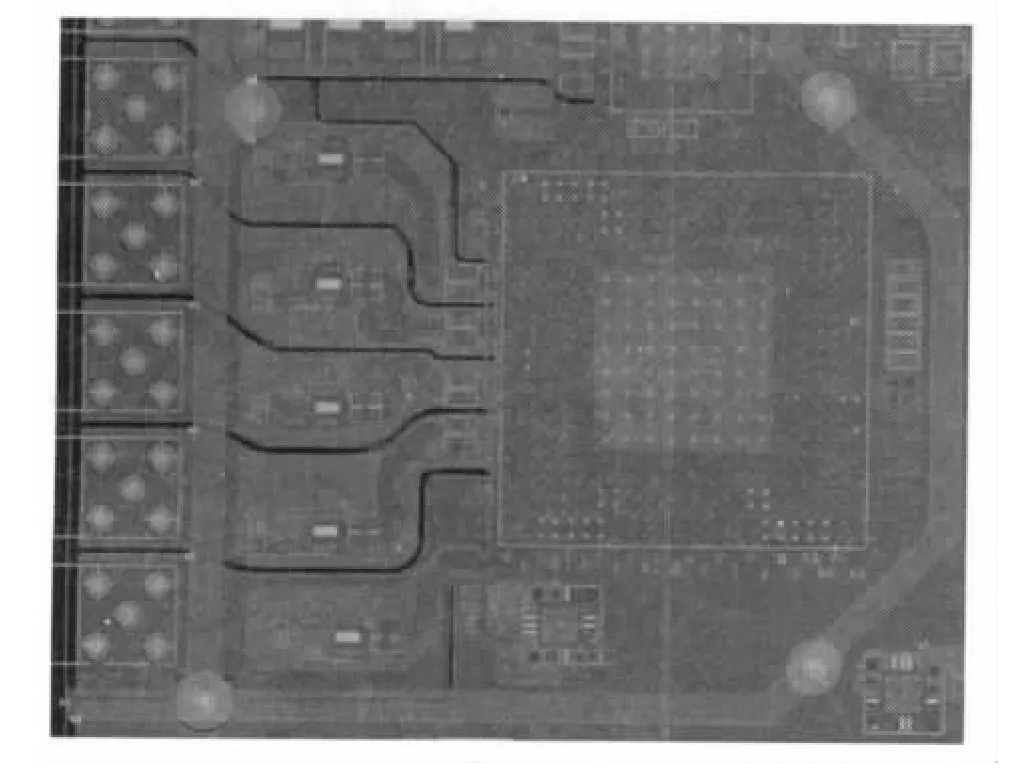

隨著芯片技術的不斷發展,在高速ADC芯片中,已經沒有模擬地與數字地管腳的區分。因此在高速ADC的采樣電路中,不再像以前那樣進行模擬地和數字地的分割,一般采用統一的地平面,這樣可以較好的保證信號阻抗的連續性和信號回流路徑的完整性。為了保證ADC輸入模擬信號通道之間的隔離度,防止模擬信號經過地平面進行傳導干擾,對模擬輸入部分的地平面進行了強行分割處理,使得每個模擬通道的參考地平面在模擬走線下方分開,最后在ADC芯片下方與系統的地平面連接。經過測試,這種分割方法能夠有效降低模擬信號之間通過地平面的傳導干擾。同時將模擬走線層上的鋪地區域通過過孔與下面的地平面連接,吸收模擬信號的空間輻射。EV10AQ190前端模擬部分地平面的分割見圖11。

圖11 模擬部分地平面分割示意圖

4 對ADC輸出信號的處理

對于高速ADC而言,輸出信號的速率一般都達到了Gbps。為了能夠將數字信號穩定可靠地傳輸到后端處理芯片,保證輸出信號阻抗的完整性至關重要[5]。此時,PCB的疊層一般選擇“電源層-信號層-地層”的順序,這樣對于復雜的PCB板,至少可以保證信號有一個完整的地平面作為參考平面,從而保證信號線阻抗的完整性。在四通道1.25GHz采樣率下,EV10AQ190每個通道輸出信號的速率為1.25Gbps,輸出信號的時鐘為625MHz。即使電源平面因為模擬電源和數字電源而進行分割,但因為地平面為一個完整的平面,因此輸出信號阻抗的完整也是有保證的。

5 采樣時鐘的處理

采樣時鐘的相位噪聲會引起系統信噪比的降低。它的抖動將對輸入信號進行調制并抬高噪聲和失真電平,所以必須采用低相位噪聲和抖動的時鐘芯片作為ADC的時鐘源。在采樣系統中采樣時鐘既與模擬信號一樣易于被噪聲感染,也與數字信號一樣易引起噪聲,因此必須同時把它與模擬和數字系統相隔離。然而,受系統所限這通常不容易實現[1]。

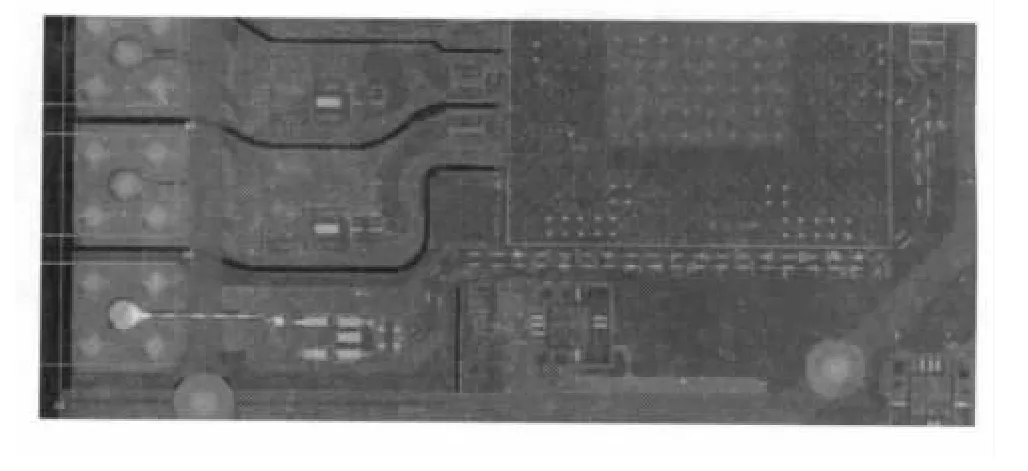

在許多情況下,高速ADC的采樣時鐘都由系統的頻綜模塊產生后直接送出,經過變壓器隔離后轉換成差分信號輸入給ADC。由于頻綜產生的是模擬正弦時鐘,極易受到干擾,因此在變壓器前端的單端時鐘PCB走線要盡可能短,而經過變壓器后的差分時鐘信號線的抗干擾能力較強,所以變壓器一般選擇盡量靠近時鐘的輸入端放置。同時為了減少時鐘信號線與模擬信號線之間的干擾,將它們之間的地平面進行分割以及在它們的走線層上鋪設地平面是很有必要的,見圖12所示。

圖12 時鐘走線與模擬走線的處理圖

6 設計實例

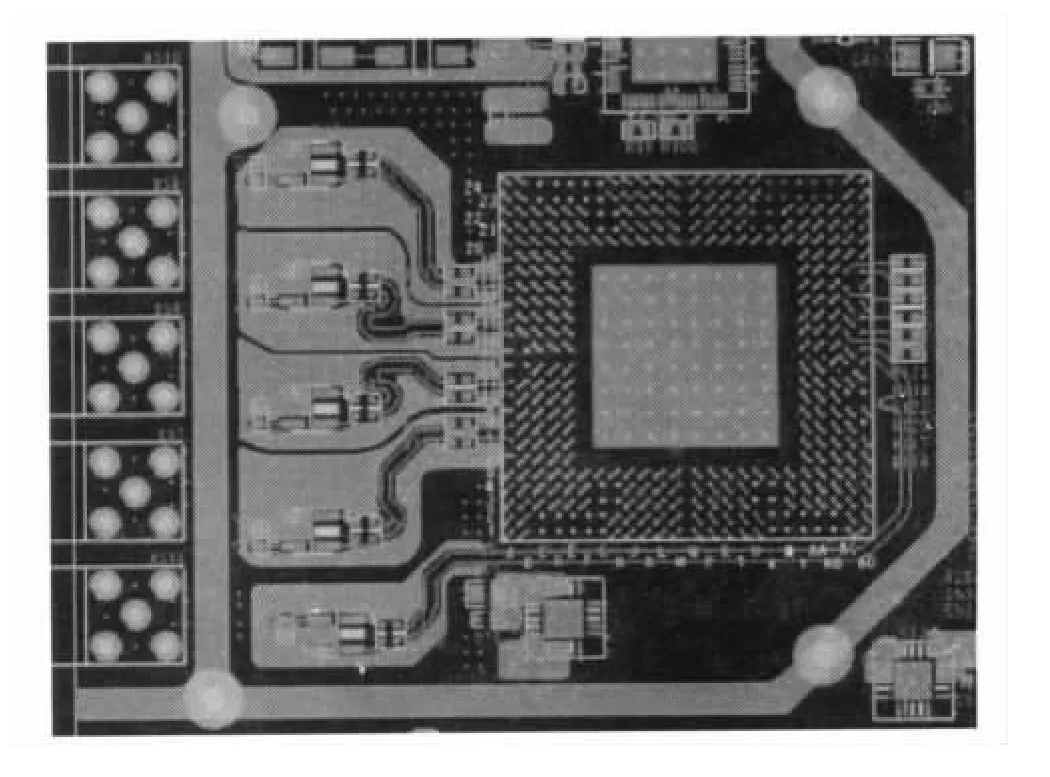

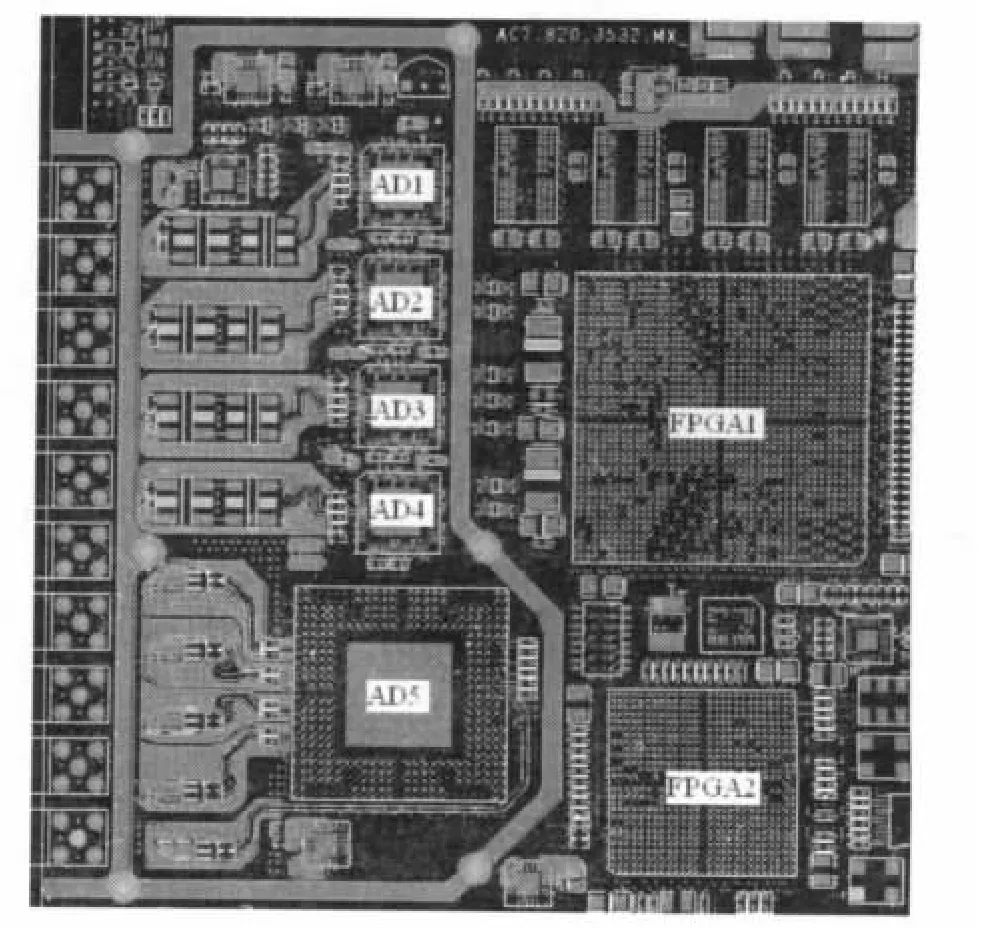

如圖13所示,是一個包含5個高速采樣ADC的高速數模混合處理板的PCB部分截圖。

圖13 設計實例

AD1-AD4是四通道獨立采樣的高速ADC;AD5為高速ADC(EV10AQ190);FPGA1用來接收AD1-AD5的數據并進行處理,FPGA2完成對AD1-AD5的SPI配置。從圖中可以看出,ADC前端都采用了變壓器方式將輸入的單端模擬信號轉變為差分信號后送給ADC。AD1-AD4的時鐘由外部提供,經過一個時鐘緩沖器后分別給它們提供時鐘,AD5的時鐘也由外部提供,經過變壓器后直接送給了AD5。

在圖中可以看出,5路ADC的電源都由線性電源分別進行供電,并在它們之間用磁珠進行了隔離處理;模擬輸入部分和時鐘在其布線層都鋪設了隔離的地平面,并對它們之間的地平面進行了分割,這樣盡可能地提高了ADC各路之間的隔離度。在整個ADC所在的區域周圍鋪設了屏蔽罩,降低了ADC受到附近高速數字信號的干擾。

7 結論

在多通道高速ADC采樣的數模混合PCB電路設計中,通過對模擬電路與數字電路進行合理的布局,減少數字電路對模擬電路的干擾;同時對模擬部分的電路進行合理的分割設計,降低模擬信號通道之間的互耦干擾,一定能夠設計出滿足指標要求的電路系統。

[1]陳慧青,江樺等.高速ADC電路的電磁兼容設計[C].第十六屆電工理論學術年會論文集,22004,(7):93-96.

[2]呂文紅,郭銀景,唐富華等.電磁兼容原理及應用教程[M].北京:清華大學出版社,2009-08.

[3]Howard Johnson,Martin Graham.High-Speed Digital Design[M].北京:北京工業出版社,2012.

[4]錢振宇,史建華等.開關電源的電磁兼容性設計,測試和典型案例[M].北京:電子工業出版社,2011-07.

[5]Howard Johnson,Martin Graham.High-Speed Signal Propagation[M].北京:北京工業出版社,2012.