高速核心板的SI仿真與改進*

蘇瑞祥 陳少昌 李 超

(1.青島航保修理廠 青島 266071)(2.海軍工程大學電子工程學院 武漢 430033)

1 引言

SI全稱Signal Integrity信號完整性,指的是電路系統中信號的質量及信號在傳輸后仍保持正確的功能特性。主要包括以下幾個問題:

1)延遲[1]:在以往的低速板中,信號在傳輸線上的傳輸時間可以忽略,但是對于高速電路板,不能忽略。信號在線上的傳輸時間產生延遲,會導致數字電路的邏輯產生錯誤,引起時序問題。延遲主要取決于線長和介質的介電常數。

2)反射[2]:信號在PCB板上傳輸時遇到阻抗不連續就會發生反射、如過孔、拐角、走線寬度的突變、源端/負載端阻抗不匹配等。有一部分信號被反射回源端,會造成工作效率降低,向外輻射電磁波,影響信號傳輸從而導致失真。

3)信號振蕩[3]:由阻抗不連續產生反射。從負載端返回源端的信號由于源端的阻抗也不匹配在源端又產生反射,從而導致信號在傳輸線上來回傳播。振蕩會產生EMI問題。

4)串擾[4]:隨著PCB向高密度發展,一塊板上集成了越來越多的器件,線路也趨向復雜。信號線由于互感互容引起信號能量耦合到另一條信號線上的現象稱為串擾。它會造成信號的失真,數字電路的誤觸發,甚至會引起器件管腳的損壞。串擾的分析與抑制是一項復雜的工作。

由于振蕩究其原因還是由信號的反射引起的,并且延遲是信號的時域問題,本文都不做討論。本文從串擾和反射入手,提出對S3C2410型核心板的信號完整性分析和改進并給出具體流程與方法。

整板的信號完整性分析應該包括以下幾個部分:確定關鍵網絡(關鍵信號),進行反射和串擾仿真,提出改進辦法,驗證改進結果。

2 確定關鍵網絡

目前的高速PCB板元器件眾多,連線網絡復雜。若要每個器件每根連線都進行仿真則工作量太大。選擇出易受干擾的和易產生干擾會影響系統工作的關鍵網絡來進行分析[5],這樣不僅能夠降低工作量,還能有效地找出線路的信號完整性問題。找出關鍵網絡的方法有兩種:

1)根據理論知識。一般在高速PCB上容易產生干擾的網絡有高頻網絡,高速網絡,數字網絡與信號閾值特別低的網絡,根據這些元器件的特點,可以在原理圖上找出這些網絡。在S3C2410核心板上找出的核心網絡為[6]:SDRAM的時鐘信號,SDRAM的片選信號,CPU與SDRAM之間的數據信號,地址信號等。因為SDRAM的工作頻率達到了133MHz,而CPU的工作頻率為266MHz。

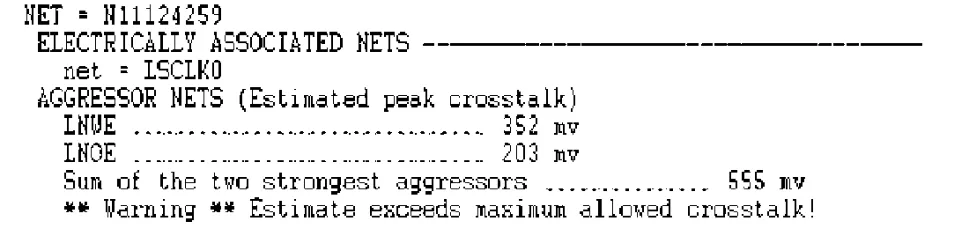

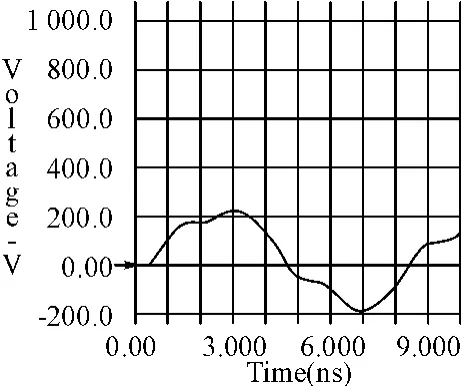

2)利用HyperLynx的快速整板仿真功能[7]。Hyper-Lynx提供了快速的整板仿真,并且不需要器件的IC模型。通過軟件仿真,設置串擾閾值為150mV得到所有串擾超過閾 值 的 網 絡:LSCLK0,LNWE,LADDR0-24,LDQM0-3,LNOE,NGCS0-5,N11070248,N11070262,LDATA0,1,8,9,LSCKE, LNSCS0,LSCLK1,LNSCAS,LNSRAS,NFRE,NXBREQ,NTRST,L3CLOCK,CLE,TDO,NWAIT,NFCE,NFWE,ALE,L3MODE,NRESET,VD2,TMS仿真結果部分如圖1。

圖1 快速仿真結果

圖1可見對于LSCLK0串擾過強的總共有兩個網絡,分別為LNWE、LNOE。

設置閾值串擾電壓為150mV并不是電路不能承受150mV,只是為了設置一個閾值電壓,找出那些串擾比較大的網絡。因為快速仿真的精確度并不高,找出關鍵網絡后必須根據PCB各器件所能承受的干擾閾值再進行準確的分析。

一般采用兩種方法結合的辦法來尋找關鍵網絡。第一種是通過經驗尋找,第二種是通過串擾強度分析尋找,兩種方法結合后可以優勢互補,找出高速PCB板上的關鍵網絡,保證了分析的全面性與準確性。經過驗證本組合方法可以有效準確地查找出關鍵網絡。

3 反射串擾的分析改進與驗證

在前面一部分內容中已經找出了關鍵網絡,下面以關鍵網絡中的LSCLK0為例進行反射與串擾仿真并改進。

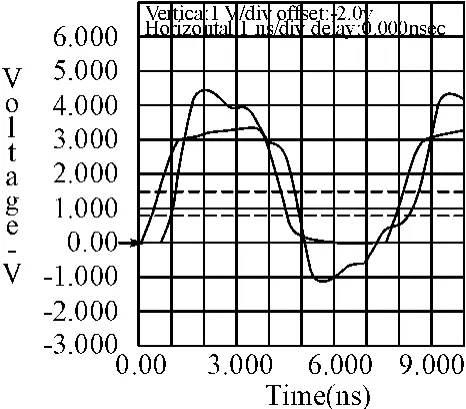

反射:設置LSCLK0網絡源端為133MHz,峰值為3.3V的方波驅動,得到負載端波形如圖2所示。

圖2 改進前反射仿真結果

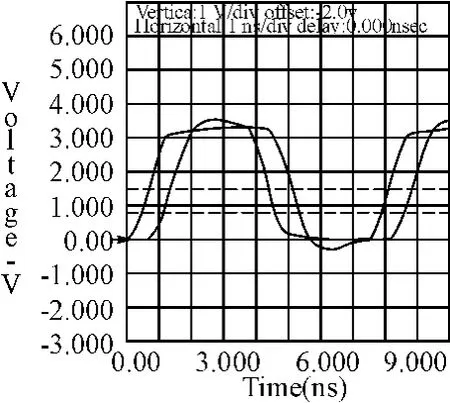

從圖2中得出末端SDRAM接收到的信號正峰值逼近4.6V,負峰值超過-1.0V。由HY57V561620B參考手冊知其所有管腳的限制電壓為-1V~4.6V,顯然網絡由反射引起的過沖太大。反射主要是由于網絡上的阻抗不連續產生的,包括過孔、拐角、源端/負載端阻抗不匹配等[8]。其中尤以源端/負載端阻抗不匹配影響最大。采用端接技術[9]抑制反射。端接技術分為:串聯端接,簡單并聯端接、戴維南并聯端接、主動并聯端接、RC并聯端接。不同的方法有不同的優勢和缺點,采用哪種方法看具體情況而定,這里不再贅述。軟件的terminator wizard提示只需在源端串接一個阻值為55Ω的電阻即可改善性能。串接后仿真圖形如圖3。

圖3所示負載端信號波形得到明顯改善,并且串聯端接方法簡單,實行起來也比較方便。所以這里已經不再需要其他的改進辦法,包括其他端接方法和對于過孔,拐角的改善。

圖3 改進后反射仿真結果

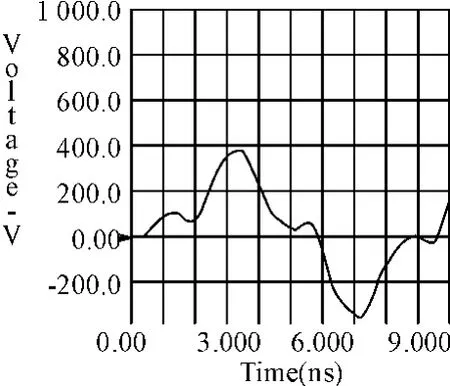

串擾:LSCLK0負載端的接收電平要求為(高2V~3.9V)(低-0.3V~0.8V),并且器件的管腳限制電平為-1V~4.6V,從而得出最大的耦合電壓不能超過700mV。從快速整板仿真結果可以看出,LNWE對LSCLK0的串擾強度最大,達到了352mV,其次是LNOE也達到了203mV。雖然兩個網絡的干擾值之和為555mV并沒有超過閾值,但電磁干擾錯綜復雜,必須為其他未知的干擾留下充足的余量。所以要對網絡進行改進。并且快速分析并不夠準確,在確定關鍵網絡后可以利用交互式串擾仿真來進行分析。仿真得到波形如圖4。

圖4 改進前串擾仿真結果

仿真時軟件自動給出超過設定耦合閾值150mV的網絡有三條,分別是LNWE、LNOE、11070276。源端串擾較小可以不用考慮。負載端串擾強度總和過沖接近于400mV與-400mV,距離700mV的閾值太近,必須加以抑制。一般抑制串擾的方法有增加兩線間距和在耦合線間加上一條隔離地線。由于加地線的方法操作復雜,并且耦合網絡不僅僅是一條,所以要加的地線也不只一條,這里不建議采用。采用改變走線位置的方法,加大受害線與攻擊線的距離,遵循3W原則(即走線間距為走線寬度的三倍)。改進后串擾仿真波形如圖5所示。

圖5 改進后串擾仿真結果

通過仿真結果可知與LSCLK0產生耦合的網絡為LNWE,11070276,與改進前相比少了一個網絡LNOE,因為改變走線位置后LNOE對LSCLK的耦合已經低于設定的閾值,所以不再是攻擊網絡。負載端總耦合強度明顯減弱,上下都只達到200mV左右,為700mV閾值留下了足夠的余量,符合設計要求。

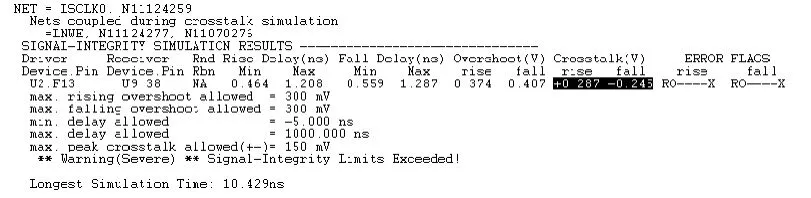

若對于網絡LSCLK0的攻擊網絡過多,在交互式仿真時會耗費大量的時間,所以這時可以采用詳細整板仿真的方法[12]。圖6所示為改進前的詳細仿真結果,其中串擾強度為432mV和-395mV。改進后仿真結果如圖7所示,串擾強度下降為287mV,-245mV。

圖6 詳細整板仿真結果

圖7 改進后詳細整板仿真結果

綜上所述,對某型高速PCB板進行信號完整性分析時,首先要先確定關鍵網絡(采用經驗,快速仿真結合組合的辦法)。然后利用交互式辦法對反射進行仿真與改進。對于串擾可以先采用交互式辦法,若網絡復雜可以再采用詳細整板仿真,分析并改進。

4 結語

本文基于HyperLynx軟件對S3C2410核心板進行了信號完整性的分析,從反射與串擾入手說明了分析方法與改進方法,并對改進前后的仿真結果做了比較。總結了對于任何高速PCB板進行信號完整性分析的一般性方法和步驟。提出了查找關鍵網絡的組合方法。但是由于S3C2410核心板的IBIS模型不易獲得,所以采用了Hyper-Lynx軟件提供的通用模型,對仿真結果有一定的影響。

[1]卓沛,嚴國萍.高速數字系統中的時序分析與設計[J].計算機技術與發展,2007,17(7):23-24.

[2]楊華.高速PCB電磁兼容性分析與研究[D].武漢:海軍工程大學,2011:77-90.

[3]賈凱賓.高速數字PCB互連設計信號完整性研究[D].南京:南京理工大學,2008:48-53.

[4]曹海舟.減小PCB微帶線間串擾方法分析[J].電子質量,2008(1):19-24.

[5]劉波.高速數字電路信號完整性和電源完整性的研究[D].西安:西安電子科技大學,2011:27-31.

[6]吳昊.高速數字電路板級信號完整性分析及其應用[D].武漢:海軍工程大學,2008:55-57.

[7]張海風.HyperLynx[M].北京:機器工業出版社,2006:4-70.

[8]王宗躍.高速PCB信號完整性分析與研究[D].武漢:海軍工程大學,2009:30-35.

[9]郝麗翠.高速互連設計中的信號完整性分析[D].南京:南京理工大學,2009:52-60.

[10]許建平.軍用計算機信號完整性分析與設計[J].計算機與數字工程,2012,40(1).

[11]譚力,蘇鋼,朱光喜,等.多天線系統中的高速串行互聯總線的信號完整性[J].計算機與數字工程,2008,36(9).

[12]趙光.PADS2007高速電路板設計[M].北京:人民郵電出版社,2009:26-33.