基于FPGA的高速多通道AD采樣系統的設計與實現

徐加彥,張之萬,陳興林,張廣瑩

(哈爾濱工業大學 航天學院,哈爾濱 150001)

光刻機作為集成電路芯片的制造設備,是超高精度的控制系統。國家在2006年十二五規劃發布的《國家中長期科學和技術發展規劃綱要(2006-2020)》中將“極大規模集成電路制造裝備及成套工藝”明確為重大專項。通過這一專項的實施,攻關60 nm光刻機的關鍵技術,為下一步研制更高分辨率光刻機打下堅實基礎。在光刻機控制系統中,其環境因素,如溫度、濕度等對高精度的控制有著重要的影響[1]。因此需實時反饋溫度、濕度等環境因素。多通道AD采樣系統作為光刻機信號采集板卡的核心部分,其采樣速度、精度對提高整個光刻機控制系統的精度有著重要影響[2]。

有限狀態機FSM(finite-state machine)又稱有限狀態自動機,簡稱狀態機,是表示有限個狀態以及在這些狀態之間的轉移和動作等行為的數學模型。它可應用在硬件電路系統設計、軟件工程、網絡協議等。就其速度而言,FSM并行同步完成許多運算和控制操作。這樣,由狀態機構成的硬件系統比對應的CPU所能完成同樣功能的軟件系統的工作速度要高出3~5個數量級。因此在超高速串行或并行AD、DA器件的控制,硬件并行通信模塊RS232等實現有著廣泛的應用[3]。

本文采用AD7606作為采樣芯片,設計采樣電路,并充分利用狀態機高速性、穩定性、高效性的特點,采用FPGA作為可編程邏輯器件,設計采樣芯片的控制時序和讀寫時序。傳統的采樣系統使用UART方式傳輸采樣結果,處理器需采用中斷方式或查詢方式讀取采樣結果,占用了處理器資源。本文將采樣結果實時儲存在雙口RAM里,處理器可實時讀取采樣結果,不占用處理器資源,提高了處理器的效率。實驗表明,穩定性和控制性能良好。

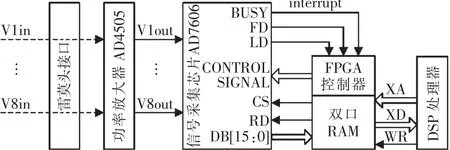

1 總體設計框架

高速多通道AD采樣控制系統框圖如圖1所示,信號采集板卡采用雷莫頭接口的方式同外界模擬信號相連接,其抗干擾、穩定性強。AD4505功放模塊作為外界模擬輸入信號和AD7606模數轉換芯片的隔離芯片,避免外界輸入的模擬電壓過大而導致燒毀AD芯片。AD采樣芯片采用AD7606作為模數轉換芯片,具有8通道同時采樣,16位輸出的特點,是一款高分辨率、雙極性輸入、同步采樣的高性能模數轉換芯片。采用Altera公司的EP2C35F672可編程邏輯控制器件對AD7606進行時序控制。并在FPGA里設置一塊雙口RAM,存儲AD7606的數字輸出結果。DSP作為信號采集板卡的主控處理器,可任意時刻讀取雙口RAM里的采樣數據。

圖1 采樣控制系統框圖Fig.1 Block diagram of sampling control system

2 FPGA控制AD7606的軟件實現

2.1 AD7606的硬件電路圖

AD7606是AD公司生產的一款高分辨率、雙極性輸入、多通道同步采樣的高速模數轉換芯片。內置二階抗混疊模擬濾波器對輸入信號進行濾波,內置數字濾波器,提供過采樣功能;可以靈活地實現并行/串行輸出;本課題設計的AD7606采用并行輸出方式。通過FPGA硬件,采用狀態機的編程方式,實現對AD7606的時序控制。

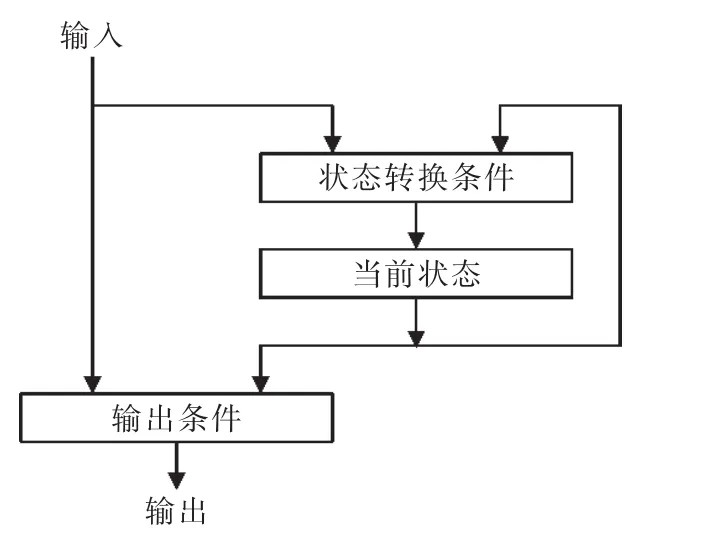

2.2 有限狀態機

圖2為有限狀態機模型,下一個狀態和輸出由當前狀態和輸入所決定。有限狀態機數學模型為(Σ,Γ,S,s0,δ,ω)。 其中:Σ 是輸入字母表;Γ 是輸出字母表;S是狀態的集合;s0是初始狀態;δ是狀態轉移函數;ω 是輸出函數。其中 δ:S×Σ→S ω:S×Σ→Γ。

圖2 有限狀態機模型Fig.2 Model of finite state machine

在數字電路中,狀態機可用可編程邏輯控制器件來建造,通過寄存器來儲存狀態變量,確定狀態轉移的一塊組合邏輯和確定狀態機輸出的另一塊組合邏輯。

2.3 時序程序的設計

有限狀態機的設計對系統的高速性能、高可靠性、穩定性都具有決定性作用。采用狀態機的形式,在每個狀態中,狀態機可并行同步完成許多運算和控制操作,相比于CPU按照指令逐條運行的方式,一般有狀態機構成的硬件系統比對應的CPU完成同樣功能的軟件系統的工作速度要高出3~5個數量級。在可靠性能方面,狀態機是在FPGA通過純硬件電路構成,其運行不依賴軟件指令逐條執行,因此不存在CPU運行軟件過程中的許多缺陷[3]。

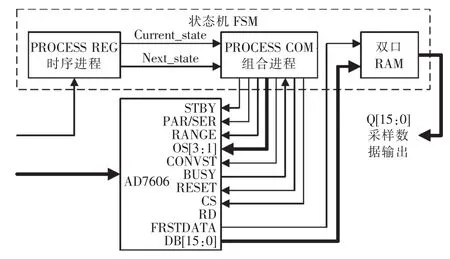

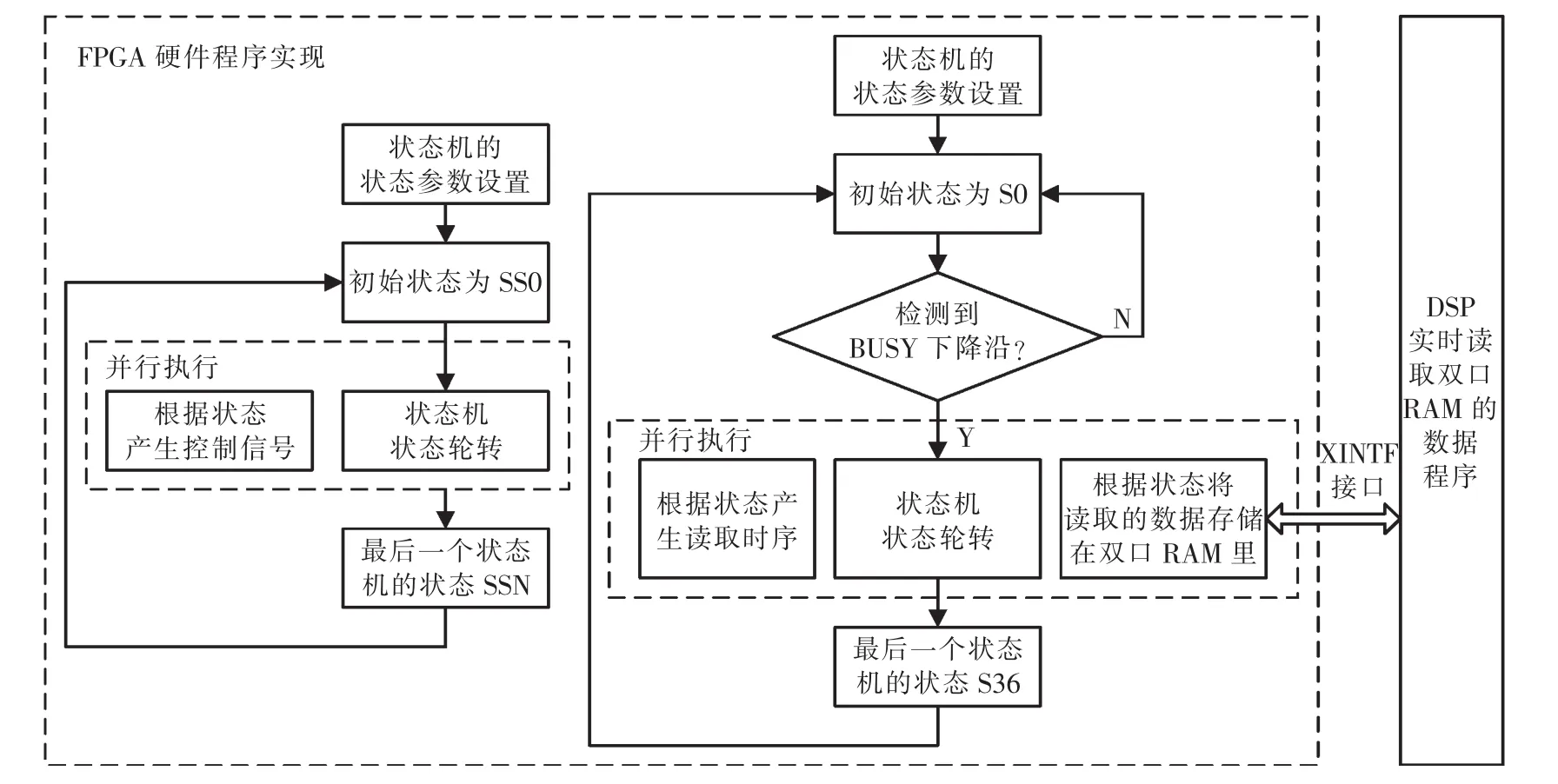

如圖3所示為采用狀態機形式的結構框圖,程序分為寫配置模塊和讀取數據模塊2個模塊。

圖3 采樣狀態機的結構框圖Fig.3 Block diagram of the sampling state machine

在寫配置模塊里配置AD7602的控制信號,比如串行模式/并行模式的選擇,輸入電壓的范圍、待機模式還是省電模式,過采樣倍率的倍數等。

讀取數據模塊是整個采樣系統的關鍵,采用狀態機的形式,設置CS和RD信號線的時序。程序要根據BUSY信號產生中斷信號,來確定轉換是否完成。

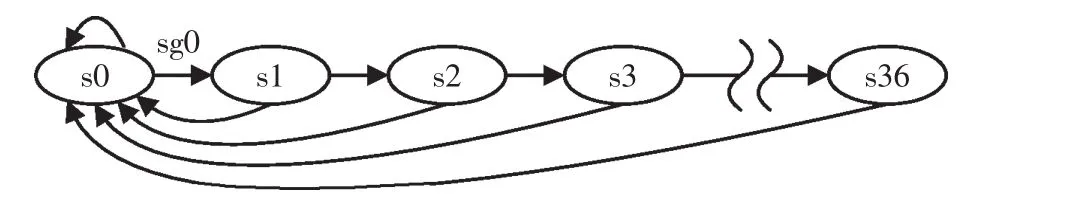

根據AD7606的工作原理和寫時序,設計接口邏輯模塊,圖4為狀態機輪轉狀態圖。

圖4 狀態機輪轉狀態圖Fig.4 State machine cycle state diagram

AD7606轉換控制信號為CONVSTA和CONVSTB。 CONVSTA 控制 V1,V2,V3,V4 通道,CONVSTB 控制 V5,V6,V7,V8 轉換通道,本文將 CONVSTA和CONVSTB短接在一起,8通道同時轉換。S0是空閑狀態,CS為高電平,RD為高電平;通過邊沿檢測是否有BUSY信號,若有則進入S1狀態,否則等待。由于等待CS穩定下來(CS到RD設置時間t8),需要插上延時狀態 S2,到 S3 穩定,在 S4,S5 狀態將RD拉低,讀取第一通道V1的轉換結果,之后依次重復7個脈沖序列,可使各通道的轉換結果按升序逐個輸出到并行總線DB[15:0]上,在狀態機里可方便地設置各種狀態。

圖5為程序框圖,通過Verilog HDL硬件語言,基于狀態機的思想,通過硬件實現對采樣芯片的控制時序和讀取時序,并將讀取的數據實時存儲在雙口RAM里,這樣DSP可實時讀取RAM里的數據,和通過中斷方式或者查詢方式讀取采樣數據相比,減小了對DSP資源的占用,提高了DSP的效率。硬件的兩部分:控制時序和讀取時序并行執行。在控制時序和讀取時序中通過狀態機方式并行執行程序,提高了采樣速率和穩定性。

圖5 程序流程圖Fig.5 Program flow chart

3 結果測試

3.1 多通道采樣系統的實時采樣測試

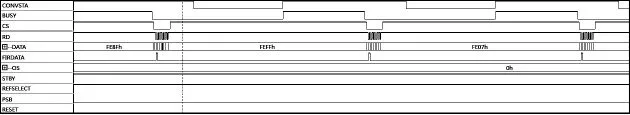

通過邏輯探測儀實時測量的數據,給定第二通道3.3 V的電壓,其他通道給定0 V電壓,測得的信號如圖6、圖7所示。

圖6 AD7606控制時序結果圖Fig.6 Figure of control timing results

圖7 AD7606讀輸出結果圖Fig.7 Figure of reading the output

AD7606的輸出編碼方式為二進制補碼,傳遞函數為:CODE=

當第二通道輸入3.3 V時,理論值為2A3Dh;圖7所示實際值為28E7h,對應3.195 V,存在一定誤差,是因為施加的激勵電源有一定的諧波,采樣系統采集了此時波形。 FDB7h,FD7Eh,FE27h,FE17h,FCEFh,FF0Fh,分別對應實際值為-0.17 V,-0.18 V,-0.144 V,-0.148 V,-0.21 V,-0.07 V。

通過實驗實時測量表明,通過狀態機編寫的對AD7606實現時序邏輯控制的硬件電路,其實驗結果如圖6、圖7所示,和AD7606芯片手冊上的讀寫時序圖一致,表明實驗結果準確。

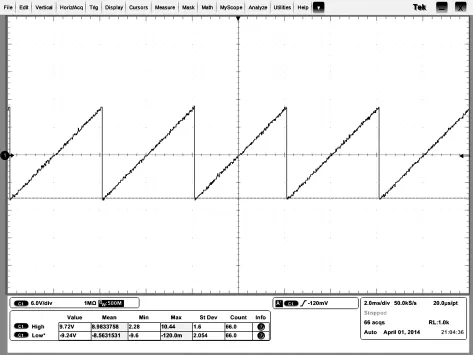

3.2 采樣系統準確率測試

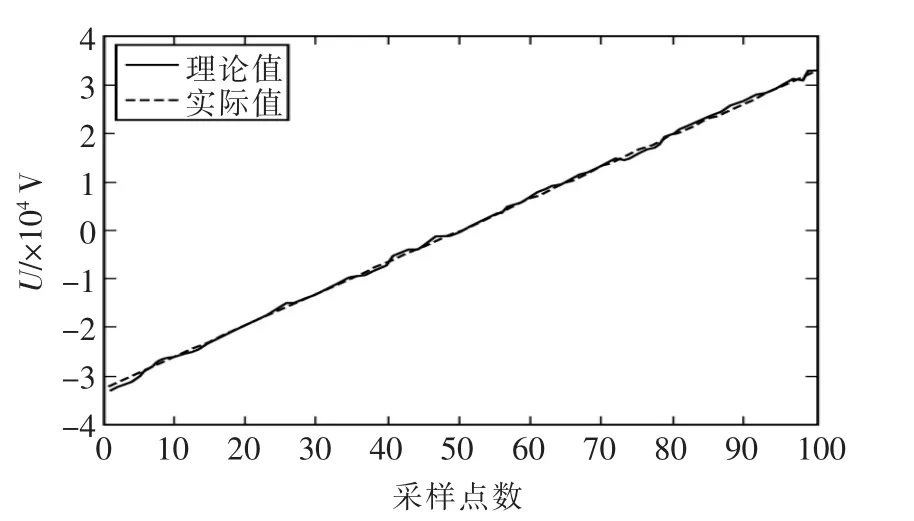

實驗采用Altera公司EP2C35F672型FPGA作為可編程邏輯控件,TI公司的TMS320F2812作為處理器[4],設計的采樣系統其采樣周期為4 μs。如圖8所示采用Tektronixs公司的AFG3052C型波形發生器產生幅值為-10 V~+10 V,周期為4 ms的鋸齒波形。在FPGA里按照時序依次存儲100個AD采樣輸出結果于雙口RAM里。通過DSP讀取雙口RAM數據,在軟件程序里將數據保存,然后通過Matlab軟件繪出曲線[5]和理論值比較,其結果如圖9所示。

圖8 實驗采樣的鋸齒波Fig.8 Experimental sampled waveform

圖9 采樣系統的輸出結果Fig.9 Output of the sampling system

通過實驗表明,采樣系統采樣的結果和理論值誤差很小,最大誤差為0.1%,整體采樣系統穩定性、誤差性達到要求[6]。

4 結語

本文利用狀態機在高速、高可靠性、穩定性方面的特點,采用FPGA作為可編程邏輯控件,以狀態機的形式,編程設計多通道高速AD采樣系統的控制時序和讀寫時序。將采樣結果實時存儲在雙口RAM里,這樣處理器可實時讀取采樣結果,相比于通過UART方式傳輸采樣結果給處理器,處理器采用SCI串口中斷方式讀取采樣結果,本文設計的采樣系統減少了對處理器資源的占用。對提高處理器的效率具有很大意義。實驗表明,系統的穩定性、高速型、誤差均達到要求,具有很強的工程實用價值。

[1]Boonman M,van de Vin C,Tempelaars S,et al.The performance advantages of a dual stage system[J].SPIE,2004,5377:742-757.

[2] 谷林.光刻機工件臺和掩膜臺同步控制研究[D].哈爾濱:哈爾濱工業大學,2013.

[3] 潘松,黃繼業.EDA技術與Verilog HDL[M].2版.北京:清華大學出版社,2010.

[4] 蘇奎峰,呂強,常天慶,等.TMS320X281xDSP原理及C程序開發[M].北京:北京航空航天大學出版社,2008.

[5] 王正林,王勝開.MATALAB/Simulink與控制系統仿真[M].北京:電子工業出版社,2008.

[6] 齊紅濤,蘇濤.基于FPGA的高速AD采樣設計[J].航空兵器,2010(1):35-39.