基于FPGA的RS485-USB轉換器設計與實現

李 勛 ,劉文怡

(1.中北大學 電子測試技術國家重點實驗室,太原 030051;2.中北大學 儀器科學與動態測試教育部重點實驗室,太原 030051)

USB接口傳輸速率快并且性能優良,它支持3種信道速率:低速為1.5 Mb/s、全速為12 Mb/s以及高速為480 Mb/s[1]。但是USB傳輸距離也不能超過30 m,這就使USB在工業應用領域中受到傳輸距離的限制。RS485總線采用平衡驅動、差分接收結構,具有抗共模干擾能力強,靈敏度高,驅動能力強等特點[2],同時其顯著優勢是傳輸距離可達1200 m以上,但是RS485傳輸速度低,可靠性差。

將RS485、USB兩者結合起來,優勢互補,就能夠產生一種快速、可靠、低成本的遠程數據通信轉換接口。目前,FPGA集成度高和工作頻率、穩定性良好,抗干擾能力強,編寫程序易于模塊化控制,易于配置等優點,逐步成為各領域數字電路的首選。設計一種基于FPGA的RS485-USB轉換器就可以有效應用到各種速率的數據處理、采集、在線檢測場合。本文主要從系統總體設計方案、硬件設計和軟件設計方面介紹一種基于FPGA的RS485-USB的轉換器的設計與實現。

1 系統總體設計

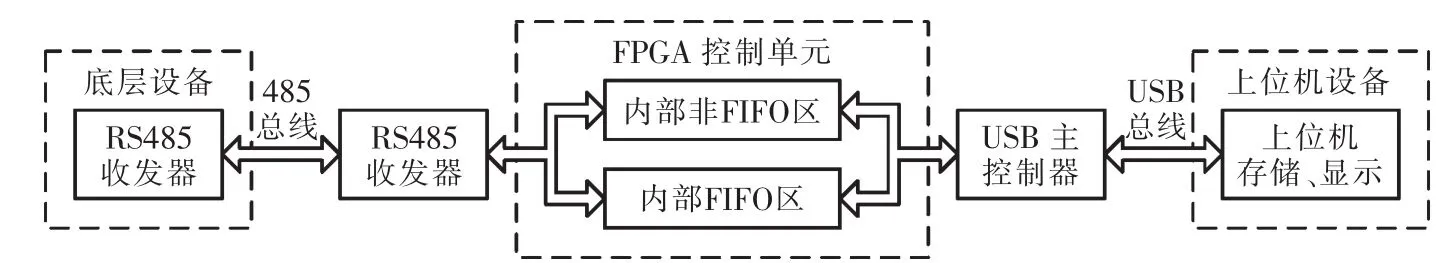

本文介紹的RS485-USB轉換器主要是通過靈活配置FPGA實現RS485接口和USB接口實現通信速率可調的遠距離數據通信,同時通過更改USB主控芯片的固件程序可以切換轉換器數據立即串行傳輸通信和數據內部FIFO緩存并行傳輸通信兩種模式,本文設計的固件程序選擇第二種并行傳輸通信模式。系統的總體設計方案如圖1所示。

該RS485-USB轉換器主要包括RS485收發器、FPGA控制單元、USB控制單元3部分。系統工作原理如下:底層設備信號經485接口芯片轉換為485電平,通過485總線傳輸至FPGA控制單元;FPGA單元主要負責接收485總線傳輸過來的信號,通過改變程序調節信號傳輸速率,對信號進行FPGA內部FIFO緩存,FPGA通過USB主控芯片對FIFO內部空、半滿、滿輸出的3種存儲狀態進行判定。該設計中固件程序主要是對CY7C68013A接收到FIFO半滿信號上升沿進行判定。若為上升沿,則FPGA將數據并行上傳;反之監測等待。USB控制器就是上位機與FPGA控制單元的通信接口,用于雙向傳輸信號;上位機設備主要負責數據存儲、采集和在線檢測并進行數據通道、波形顯示。

2 RS485-USB轉換器硬件設計

圖1 系統總體設計框圖Fig.1 System block diagram of the overall design

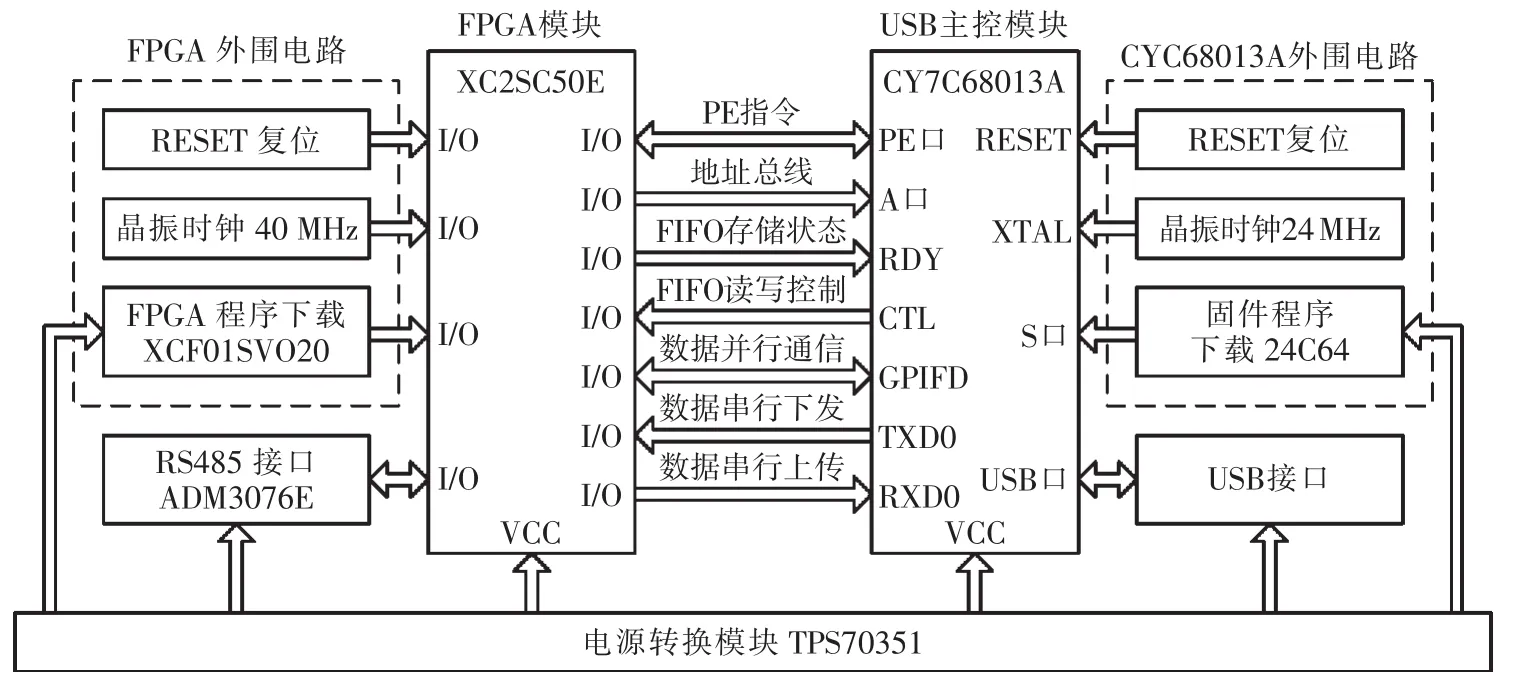

圖2 硬件設計原理示意圖Fig.2 Schematic diagram of the hardware design

本文硬件部分主要負責完成RS485與USB總線轉換中的各控制模塊的硬件電路設計,其滿足了RS485與USB雙向通信,保證了數據的準確性和抗干擾能力。硬件設計主要的原理示意圖如圖2所示。

本文設計的RS485-USB轉換器中的硬件部分主要包括以下4個模塊:

電源轉換模塊所選的FPGA芯片需要1.8 V供電,USB主控芯片和RS485協議芯片需要3.3 V供電,故設計選用具有高準確度、快速瞬態響應等優點的TPS70351芯片實現電平轉換,滿足設計中供電要求。

RS485總線接口模塊RS485采用平衡發送和差分接收方式來實現通信,設計選用ADM3076E作為485接口芯片。在某些工業控制領域中,工作現場情況復雜,各節點之間存在很大的共模電壓,雖然RS485接口采用的是差分傳輸方式,但當共模電壓超過RS485接收器的極限電壓,接收器就無法正常工作,嚴重時會燒毀芯片和儀器設備。為解決這一問題,該轉換器設計中通過加入RS485將電源和RS485收發器的電源隔離,在信號輸人和輸出中均采用了光電耦合器HCPL-2631,其開關頻率高達 10 MHz,完全滿足數據傳輸要求,實現數據的長線傳輸。

FPGA控制模塊主要負責整個電路中邏輯控制,其工作模式主要有系統復位模式、數據存儲模式和數據轉換模式。本設計選用的FPGA芯片是Xilinx公司生產的Spartan-2E系列XC2S50E,該芯片具有很高的邏輯資源,易于配置等綜合性能;其程序下載PROM模塊選用的是與FPGA相對應的XCF01SV020芯片,該芯片使用方便,能夠為FPGA提供快速的再編程位流[3]。

USB總線控制模塊主要負責控制連接FPGA與上位機的通信,本設計選用賽普拉斯研發出的芯片CY7C68013A作為USB接口電路核心芯片。CY7C68013A支持12 Mb/s的全速以及480 Mb/s高速傳輸,除集成了超強的USB2.0引擎SIE外,還集成了改進的增強型8051內核[4]。USB主控芯片CY7C68013A選用ATMEL公司的24C64芯片下載固件程序,該芯片具有很快的讀寫速度、低功耗,是現在使用的非易失性存儲芯片中靈活性高的類型之一。

3 RS485-USB轉換器軟件設計方案

本文設計的RS485-USB轉換器中的軟件設計部分主要包括FPGA控制模塊、CY7C68013A固件程序控制模塊、設備驅動程序控制模塊。

(1)FPGA 控制模塊

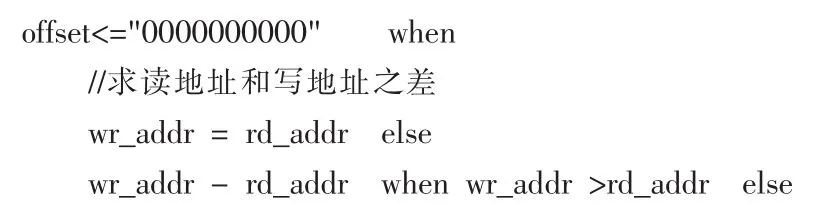

FPGA的功能控制程序是通過Xilinx ISE12.1軟件平臺實現,控制程序選用硬件描述語言VHDL語言進行功能模塊化編寫的。為了匹配FPGA和CY7C68013A之間的數據傳輸速率,提高數據的傳輸效率和準確性,在FPGA內部開辟了1 KB的FIFO緩存器。FPGA接收到RS485串口數據后,對其進行消抖、數據傳輸速率調整及波特率檢測、串并轉化處理,進行內部FIFO緩存時將寫信號電平拉高,數據在寫信號上升沿被寫入到FIFO,同時寫地址加1;當FIFO內部數據達到半滿時,半滿標志(half_flag)變為1,半滿信號上升沿的跳變觸發USB主控芯片CY7C68013A中的CTL控制信號將FPGA讀信號拉高,同時在讀信號上升沿將數據讀出,通過USB接口傳輸給上位機,讀地址加1。半滿標志位通過讀地址和寫地址在FPGA內存中的相對位置進行計算,部分程序代碼如下:

FPGA配置程序主要通過倍頻、分頻晶振基準頻率和控制讀寫數據狀態機來實現傳輸速率的可調,程序中按功能需求將各模塊進行連接、通信。為了便于應用和檢測,FPGA通過主程序控制MEN(2:0)信號選擇底層設備,指示燈 LED(2:0)信號實時顯示轉換器與上位機在線檢測時復位、設備連接、讀數指示。

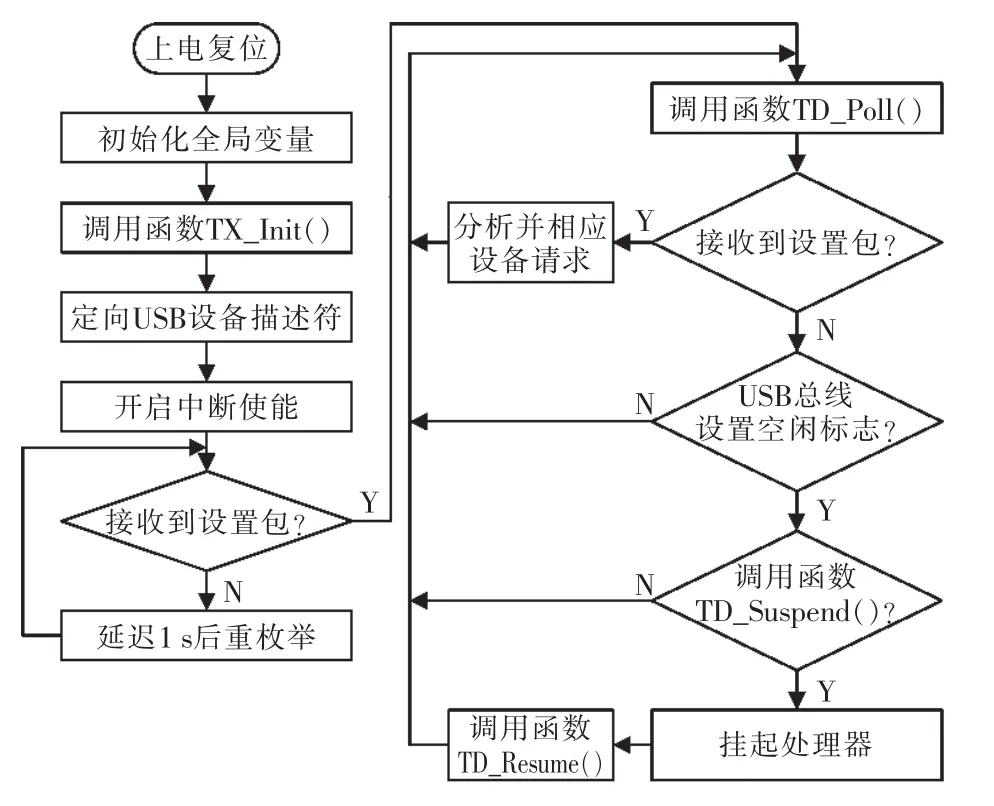

(2)CY7C68013A固件程序控制模塊

USB通信數據、指令是通過CY7C68013A端點連接上位機與外部邏輯處理器FPGA。CY7C68013A的固件程序下載方式有兩種:一種是固件程序下載存儲到片外E2PROM中,上電后自動將固件程序加載到CY7C68013芯片RAM中;另一種是在線加載方式,計算機需要編寫、存儲固件下載驅動程序,當CY7C68013A連接到計算機后,由驅動程序下載固件[5]。由于第一種固件程序加載方式便于擴展、操作簡單,本文選用第一種方式。CY7C68013A固件功能的實現主要集中在三個模塊:調用TD_Init()函數完成CY7C68013A的初始化模塊;設備請求模塊,對應固件編程框圖中的設備請求部分;重復調用函數TD_Poll()實現用戶所需的功能模塊,完成底層串口設備與USB通信數據之間的轉化。在本設計轉換器應用的固件程序流程框圖如圖3所示。

圖3 CY7C68013A固件編寫流程框圖Fig.3 Flow diagram of CY7C68013A firmware preparation

(3)設備驅動程序控制模塊

設備驅動程序主要實現主機與底層設備端口之間連接的功能,本文采用CYPRESS公司EZ-USB開發系統提供的全新驅動程序CYUSB.SYS。安裝驅動時,需找到與用戶編寫的PID/VID代碼、設備描述相匹配的CYUSB.INF文件,驅動即可被正確安裝,此時設備才可以正常使用[6]。

4 功能測試

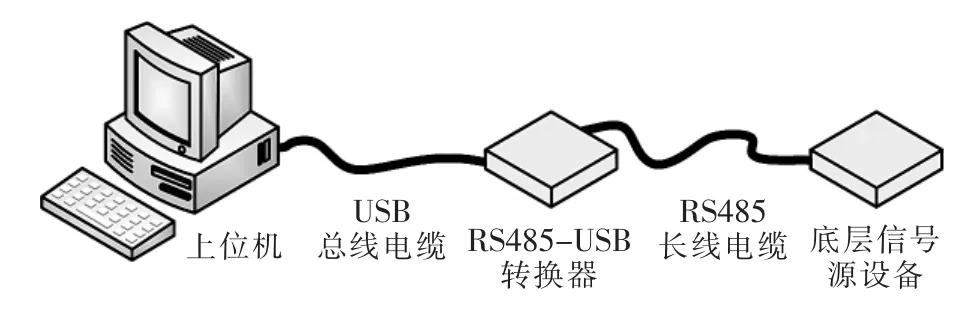

功能測試模塊主要包括底層信號源設備、RS485-USB轉換器、上位機3部分,其關系框圖如圖4所示。上位機軟件主要采用VB進行編程,實現對底層信號源設備上傳數據檢測、實時顯示的可視化界面操作。

圖4 功能測試系統連接框圖Fig.4 Connection diagram of functional test system

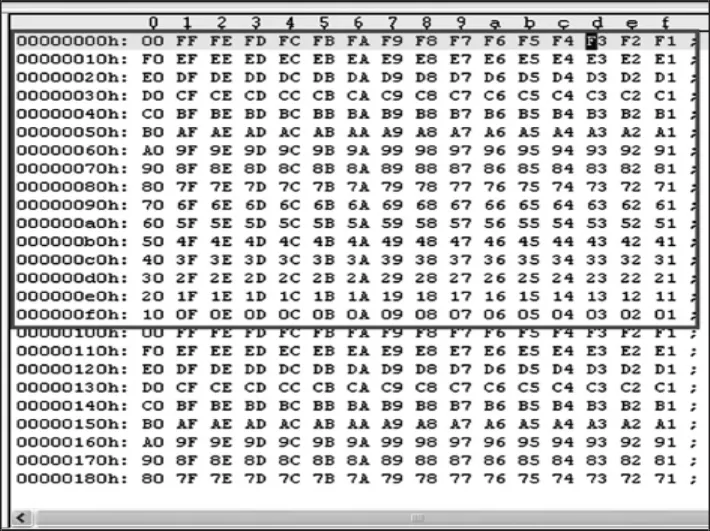

通過程序下載盒將FPGA各功能模塊程序下載到該轉換器XCF01SV020芯片中。轉換器利用RS485接口接收信號源產生的遞減數據,經過接口芯片轉化,將差分信號轉換成串行數據輸入,圖5為利用示波器測出的轉換器RS485接口電路轉換后RX端的信號波形。圖5中截取了三組串行信號的波形,信號源設定串行信號第一位為起始位“0”,后八位為串行數據,最后三位為空閑信號“1”組成的十二位串行數據,并且先發低位再發高位。

從圖中可讀出三組信號為“000010110111”、“011100110111”、“001100110111”, 去掉起始位和空閑位,調整高低位順序分析得出轉換器接收到的信號源發出的三組遞減數據位“01101000”、“01100111”、“01100110”。

本設計中遞減數據實時采集圖如圖6所示。上位機界面顯示遞減數據結果與示波器測試轉換器RS485接收底層信號源遞減數據波形圖結果一致,轉換器實現了RS485總線轉換到USB2.0總線接口的數據通信功能。

圖6 上位機數據采集圖Fig.6 PC data acquisition diagram

5 結語

本文介紹了一種基于FPGA的RS485-USB轉換器設計方案,并進行了實驗驗證,其特點在于充分利用了FPGA易于編程和配置,以實現特定模塊化功能,數據傳輸速率可調;同時結合了RS485接口具有長線遠程傳輸特性,USB接口高速率傳輸、熱插熱拔優良特性,實現了快速、可靠、低成本的RS485-USB轉換器轉換功能。該設計轉換器具有硬件電路簡單、軟件設計靈活、體積小、功耗低、可在線更新等特點,可以應用到工業數據采集、檢測等領域,其傳輸速率范圍可控制在9.6 kb/s~72 Mb/s,具有很高的實用性。

[1] 王寶珠,楊永,林永峰,等.基于USB接口的數據采集系統設計[J].電子技術應用,2010,36(1):67-70.

[2] 孫東,韓紹坤,邢懷飛.自制RS-232/RS-485轉換器應用[J].電子測量技術,2005,48(3):17-18.

[3] 劉福奇.FPGA嵌入式項目開發實戰[M].北京:電子工業出版社,2009.

[4] 馬俊濤,李振字.S1aveFIF0模式下CY7C68013和FPGA的數據通信[J].中國傳媒大學學報:自然科學版,2009,16(2):38-44.

[5] 呼媛,李白田,胡炳檬,等.EZ-USBFX2固件與設備驅動開發[J].微計算機信息,2010,26(7):162-164.

[6] CypressSemiconductorCorporation.EZ-USB FX2 Technical Reference Manual Version 2.2[Z],2003. ■