FPGA構造單向串行LVDS接口RAM存儲器

宋 娟,吳榮斌,張 剛

(1.太原理工大學信息工程學院,山西太原030024;2.蘭州交通大學電子與信息工程學院,甘肅蘭州730070)

大數據時代,越來越多的信息轉換為數據進行存儲和處理,因此對控制系統中存儲系統的數據快速處理能力和實時性提出更高要求,否則極易造成數據處理中的“瓶頸”現象[1-2]。并行傳輸方式在提升時鐘頻率時容易引起信號線間的互擾,導致傳輸錯誤,同時增加位寬會增加系統板布線密度,因此串行通信技術正在取代并行總線而成為高速數據接口的主流,而低壓差分信號技術(Low Voltage Differential Signaling,LVDS)在各種高速串行總線得到普遍應用。

目前,嵌入式系統CPU與RAM的控制端口、讀寫使能、地址及數據總線相連,為節約CPU引腳資源,提高其訪問內存的速度,本文使用FPGA提供的RAM IP核,設計實現了基于有限狀態機的單向串行只寫總線型接口RAM存儲器,該存儲器與CPU通過單向串行只寫總線(One-way Write-Only Serial Bus,OWOSB)進行數據交換[3],并且使用低壓差分傳輸技術抑制信號干擾,有利于提高數據訪問速率和傳輸可靠性。不同于CPU直接通過并行線對RAM存儲器進行訪問的模式,該存儲器以消息包的方式進行訪問。

CPU與存儲器之間只有兩對差分數據線相連,很大程度上節約了RAM之前所需要的并行總線,因此CPU可以不受地址和數據引腳的限制,增大訪問的內存容量。并且串行差分信號線間干擾較小,有利于提高CPU訪問存儲器的速度,具有良好的擴展性。

1 存儲器的結構設計

1.1 存儲器系統總體結構

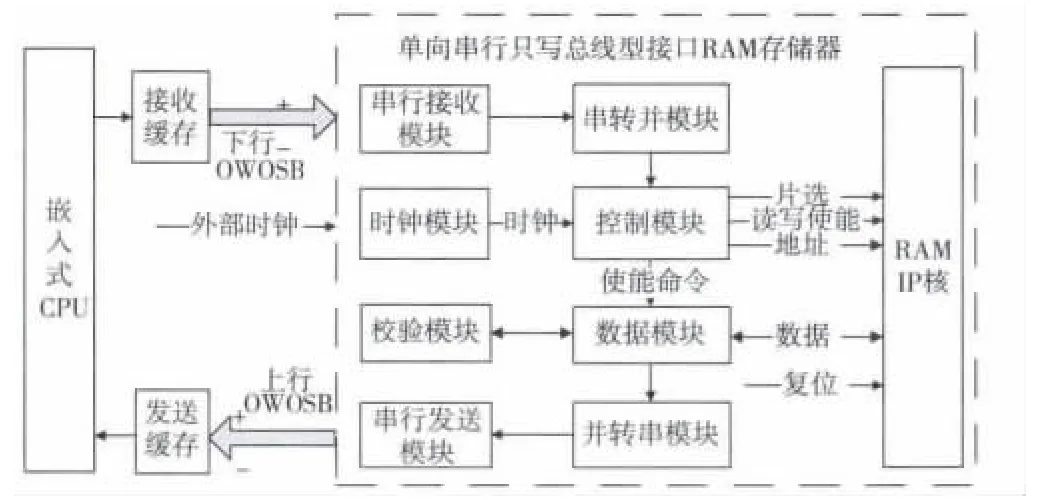

單向串行只寫總線型接口RAM存儲器有時鐘、復位和單向串行只寫上行總線3個輸入和1個單向串行只寫下行總線端口。主要由8個模塊組成:時鐘模塊、串行數據接收模塊、串轉并模塊、控制模塊、數據模塊、串行數據發送模塊、并轉串模塊以及校驗模塊,見圖1。

圖1 RAM存儲器系統結構框圖

時鐘模塊:為存儲器的其他各個模塊提供所需時鐘頻率。

串行接收/發送模塊:接收或發送消息包。

串轉并模塊:對串行數據包進行解析分包,把串行數據轉為并行數據。

并轉串模塊:把RAM中讀出的并行數據由高位到低位串行發送,并把發送數據幀頭與32位校驗值封裝到數據包。

控制模塊:從并行數據中提取出片選信號、讀寫使能、讀寫數據長度、命令和地址等信息,控制RAM讀寫操作。

校驗模塊:對數據進行校驗計算。

數據模塊:提供與RAM IP核的數據接口。

1.2 接收緩存模塊

存儲器與嵌入式CPU之間首先需要1個緩存來暫時存放CPU向RAM中寫入的數據,本文所使用的緩存都是Xilinx公司提供的FIFO緩存IP核。CPU以32位為單位進行數據處理,而本文所設計的RAM存儲器是以串行數據進行接收的,因此,FIFO的輸入數據寬度為32 bit,輸出數據寬度為1 bit。緩存讀和寫采用不同頻率的時鐘,寫時鐘頻率與CPU相同,讀時鐘頻率與串行傳輸頻率相同,這是考慮到串行傳輸的特點,可以通過提高時鐘頻率來提高傳輸的速度,也方便數據的存取。

發送緩存模塊類似,不再贅述。

1.3 時鐘模塊

Xilinx Virtex-5開發板內含鎖相環(Phase Locked Loop,PLL)模塊與8個數字時鐘處理器(Digital Clock Management,DCM)模塊[4-5]。PLL 是一種反饋電路,利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位,從而使得電路上的時鐘和某一外部時鐘的相位同步,DCM模塊內部構成:延遲鎖相環(Delay Locked Loop,DLL),其核心功能是消除輸入時鐘與輸出時鐘之間的延時;數字頻率綜合器(Digital Frequency Synthesiser,DFS):可對時鐘進行倍頻、分頻合成新頻率;PS(相位偏移):可對DCM模塊的9個輸出信號進行相位的偏移;狀態邏輯:LOCKED信號有效時,輸出時鐘才可以使用,在此之前,輸出時鐘處于復雜不穩定狀態。

該開發平臺系統時鐘為100 MHz,本文使用2個DCM模塊和2個PLL模塊進行級聯,最后輸出2.15 GHz提供給RAM存儲器,具體如圖2。

圖2 時鐘模塊

1.4 校驗模塊

在高速數據采集系統中,必須保證在限定時間內有足夠的數據傳輸速率和存儲容量,而信號在總線的傳輸過程中不可避免的會發生突發性錯誤,為了提高系統的可靠性,引入數據檢錯機制,即循環冗余校驗(Cyclic Redundancy Check ,CRC)并行算法[6-7]。

CRC是一種誤碼檢測能力強、開銷小、抗干擾性能優異的校驗碼,從其檢錯能力來看,它所不能發現的錯誤的幾率僅為0.004 7%以下。從性能上和資源上考慮,均遠遠優于奇偶校驗及算術和校驗等方式,也是數據存儲和數據通訊領域最常用的差錯校驗碼,其特征是信息字段和校驗字段的長度可以任意選定。

本文在存儲器數據收發過程中均使用8位并行CRC校驗法進行數據檢錯,其生成多項式為G(x)=1+x+x2+x3+x6+x7,系數序列記為11001111。存儲器在接收數據結束后,把計算出的CRC校驗值與CPU發送的校驗值進行比較,如果兩個值不一樣,則在數據傳輸過程中產生錯誤,返回傳輸失敗信號,請求CPU重新發送,若相同,則傳輸正確,返回傳輸成功信號。

2 存儲器的實現

2.1 串行消息幀格式定義

單向串行只寫總線OWOSB,其信息的傳遞只能沿單一方向進行傳輸,在本文OWOSB只用到兩根,一根為上行總線,一根為下行總線。

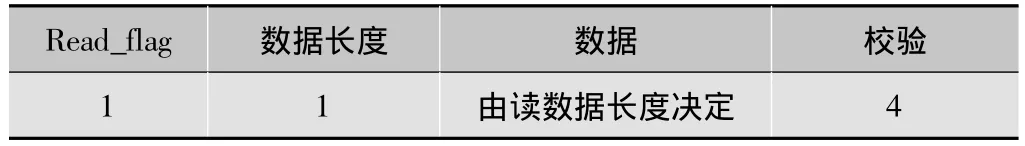

本文定義了RAM存儲器OWOSB通信數據寫/讀幀格式,具體如表1~表2。

表1 串行寫數據幀格式 byte

表2 讀數據幀格式 byte

RAM地址:使用1 byte給每個RAM存儲器進行編號;

命令:表示寫/讀命令,使用“00001111”表示寫命令,“11110000”表示讀命令;

首地址:代表寫/讀數據的起始地址;

數據:寫入/讀取的數據,通過數據長度決定該字段長度;

校驗序列:表示幀校驗;

Read_flag(讀數據先導):用“10101010”表示,CPU 檢測到“10101010”時,則可識別該幀為RAM中讀出的數據幀。

2.2 存儲器接收狀態轉移圖

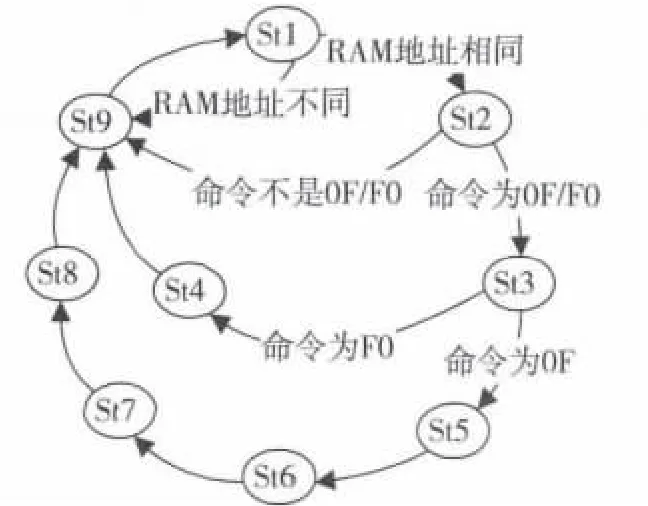

本文使用有限狀態機來實現單向串行LVDS接口RAM存儲器,圖3是RAM存儲器接收狀態轉移圖,各個狀態含義如下:

St1:空閑,等待接收數據幀;

St2:接收CPU發送的寫/讀數據命令;

St3:接收寫/讀數據的首地址;

水分含量在42.99~64.78g/100g之間,平均含量為59.12g/100g,不同部位的平均含量高低依次為頸肩肉含量61.78g/100g、后腿肉含量60.83g/100g、前腿肉含量57.85g/100g、最長肌肉含量55.35g/100g、胸腹部肉含量43.27g/100g。

St4:接收讀數據長度;

St5:接收寫數據長度;

St6:接收要向存儲器寫入的數據;

St7:接收32bit的校驗序列;

St8:驗證接收到的數據是否正確;

St9:接收數據結束。

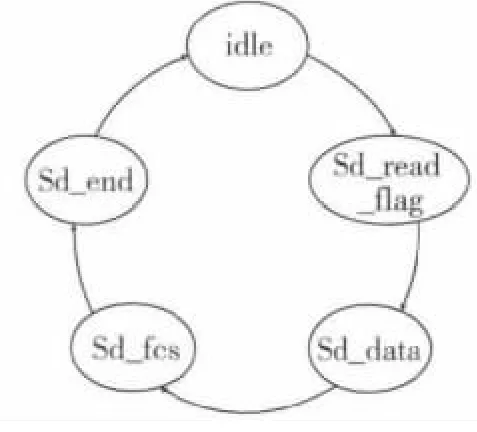

圖3 接收命令狀態轉移圖

系統復位后存儲器處于空閑狀態;當接收到8 bit數據時,先判斷該數據是否與本RAM地址相符合,如相符,說明該幀是發送到本RAM的,繼續接收數據,如不符合,則跳轉到結束狀態;接收到RAM地址,經過8個時鐘周期,判斷接收到的數據,若是“00001111”或者“11110000”,則將該命令保存到cmd_s,繼續下一步狀態跳轉,若為其他,則狀態機跳轉到結束狀態;命令接收完畢,再經過8個時鐘周期,把接收到的讀寫起始地址存到寄存器;如果是cmd_s是“00001111”,表示CPU寫入數據,此時狀態跳轉到接收寫數據長度;如果cmd_s是“11110000”,則表示CPU讀取數據,此時狀態跳轉到接收讀數據長度。

在接收寫數據長度狀態下,根據數據長度,接收來自CPU的存儲數據和4個字節的校驗數據,并返回一個校驗標識信號。如果數據接收正確,用“1”表示;否則用“0”表示,并跳轉到結束狀態。最后返回空閑狀態。在接收讀數據狀態下,接收要讀取的數據長度,最后接收數據結束并返回空閑狀態。

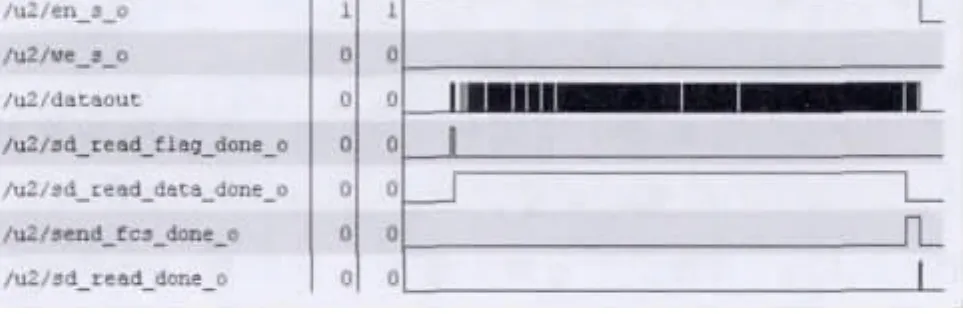

2.3 存儲器發送狀態轉移圖

復位后,存儲器為空閑狀態;依據發送數據幀格式,RAM存儲器先發送讀數據先導,之后發送從RAM內讀出的數據,發送過程中要對數據進行校驗計算,發送數據完畢,發送32位校驗值。最后發送結束,返回等待狀態。RAM存儲器發送讀數據狀態轉移見圖4。

3 驗證結果

3.1 測試結果

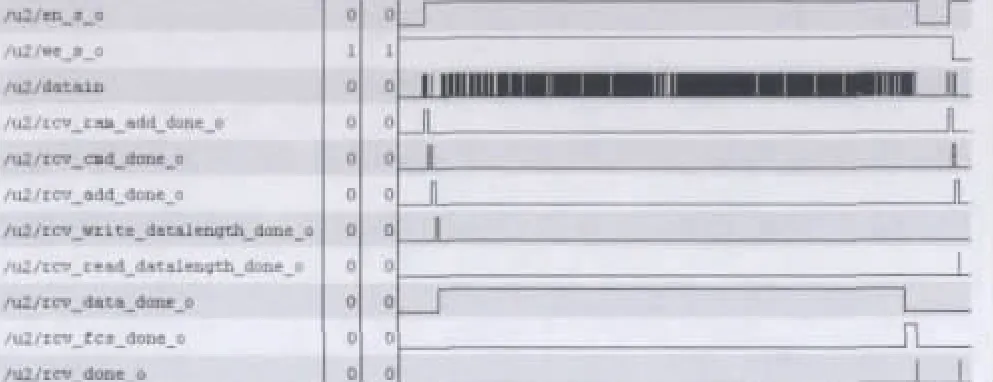

本文使用ISE在線邏輯分析儀ChipScope,采集RAM存儲器寫/讀操作,采集所用時鐘頻率為2.15 GHz,RAM存儲器數據寬度16,深度256。

圖5中,Datain是存儲器串行輸入端口得到的數據,接收到RAM地址后,與本RAM地址相符合,則將本RAM的使能置高,接收到命令為“0F”即向RAM寫入數據,因此將讀寫使能置高,接收到命令“F0”即從RAM讀出數據,因此將讀寫使能置低,其他均為標志位,為高電平時代表成功接收幀的各個字段,rcv_done_o=1,標志著存儲器接收正確。

圖6中,Dataout是存儲器向CPU發送的串行數據,依照幀格式定義,該端口先發送讀先導“10101010”,之后發送讀出的數據以及32位校驗值。sd_read_done_out=1,表示從RAM中讀出的數據正確。

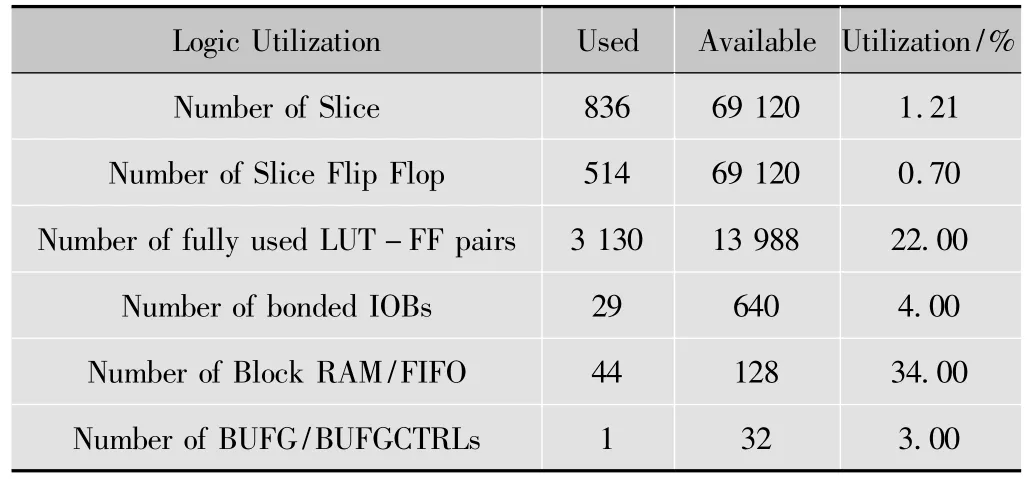

3.2 資源使用情況和分析對比

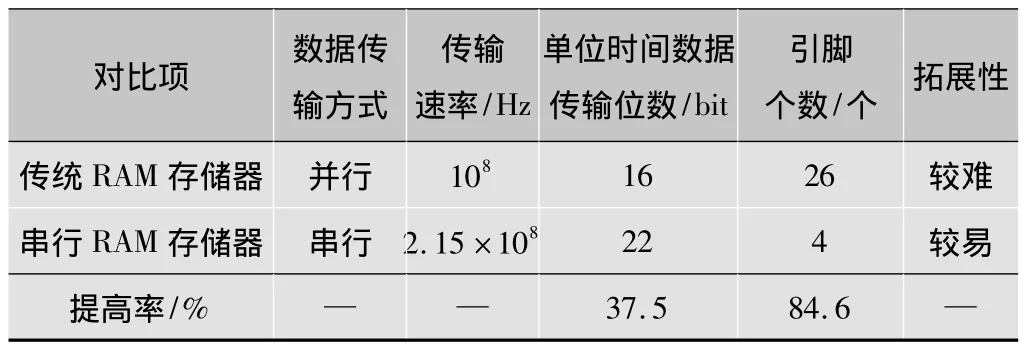

由綜合報告可知該RAM存儲器資源占用情況,具體如表3。由Utilization一列可以清晰地看到,本文所設計的串行接口RAM存儲器使用資源比較少,引腳個數節約了84.6%,非常有效地降低了SoC的空間和成本,同時數據傳輸速率提高了37.5%。表4中對比了傳統RAM存儲器與本文所設計的單向串行只寫總線型RAM存儲器,具體如下。

圖5 RAM存儲器接收CPU發送的寫和讀命令結果(截圖)

圖6 RAM控制器向CPU發送串行數據結果(截圖)

表3 串行接口RAM存儲器使用資源的情況

表4 RAM存儲器對比

4 總結與展望

本文應用Xilinx Vertex-5開發板上豐富的FPGA資源,利用其高速工作特性,以及內嵌的單端口RAM IP核,構造并實現了具有單向串行只寫總線接口的RAM存儲器,并采用LVDS技術抑制高速信號間干擾,大大提高了數據的傳輸速率與可靠性。通過下載驗證,該存儲器的設計方案正確,靈活性很高,可以很方便地進行擴展[8]。RAM為可配置軟IP核,其存儲容量可以根據需要定制。嵌入式CPU可以通過增加RAM節點個數形成存儲陣列來達到擴展緩存容量的目的,因此在單位時間內可以訪問更大的內存,處理更大規模的數據,從而加快其訪問內存的速度。FPGA具有硬件邏輯可編程性、大容量、高速、內嵌存儲陣列等特點,使其特別適合于高速數據采集、精確時序邏輯等場合的應用[3]。

[1]李慶誠,劉嘉欣,張金.嵌入式系統原理[M].北京:北京航空航天大學出版社,2008.

[2]秦鴻剛,劉京科,吳迪.基于FPGA的雙口RAM實現及應用[J].電子設計工程,2010(2):72-74.

[3]馬玉春,宋瀚濤.串行通信協議的研究及應用[J].計算機應用研究,2004(4):228-232.

[4]Virtex-5 FPGA Data Sheet[EB/OL].[2013-10-30].http://wenku.baidu.com/link?url=AeiuPIDTJ-8xJnQ4wQuxAvDetu7FPi5qtsOFPw JUcXmGaCp85oy1RL8xEV2jqlgMS7tSkMuYL2bwc_RYy8XAkhF_jeYeM-hQwbqV8GQF-NSS.

[5]封彥彪,劉興春.基于Xilinx FPGA的時鐘管理設計與實現[J].電子測量技術,2010(10):52-55.

[6]張友,鄭世寶.一種SPI濾波器設計中的并行CRC算法[J].電視技術,2005,29(3):28-30.

[7]杜瑞,張偉功,鄧哲,等.新型總線中并行CRC算法的設計與實現[J].計算機工程與設計,2013(1):131-135.

[8]田豐,鄧建國,李巍,等.SDRAM控制器的設計與VHDL實現[J].電子技術應用,2005(2):74-79.