非對(duì)稱式多諧振蕩器的M ultisim仿真

馬敬敏

(渤海大學(xué) 實(shí)驗(yàn)管理中心,遼寧 錦州 121000)

Multisim10是一種專門(mén)用于電路仿真和設(shè)計(jì)的軟件之一[[1-3],是NI公司下屬的ElectroNIcsWorkbench Group推出的以Windows為基礎(chǔ)的仿真工具,是目前最為流行的EDA軟件之一。該軟件基于PC平臺(tái),采用圖形操作界面虛擬仿真了一個(gè)與實(shí)際情況非常相似的電子電路實(shí)驗(yàn)工作臺(tái),用軟件的方法虛擬電子元器件、虛擬電子儀器和儀表,實(shí)現(xiàn)了“軟件即元器件”、“軟件即儀器”,幾乎可以完成在實(shí)驗(yàn)室進(jìn)行的所有電子電路實(shí)驗(yàn),已被廣泛地應(yīng)用于電子電路分析、設(shè)計(jì)、仿真等項(xiàng)工作中。

多諧振蕩器是一種自激振蕩器,它沒(méi)有穩(wěn)定的輸出狀態(tài),有兩個(gè)暫穩(wěn)態(tài),不需要外加觸發(fā)信號(hào),工作時(shí)自動(dòng)在兩個(gè)暫穩(wěn)態(tài)之間轉(zhuǎn)換,產(chǎn)生矩形脈沖。多諧振蕩器的電路有多種構(gòu)成形式,文中以CMOS非對(duì)稱式多諧振蕩器為例,介紹用Multisim10虛擬仿真工作波形的技術(shù)。

1 CMOS非對(duì)稱式多諧振蕩器的工作原理

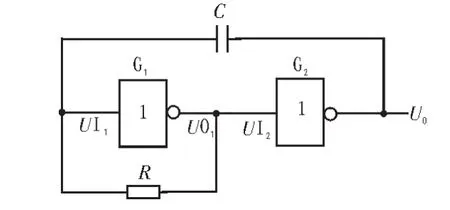

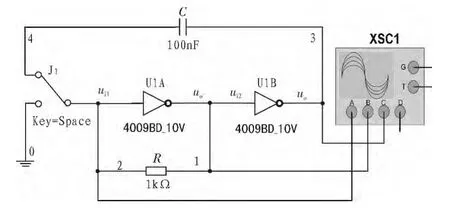

用CMOS非門(mén)及R、C元件組成的非對(duì)稱式多諧振蕩器如圖1所示。電容C為G2門(mén)、G1門(mén)之間的耦合電容,電阻R為G1門(mén)設(shè)置了靜態(tài)工作點(diǎn)。

圖1 CMOS非對(duì)稱式多諧振蕩器Fig.1 CMOSasymmetricmultivibrator

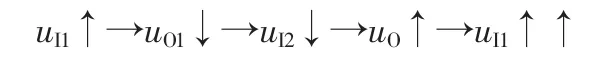

電路處于暫穩(wěn)態(tài)I時(shí),uO1=VDD、uO≈0 V,電容 C被充電,充電回路為 uO1→R→C→uO,使 uI1上升,當(dāng) uI1↑≥UTH時(shí)產(chǎn)生

正反饋過(guò)程,使電路轉(zhuǎn)入uO1≈0 V、uO=VDD的暫穩(wěn)態(tài)II。

電路處于暫穩(wěn)態(tài)II時(shí),電容C反充電,充電回路為uO→C→R→uO1,使 uI1下降,當(dāng) uI1↓<UTH時(shí)產(chǎn)生

正反饋過(guò)程,使電路轉(zhuǎn)入暫穩(wěn)態(tài)I。

電路在暫穩(wěn)態(tài)I、暫穩(wěn)態(tài)II之間自動(dòng)轉(zhuǎn)換,在輸出端得到矩形脈沖波形。

振蕩周期為

2 仿真電路存在的問(wèn)題

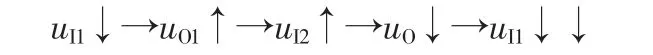

按圖1所示電路構(gòu)建仿真電路并用示波器顯示uO1、uO2及uO的波形 ,仿真分析電路的工作過(guò)程時(shí),出現(xiàn)不能正常工作的現(xiàn)象,仿真波形如圖2所示,由上至下分別為uI1、uO1(uI2)、uO的波形。

圖2 非對(duì)稱式多諧振蕩器的錯(cuò)誤仿真波形Fig.2 The incorrect simulated workingwave of asymmetric multivibrator

由圖2波形可看出,電路沒(méi)有正常工作、沒(méi)有形成振蕩。

查找分析原因如下。

Multisim10軟件中的設(shè)置是,器件從0輸出狀態(tài)開(kāi)始仿真,因此按圖1所示電路構(gòu)建仿真電路時(shí),按下仿真開(kāi)關(guān)后,uI1、uO1(uI2)、uO的信號(hào)按 000→111→000→111…的規(guī)律循環(huán)變化,解決的方法是,仿真時(shí)先使電路脫離系統(tǒng)設(shè)置的初始輸出狀態(tài)。

3 仿真方案設(shè)計(jì)

選擇以波形圖的形式描述CMOS非對(duì)稱式多諧振蕩器在兩個(gè)暫穩(wěn)態(tài)之間自動(dòng)轉(zhuǎn)換的工作過(guò)程。選擇用四蹤示波器顯示 G1門(mén)輸入端信號(hào) uI1、G1門(mén)輸出端信號(hào) uO1、G2門(mén)輸入端信號(hào)uI2、輸出信號(hào)uO的波形。

在Multisim10中構(gòu)建CMOS非對(duì)稱式多諧振蕩器工作波形仿真電路如圖3所示。非門(mén)4009BD從元件工具欄的CMOS器件庫(kù)中找出;電阻、電容從元件工具欄的基本元件庫(kù)找出;或使用快捷鍵Ctrl+W調(diào)出選用元件的對(duì)話框再找出相應(yīng)的元件;四蹤示波器XSC1從虛擬儀器欄中找出。

第一個(gè)門(mén)U1A的輸入端所接入的轉(zhuǎn)換開(kāi)關(guān)J1,其作用是使電路脫離系統(tǒng)設(shè)置的初始輸出狀態(tài)。仿真時(shí)先將開(kāi)關(guān)J1置于接地狀態(tài),電路對(duì)輸入的0信號(hào)進(jìn)行處理后便脫離設(shè)置的初始輸出狀態(tài),再將轉(zhuǎn)換開(kāi)關(guān)J1置于接輸出端構(gòu)成CMOS非對(duì)稱式多諧振蕩器,電路即可正常工作。

圖3 CMOS非對(duì)稱式多諧振蕩器的仿真電路Fig.3 The circuit of the CMOSasymmetricmultivibrator in simulation

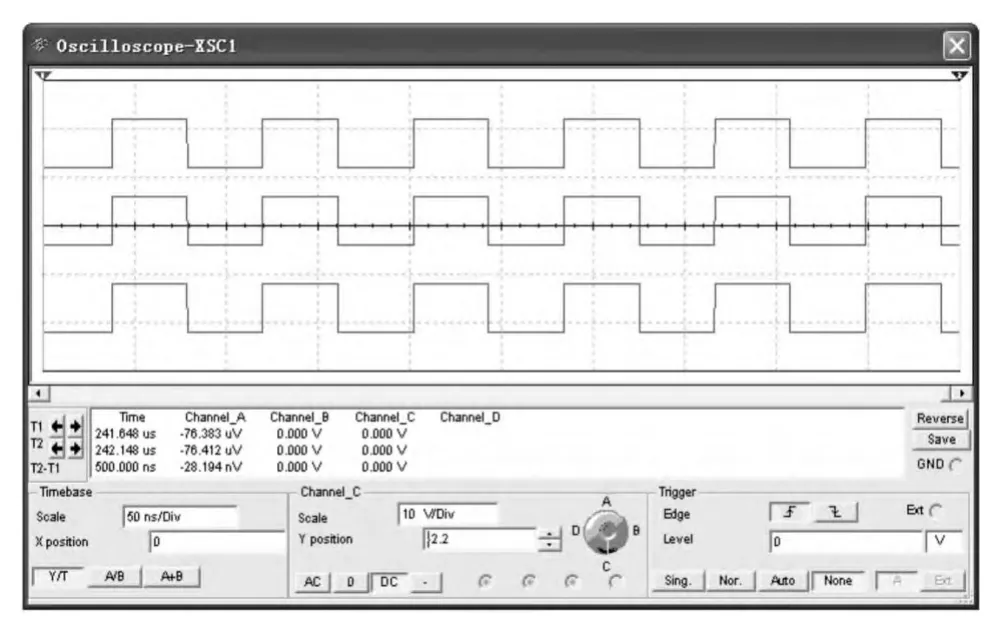

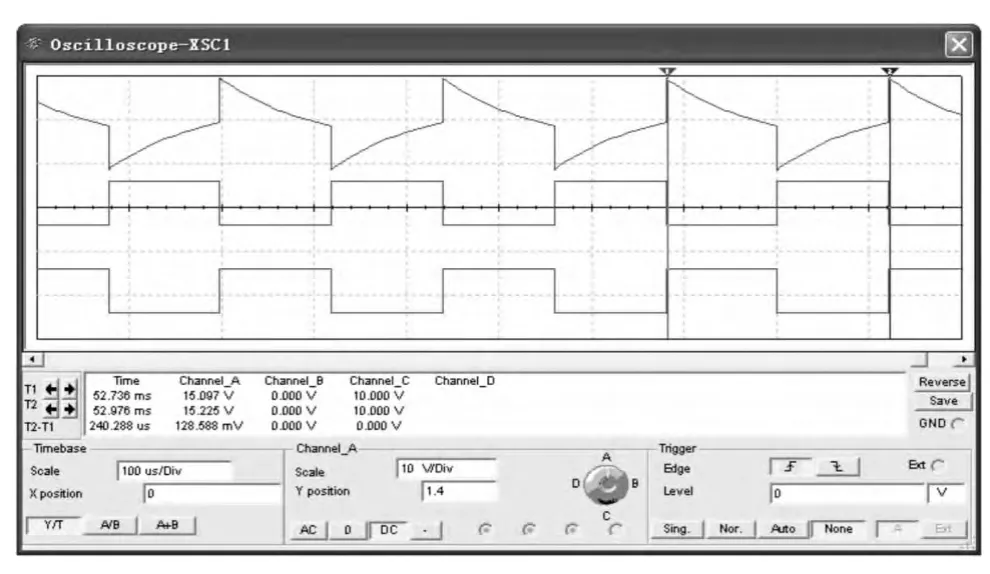

4 仿真運(yùn)行及結(jié)果

按下仿真開(kāi)關(guān),將轉(zhuǎn)換開(kāi)關(guān)J1先接地再接電容C構(gòu)成CMOS非對(duì)稱式多諧振蕩器,雙擊四蹤示波器的圖標(biāo)打開(kāi)面板圖顯示波形如圖4所示,在Channel區(qū)通過(guò)通道選擇旋鈕調(diào)整各通道波形的位置及顯示幅度,各通道均設(shè)置為DC耦合方式,在Time base區(qū)設(shè)置Scale的數(shù)值使顯示波形的個(gè)數(shù)合適,Y/T顯示方式。

圖4 四蹤示波器顯示的CMOS非對(duì)稱式多諧振蕩器仿真波形Fig.4 The simulated wave of the CMOSasymmetricmultibrator in four trace oscilloscope

圖 4 中,由上至下分別為 uI1、uO1(uI2)、uO的波形。 仿真波形反映了電容C充、放電控制多諧振蕩器自動(dòng)在兩個(gè)暫穩(wěn)態(tài)之間轉(zhuǎn)換的過(guò)程,并可確定振蕩周期T=240.288μs,和按式(1)計(jì)算所得理論值基本一致。

5 結(jié)束語(yǔ)

用硬件實(shí)驗(yàn)儀器對(duì)MOS非對(duì)稱式多諧振蕩器工作波形進(jìn)行測(cè)試,無(wú)法同時(shí)顯示 uI1、uO1(uI2)、uO3 個(gè)波形,用 Multisim軟件仿真解決了這一問(wèn)題。

CMOS非對(duì)稱式多諧振蕩器工作波形的Multisim仿真分析,可以直觀、定量描述電路的工作過(guò)程,Multisim仿真的問(wèn)題分析、方案改進(jìn),將有利于系統(tǒng)地研究Multisim的有效應(yīng)用方法。 所述方法具有實(shí)際應(yīng)用意義。

[1]閻石.數(shù)字電子技術(shù)基礎(chǔ)[M].北京:高等教育出版社,2006.

[2]任駿原,騰香,馬敬敏.數(shù)字電子技術(shù)實(shí)驗(yàn)[M].沈陽(yáng):東北大學(xué)出版社,2010.

[3]任駿原.用Multisim仿真軟件分析觸發(fā)器的狀態(tài)變化過(guò)程[J].實(shí)驗(yàn)科學(xué)與技術(shù),2011,9(1):53-56.REN Jun-yuan.The state transition analyzing of flip-flop by multisim[J].Experiment Science&Technology,2011,9(1):53-56.

[4]任駿原.Multisim在觸發(fā)器工作波形分析中的應(yīng)用[J].現(xiàn)代電子技術(shù),2010,33(15):184-186.REN Jun-yuan.An application of Multisim to the working wave analyzing of Flip-flop [J].Modern Electronics Technique,2010,33(15):184-186.

[5]任駿原.74LS161異步置零法構(gòu)成任意進(jìn)制計(jì)數(shù)器的Multisim仿真[J].電子設(shè)計(jì)工程,2011,19(14):135-137.REN Jun-yuan.Multisim simulation for modulo-N counter composed by 74LS161with asynchronous reset method[J].Electronic Design Engineering,2011,19(14):135-137.

[6]任駿原.RC橋式正弦波振蕩電路的輸出幅值分析[J].電子設(shè)計(jì)工程,2013,21(14):107-108.REN Jun-yuan.Study on the amplitude of RC-bridge oscillator[J].Electronic Design Engineering,2013,21(14):107-108.

[7]騰香.二進(jìn)制譯碼器邏輯功能的Multisim仿真方案[J].現(xiàn)代電子技術(shù),2010,33(20):11-13.TENG Xiang.Multisim simulation program of Binary decoder logic function[J].Modern Electronics Technique,2010,33(20):11-13.

[8]馬敬敏.基本RS觸發(fā)器工作狀態(tài)的Multisim仿真[J].電子設(shè)計(jì)工程,2011,19(17):24-26.MA Jing-min.Multisim simulation of basic RS flip-flop working conditions [J].Electronic Design Engineering,2011,19(14):24-26.