(7×7)奇偶校驗電路的EDA設(shè)計

嚴添明

(黎明職業(yè)大學(xué) 信息與電子工程學(xué)院, 福建 泉州 362000)

信道編碼技術(shù)是未來寬帶無線通信系統(tǒng)中的關(guān)鍵技術(shù)之一,在算法方面已經(jīng)有較深入的研究.LDPC(LowDensity Parity Check,低密度奇偶校驗)碼具有逼近Shannon限的性能,是信道編碼研究領(lǐng)域的一個熱點,是當前通信領(lǐng)域的熱門研究課題之一,也是當前性能最好的信道編碼之一,是第四代通信系統(tǒng)(4G)強有力的競爭者.文獻[1]研究了LDPC碼相關(guān)技術(shù)及其并行級聯(lián)構(gòu)造,設(shè)計了一種低復(fù)雜度的迭代終止準則——CMM準則,與其它迭代終止準則相比,CMM準則具有運算復(fù)雜度低、存儲空間占用量少等優(yōu)點.多進制(Nonbinary) LDPC碼是該領(lǐng)域中的新興分支,主要集中在碼字構(gòu)造、性能分析以及優(yōu)化算法等方面,具有廣闊的研究前景以及深遠的學(xué)術(shù)意義.文獻[2]提出一種基于搜索多進制LDPC碼最小碼距的性能分析方法,對多進制LDPC碼的特點進行了多項改進,提出一種基于優(yōu)化最小碼距上限的多進制QC-LDPC碼構(gòu)造方法.文獻[3]提出了串行多重級聯(lián)奇偶校驗碼或串并混合的多重級聯(lián)奇偶校驗碼,能夠獲得比卷積碼更佳的性能,編碼相當簡單,參數(shù)選取靈活,在譯碼復(fù)雜度很低情況下能夠取得接近香農(nóng)容量極限的性能.

通過網(wǎng)絡(luò)搜索有關(guān)奇偶校驗電路硬件設(shè)計方面的資料很少,文獻[4]利用Altera公司的Max+PlusⅡ集成設(shè)計環(huán)境完成了串行通信校驗八位時序奇偶校驗器的VHDL源代碼輸入和仿真測試.文獻[5]提出了多目標演化算法實現(xiàn)奇偶校驗器的電路自動設(shè)計,具有較少的運算量和較高的效率,能自動設(shè)計出使用邏輯門數(shù)更少、延時更小的奇偶校驗器.在較早的文獻[6-7]在信道編解碼技術(shù)中只提供算法,沒有具體電路,研究人員無法了解集成電路內(nèi)部核心電路結(jié)構(gòu),EDA設(shè)計困難.基于此,本文以邏輯電路為主體,繪制了 (7×7)奇偶校驗編碼解碼器硬件結(jié)構(gòu)框圖,設(shè)計出(7×7)奇偶校驗編碼器和解碼器邏輯電路原理圖和時序圖,為EDA設(shè)計(7×7)奇偶校驗編碼解碼器芯片提供邏輯電路依據(jù),為其他大規(guī)模電路設(shè)計提供參考.

1 奇偶校驗碼原理

水平垂直冗余校驗碼(Longitudinal-Vertical Redundancy Check)(7×7)奇偶校驗碼編碼時,每個字節(jié)通過行奇偶校驗發(fā)生器產(chǎn)生行檢驗位,與原來7bit信息碼一起構(gòu)成新的8bit碼,每7個字節(jié)通過列奇偶校驗發(fā)生器產(chǎn)生對應(yīng)7bit列檢驗位,組成7bit列檢驗字節(jié),列檢驗字節(jié)也通過奇偶校驗發(fā)生器產(chǎn)生行檢驗位,與列檢驗字節(jié)一起構(gòu)成8bit的檢驗字,最后由8×8bit組成一幀[6].一幀中信息碼為49bit,監(jiān)督碼為15bit,編碼效率為49÷64≈76.6%.

接收時,每行8bit字通過行奇偶校驗器產(chǎn)生8bit的行校驗字節(jié),每列8bit通過列奇偶校驗器產(chǎn)生8bit的列校驗字節(jié),當某行某列出現(xiàn)錯誤時,相應(yīng)的行和列的奇偶校驗結(jié)果為1,因此根據(jù)校驗字測試比特為1的行和列來判定錯誤的位置,并進行糾正[7].顯然,當存在2個或2個以上的數(shù)碼位出錯時,就無法判斷錯誤的位置,不能糾正.

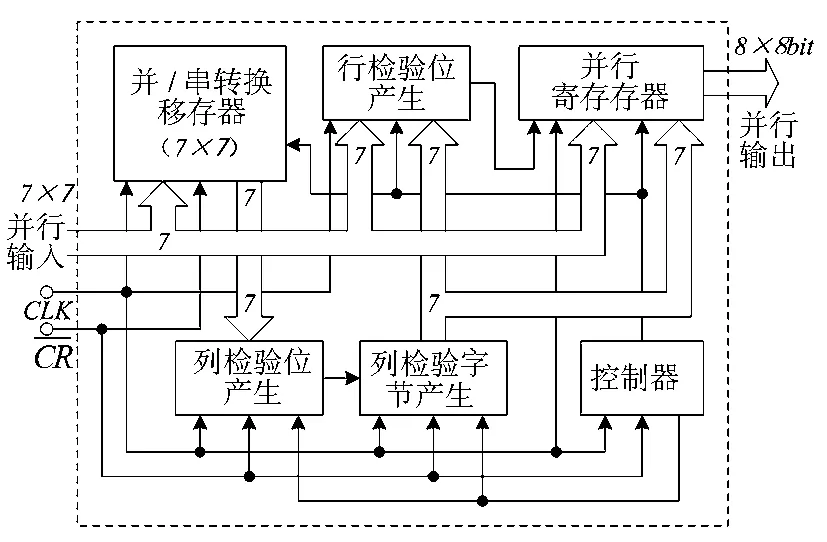

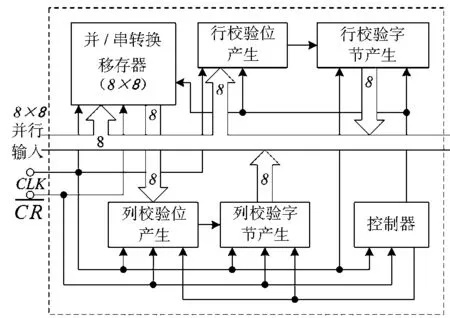

(7×7)奇偶校驗碼編碼器組成框圖(7×7)奇偶校驗碼解碼器組成框圖如圖1、圖2所示.

圖1 (7×7)奇偶校驗碼編碼器組成框圖

圖2 (7×7)奇偶校驗碼解碼器組成框圖

(7×7)奇偶校驗電路的EDA設(shè)計包括編碼器和解碼器的電路設(shè)計,因此要分別設(shè)計.

2 (7×7)奇偶校驗編碼器EDA設(shè)計

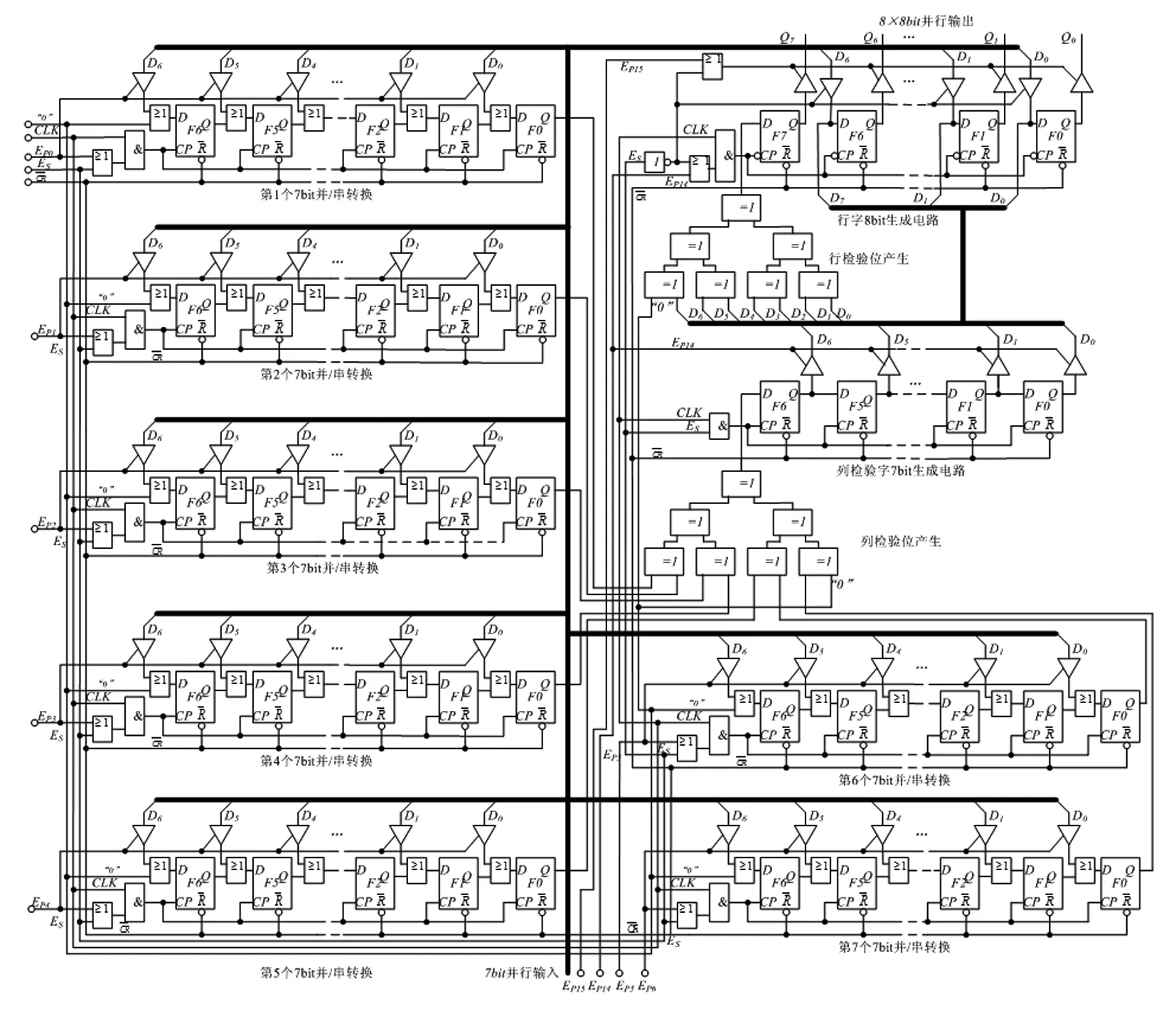

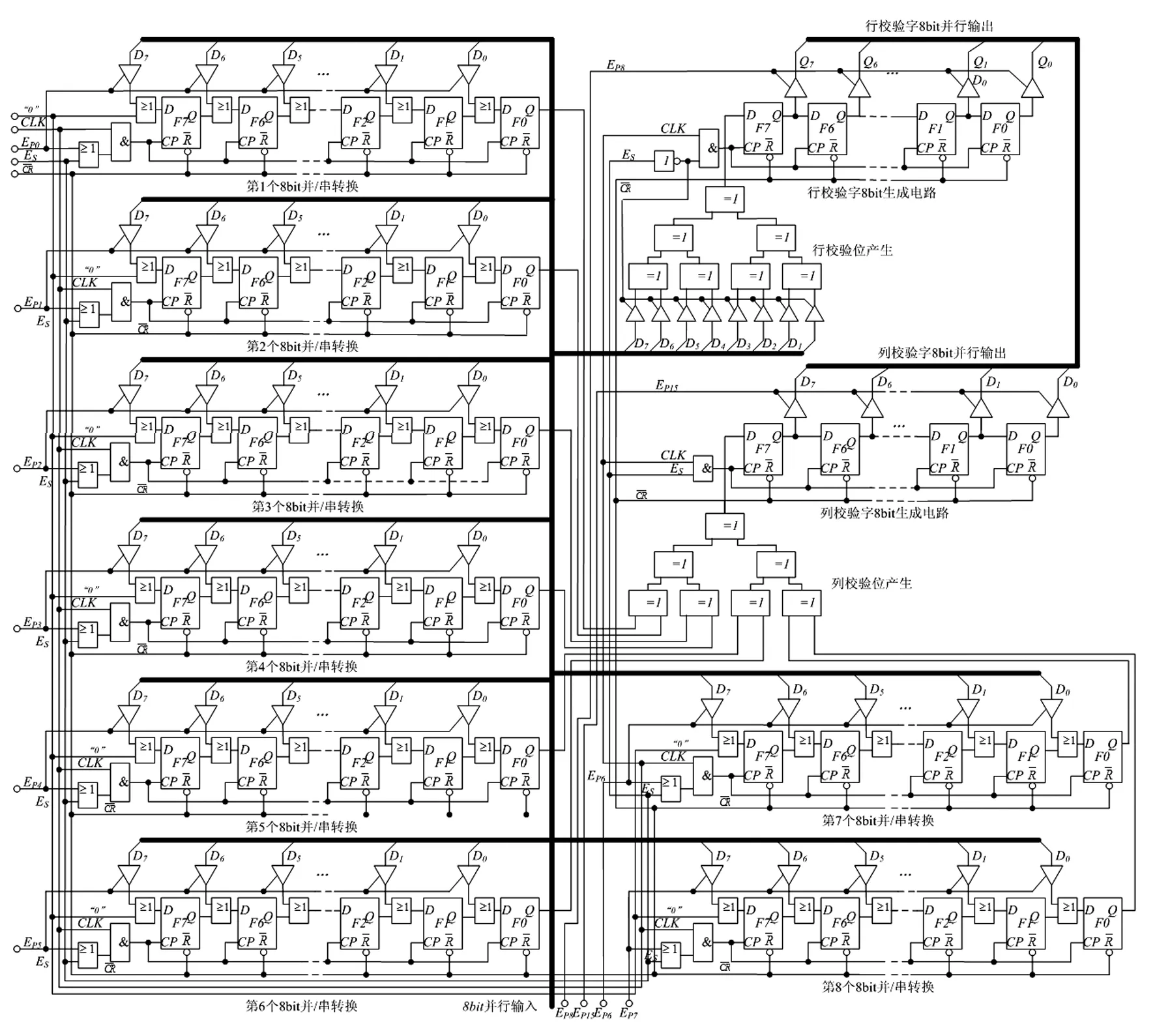

2.1 (7×7)奇偶校驗編碼原理圖設(shè)計

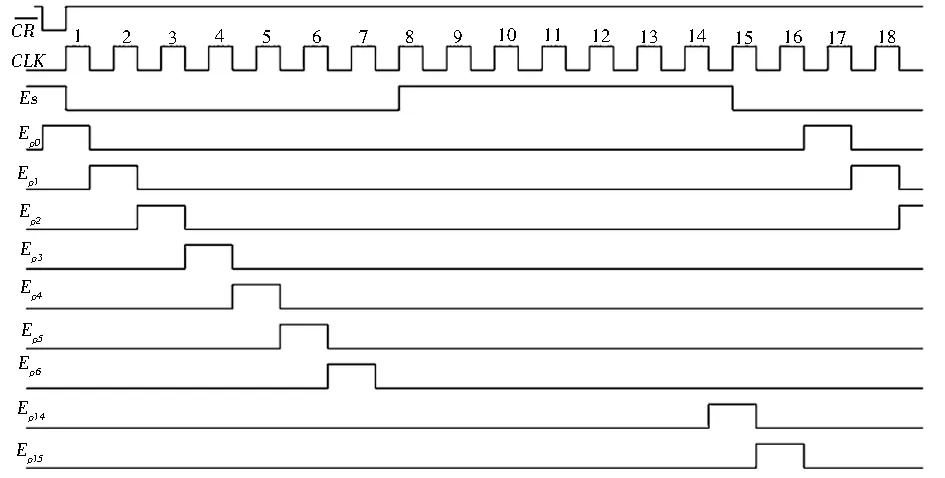

2.2 編碼器時序波形發(fā)生器的設(shè)計

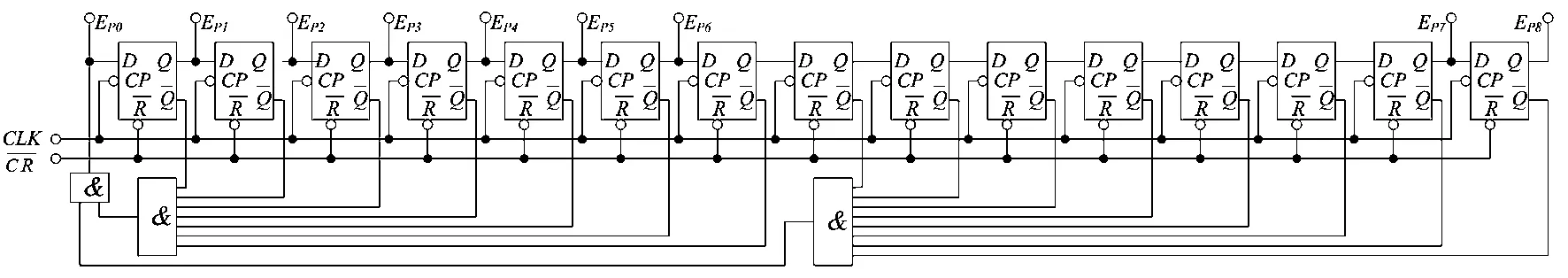

2.2.1 編碼器并行控制時序波形發(fā)生器原理圖

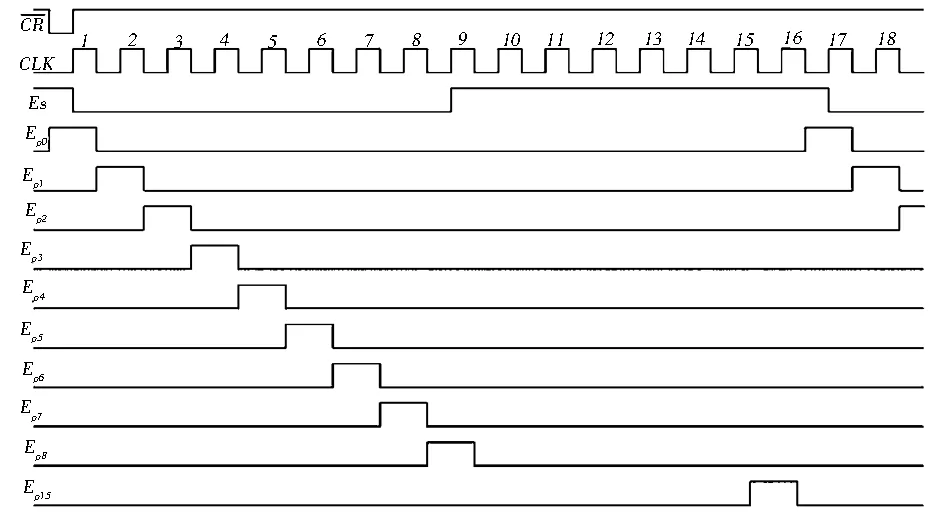

(7×7)奇偶校驗編碼器控制時序波形發(fā)生器原理圖如圖5所示.電路由15個D觸發(fā)器和1個二輸入端與門和2個八輸入端與門組成[8].系統(tǒng)復(fù)位后產(chǎn)生EP0節(jié)拍,控制第1個7bit信息碼在第1個CLK上升到達后并行鎖存產(chǎn)生第1行8bit碼組,第1個CLK下降沿到達后,并行輸出,結(jié)束EP0節(jié)拍產(chǎn)生EP1節(jié)拍,控制第2個7bit信息碼在第2個CLK上升到達后并行鎖存產(chǎn)生第2行8bit碼組,第2個CLK下降沿到達后,并行輸出,結(jié)束EP1節(jié)拍產(chǎn)生EP2節(jié)拍,……,第6個CLK下降沿到達后結(jié)束EP5產(chǎn)生EP6節(jié)拍,控制第7個7bit信息碼在第7個CLK上升到達后并行鎖存產(chǎn)生第7行8bit碼組,下降沿到達后,并行輸出.在第8個CLK到地第14個CLK期間逐位產(chǎn)生列檢驗碼移位寄存,到第15個CLK上升沿到后并行鎖存產(chǎn)生第8行8bit監(jiān)督碼組,下降沿達到后結(jié)束EP14節(jié)拍產(chǎn)生EP15節(jié)拍,控制8bit列監(jiān)督碼并行輸出,第16個CLK下降沿到后結(jié)束EP15節(jié)拍產(chǎn)生EP16節(jié)拍,開始新的一幀數(shù)據(jù)編碼.

2.2.2 編碼器串行移位控制信號Es產(chǎn)生電路的設(shè)計

圖3 (7×7)奇偶校驗編碼器原理圖

圖4 (7×7)奇偶校驗編碼器時序圖

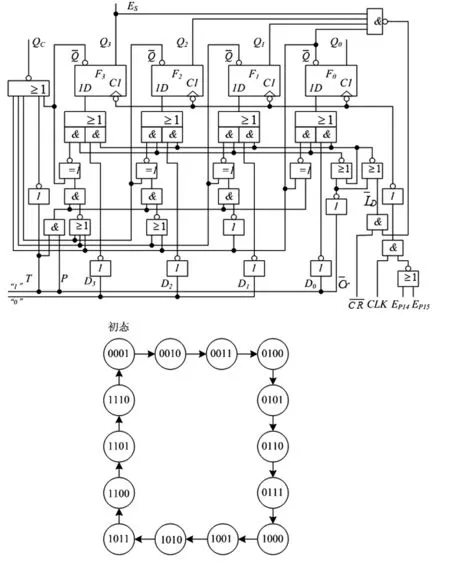

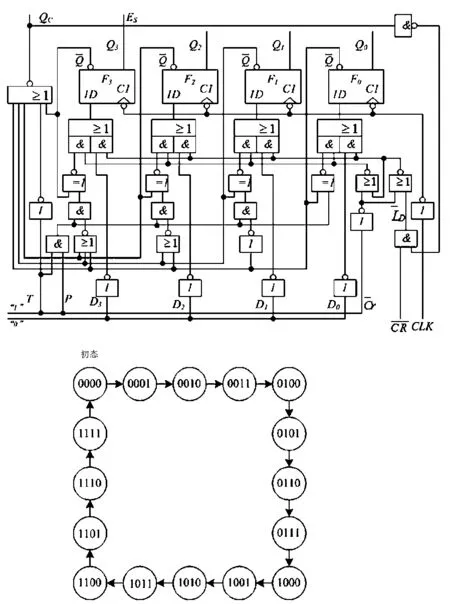

圖6為14進制計數(shù)電路原理圖及狀態(tài)轉(zhuǎn)換圖,由1個4位可預(yù)置清零加法計數(shù)器[9]、1個與非門、2個與門和1個或非門組成預(yù)置數(shù)置入計數(shù)器,系統(tǒng)復(fù)位后,初態(tài):Q3Q2Q1Q0=0001,Q3輸出低電平期間提供7個7bit信息碼逐一并行輸入到移位寄存器中,Q3輸出高電平期間提供7bit奇偶校驗碼移位控制信號.利用EP14、EP15高電平期間封鎖2個CLK計數(shù)脈沖,使Q3Q2Q1Q0=0001狀態(tài)保持3個CLK時鐘周期,實現(xiàn)了14進制計數(shù)的16分頻電路,將系統(tǒng)時鐘信號CLK信號16分頻,滿足串并行控制的時序要求.

圖5 (7×7)奇偶校驗編碼器控制時序波形發(fā)生器

圖6 16分頻器電路

2.3 (7×7)奇偶校驗編碼器仿真結(jié)果

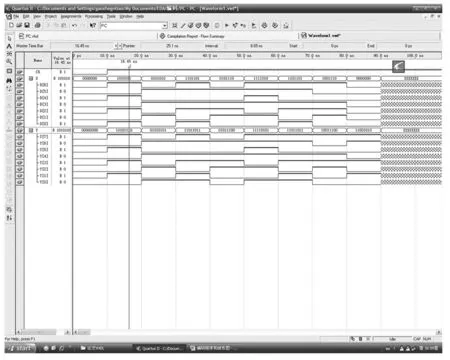

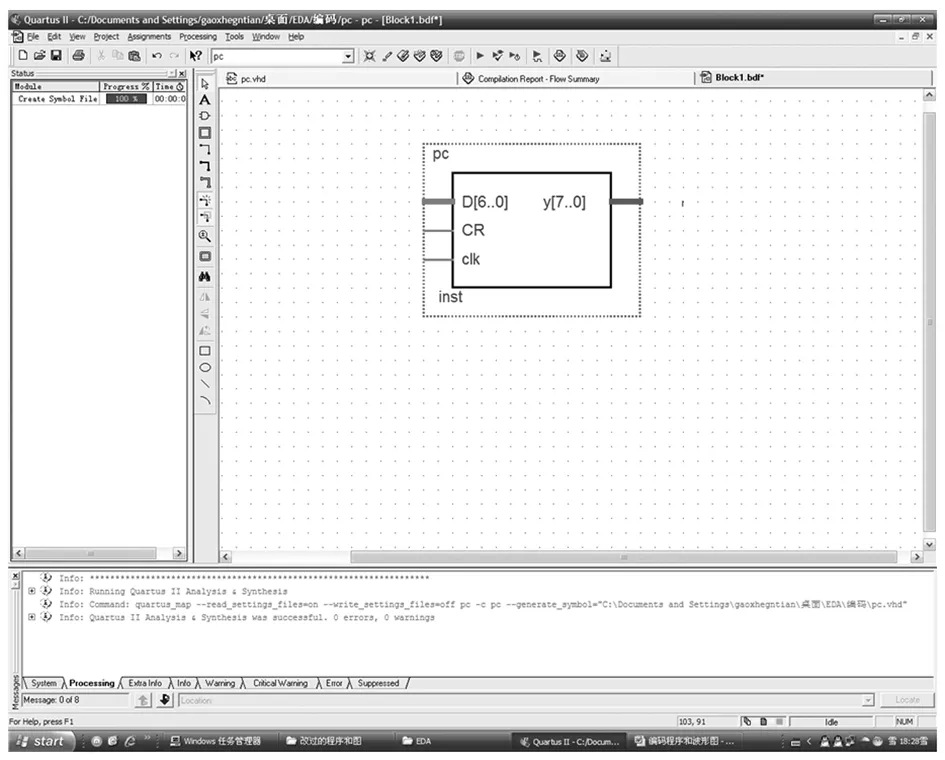

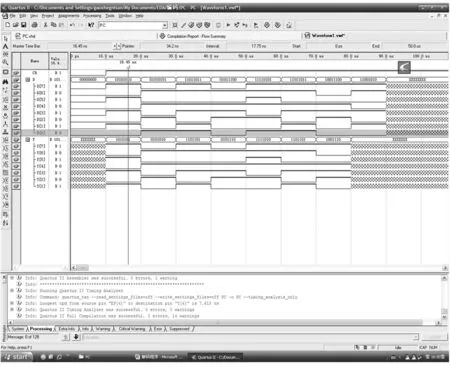

根據(jù)(7×7)奇偶校驗編碼器邏輯電路圖和相應(yīng)時序產(chǎn)生邏輯圖用VHDL硬件描述語言設(shè)計(7×7)奇偶校驗編碼器實體,描述系統(tǒng)外部接口信號[10],包括7bit×7輸入信息碼(D6、D5、…、D0)7個輸入端、系統(tǒng)復(fù)位(CR)輸入端、系統(tǒng)時鐘(CLK)輸入端、編碼輸出端(Y7、Y6、…、Y0);設(shè)計內(nèi)部的結(jié)構(gòu)和行為,建立輸入和輸出之間的邏輯關(guān)系.通過仿真實驗生成(7×7)奇偶校驗編碼器的仿真波形圖和芯片原理圖.

(7×7)奇偶校驗編碼器仿真波形圖如圖7所示.輸入一幀7bit×7,經(jīng)過奇偶校驗編碼器編碼后,每個字節(jié)變?yōu)?bit,其中前7bit為信息碼,最后一位為檢驗碼,有7個字節(jié),最后一個字節(jié)為列檢驗字節(jié),因此共有8個字節(jié),可用并行傳輸出去,也可用串行傳輸出去.

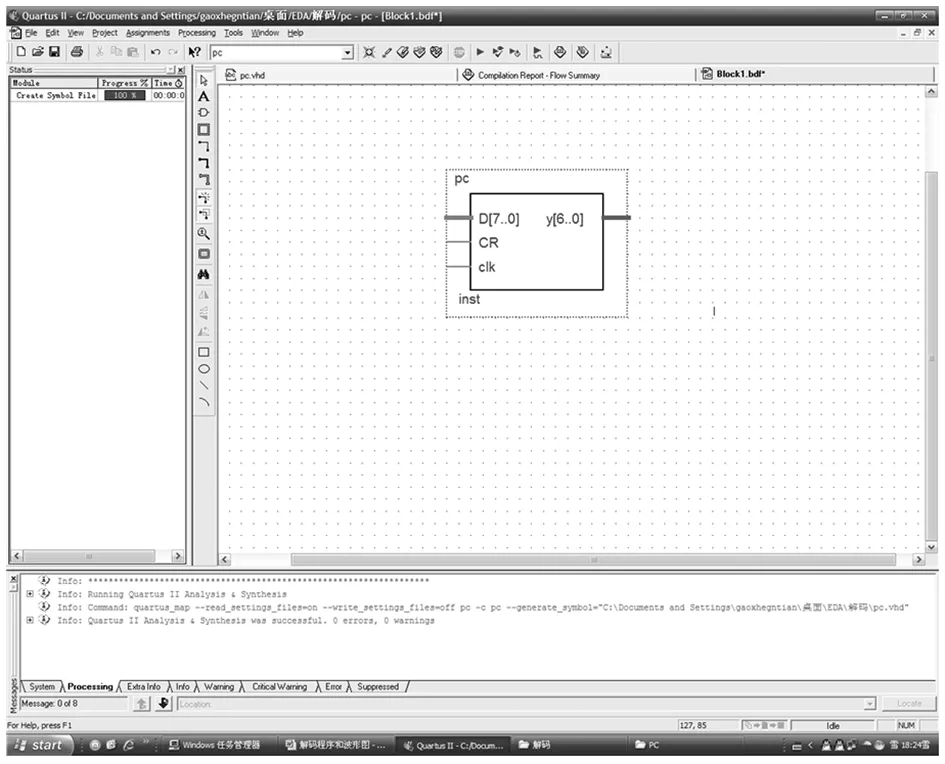

生成芯片原理引腳圖如圖8所示,共用17個引腳,分別是清零端CR,系統(tǒng)時鐘信號端CLK,7條并行數(shù)據(jù)輸入端,8條并行數(shù)據(jù)輸出端.

3 (7×7)奇偶校驗解碼器EDA設(shè)計

3.1 (7×7)奇偶校驗解碼原理

圖7 (7×7)奇偶校驗編碼器仿真波形圖

圖8 生成奇偶校驗編碼器芯片原理引腳圖

圖9 (7×7)奇偶校驗解碼器原理圖

圖10 (7×7)奇偶校驗解碼器時序圖

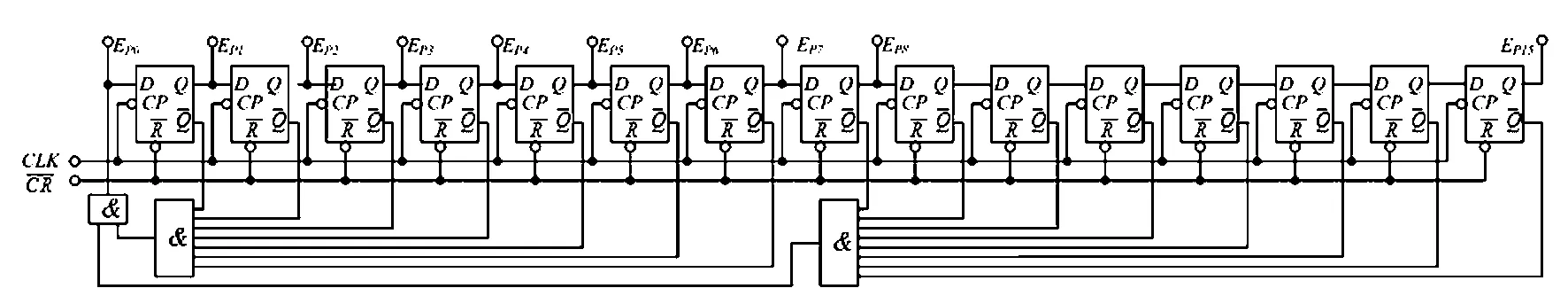

3.2 解碼器時序波形發(fā)生器的設(shè)計

(7×7)奇偶校驗解碼器時序波形發(fā)生器原理圖如圖11所示.工作原理與解碼器時序波形發(fā)生器相同,就不贅述.

串行Es控制信號的產(chǎn)生電路為16分頻的邏輯電路,其原理圖和狀態(tài)轉(zhuǎn)換如圖12所示,由1個4位可預(yù)置清零加法計數(shù)器、1個與非門、1個與門組成可預(yù)置數(shù)置入計數(shù)器,在正常計數(shù)過程中利用進位狀態(tài)進行反饋控制置數(shù)[11].

3.3 (7×7)奇偶校驗解碼器仿真結(jié)果

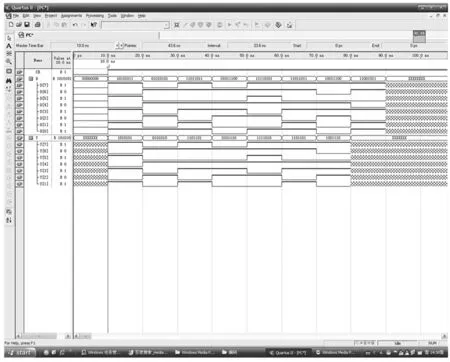

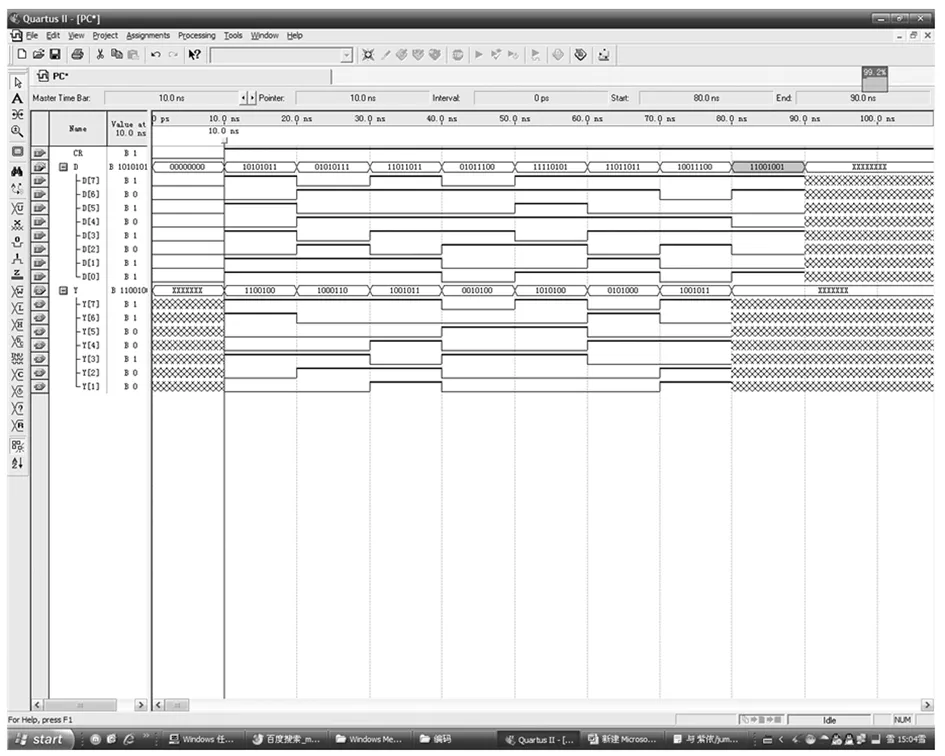

根據(jù)(7×7)奇偶校驗解碼器邏輯電路圖和相應(yīng)時序產(chǎn)生邏輯圖用VHDL硬件描述語言設(shè)計(7×7)奇偶校驗編碼器實體,描述系統(tǒng)外部接口信號,包括8bit×8輸入信息碼(D7、D6、D5、…、D0)7個輸入端、系統(tǒng)復(fù)位(CR)輸入端、系統(tǒng)時鐘(CLK)輸入端、解碼輸出端(Y6、Y5、…、Y0);設(shè)計內(nèi)部的結(jié)構(gòu)和行為,建立輸入和輸出之間的邏輯關(guān)系.通過仿真實驗生成(7×7)奇偶校驗編碼器的仿真波形圖和芯片原理圖.

當輸入信號沒有差錯時,奇偶校驗解碼器仿真波形圖如圖13所示.輸入一幀8bit×8,經(jīng)過奇偶校驗解碼器編碼后,每個字節(jié)變?yōu)?bit的信息碼,共有7個字節(jié).

當輸入信號錯一位碼時,跟原樣第1個字節(jié)第1位差錯,即是把第一個字節(jié)10101010改成10101011(校驗碼發(fā)生錯誤時),奇偶校驗解碼器仿真波形圖如圖14所示.每個字節(jié)變?yōu)?bit的信息碼,共有7個字節(jié),并且糾正過來了.

當發(fā)生兩個比特錯誤碼時,輸出變亂碼了(即把原來正確碼第一字節(jié)10101010改成10101011第二字節(jié)碼01010101改成01010111),則出現(xiàn)亂碼如圖15所示.

圖11 ( 7×7)奇偶校驗解碼器時序波形發(fā)生器

圖12 16分頻器

圖13 輸入信號沒有差錯,奇偶校驗解碼器仿真波形圖

圖14 輸入一位校驗碼差錯,奇偶校驗解碼器仿真波形圖

圖15 輸入兩位差錯,奇偶校驗解碼器仿真波形圖

圖16 生成奇偶校驗解碼芯片原理引腳圖

4 結(jié)束語

本文介紹了水平垂直冗余校驗碼(7×7)奇偶校驗碼的編碼器與解碼器邏輯電路的EDA設(shè)計,編碼時一幀中信息碼為49bit,監(jiān)督碼為15bit;解碼時,通過行奇偶校驗器產(chǎn)生每行1bit的8bit的行校驗字節(jié),通過列奇偶校驗器產(chǎn)生每列1bit的8bit列校驗字節(jié),當某行某列出現(xiàn)錯誤時,相應(yīng)的行和列的奇偶校驗結(jié)果為1,因此根據(jù)校驗子測試比特為1的行和列來判定錯誤的位置,并進行糾正.當存在2個或2個以上的數(shù)碼位出錯時,就無法判斷錯誤的位置,不能糾正.為了提高糾錯能力,可利用比特交織法使群誤碼變成離散的隨機誤碼,奇偶校驗器就可以糾錯,信號傳輸?shù)目煽啃詴蟠蟮靥岣撸虼嗽趯嶋H應(yīng)用中,都是結(jié)合交織技術(shù)對信號進行信道編碼處理.

水平垂直冗余校驗碼有很強的檢錯能力,冗余度不高,在ARQ系統(tǒng)中使用較多,用于計算機的通用同步/異步收發(fā)機UART/USRT.商用的編碼IC

片不多,有Motorola的MC6850、Intel公司的8251和ZILOG公司的UART型號Z80-SIO等.仿真結(jié)果表明,符合芯片設(shè)計要求,可以燒寫成芯片,把發(fā)送和接收封裝在同一芯片上實現(xiàn)雙工通信,提高信號處理速度.

[1] 李金根.低密度奇偶校驗碼的研究與設(shè)計[D].大連:大連海事大學(xué), 2008.

[2] 劉磊.多進制低密度奇偶校驗碼的研究[D].合肥:中國科學(xué)技術(shù)大學(xué), 2012.

[3] 孫麗,岳殿武.多重級聯(lián)奇偶校驗碼與卷積碼的性能比較[C]//2007通信理論與技術(shù)新發(fā)展——第十二屆全國青年通信學(xué)術(shù)會議論文集(下冊).北京:中國通信學(xué)會,2007.

[4] 曹永建,俎美杰.基于VHDL語言的8位時序奇偶校驗器的設(shè)計[J].科技信息,2006(1):155-156.

[5] 王平,曾三友,鄢靖豐,等.基于演化算法的奇偶校驗器自動設(shè)計[J].計算機應(yīng)用研究,2007(6):257-258,261.

[6] 張宗橙.糾錯編碼原理和應(yīng)用[M].北京:電子工業(yè)出版社.2003:30-31.

[7] 《電子天府》叢書編寫組.VCD視盤機精解[M].成都:電子科技出版社,1997:71.

[8] 張維廉.數(shù)字電子技術(shù)基礎(chǔ)[M].北京:高等教育出版社,1989:305-307.

[9] 宋樟林,陳道鐸,王小海.數(shù)字電子技術(shù)基本教程[M].杭州:浙江大學(xué)出版社,1995:165.

[10] 黃仁欣.EDA技術(shù)實用教程[M].北京:清華大學(xué)出版社,2006:17-18.

[11] 張友漢.數(shù)字電子技術(shù)基礎(chǔ)[M].北京:高等教育出版社,2002:111-113.