一種新型數字芯片測試儀的設計與實現

李天義 耿躍華 富坤 張梅芳

(河北工業大學計算機科學與軟件學院1,天津 300401;中國人民解放軍93642部隊2,河北 唐山 064000;河北工業大學電氣與自動化學院3,天津 300401)

一種新型數字芯片測試儀的設計與實現

李天義1,2耿躍華3富坤1張梅芳1

(河北工業大學計算機科學與軟件學院1,天津 300401;中國人民解放軍93642部隊2,河北 唐山 064000;河北工業大學電氣與自動化學院3,天津 300401)

針對傳統數字芯片測試設備檢測芯片固定、PC機軟件不可擴展、測試電路復雜等問題,設計了一種新型數字芯片測試儀。儀器設計為上位機和下位機兩部分,并著重突出了上位機的作用。對組成上位機的編譯模塊、數據管理模塊、SQLite數據庫、測試模塊和串口設置模塊進行了研究,同時對以PL2303芯片為主的串口通信模塊和以STC89C52為控制芯片的下位機電路進行了設計。系統能夠準確地檢測組合邏輯芯片、定位故障點,并能動態生成測試集、擴展可測組合邏輯芯片。

編譯功能 SQLite數據庫 芯片測試 測試集 結果集 故障檢測

0 引言

隨著電子技術的不斷發展,組合邏輯芯片被廣泛使用在數字系統研究中,因其反復使用、頻繁插拔等,極易出現故障。為及時檢測出問題芯片、提高芯片利用率,各大高校和實驗室紛紛推出自己的芯片測試儀器或設備[1-5]。這些測試儀器在一定程度上實現了對問題芯片進行檢測的目的。然而,這些測試儀器注重對芯片測試能力的設計,對適用范圍、交互能力沒有進行充分的考慮,主要體現在3個方面:一是將被測芯片的測試集提前寫入檢測系統中,導致被測芯片型號固定;二是忽略了上位機軟件的擴展開發,使得測試系統不能夠擴充被測芯片;三是通過撥碼開關來對芯片類型和型號進行選擇,增加了硬件電路的復雜度。本文引入軟件編程技術、數據庫技術等,將研究重點放在上位機的開發上,通過增加上位機的編譯模塊和SQLite輕型數據庫管理模塊,配合下位機相應的硬件電路,有效地解決了上述問題。

1 系統總體設計

1.1 測試原理分析

數字芯片測試儀的基本測試原理是:首先,根據被測試片的邏輯功能生成測試集和結果集;然后,利用硬件電路將測試集轉換成電平信號并加載到被測芯片的輸入引腳,而后讀取被測芯片的輸出電平信號;最后將采集到的輸出電平信號與結果集進行比對,判斷出被測芯片的完整性。

上述基本原理在實際應用過程中有2個突出問題需要解決。一是測試集和結果集的存放問題。每一芯片都有其對應的測試集和結果集,存儲測試集和結果集是需要空間開銷的。如果將測試集和結果集存放在下位機的硬件存儲設備中,會使得原本就有限的下位機存儲空間更為拮據,故本文將測試集和結果集存放在上位機中。二是被測數字芯片輸入輸出引腳的確立問題。每組數字芯片對其各自的引腳定義不一定相同,一些引腳是信息量輸入引腳,一些則是信息量輸出引腳,在測試開始之初便需要確立引腳的輸入輸出狀態性質。本文通過建立上位機和下位機的通信協議、通信協議來配置上位機所傳遞的數據。

1.2 系統設計

通過上述分析,將系統總體框架設計為上位機和下位機兩部分,如圖1所示。

①上位機軟件部分主要由編譯模塊、數據管理模塊、測試模塊、串口設置模塊以及SQLite數據庫構成,主要實現對被測芯片的選定、類型擴充以及通信設置等基本操作。

②下位機則由以PL2303芯片為主的通信模塊和以STC89C52芯片為控制芯片的檢測模塊配以外圍擴展電路組成,主要實現對芯片的測試信號加載以及測試結果捕捉等操作。

圖1 系統總體框架圖Fig.1 Framework of the whole system

系統工作時,上位機的測試模塊將被測芯片的測試集發送到下位機通信模塊。通信模塊接收測試集并發送測試信號到下位機測試模塊,由測試模塊產生激勵信號對被測芯片進行檢測,并采集被測芯片的輸出響應。檢測模塊將輸出響應發送到通信模塊,進而發送到上位機的測試模塊。測試模塊將反饋信息集與被測芯片結果集進行比對,從而判斷被測芯片的好壞。

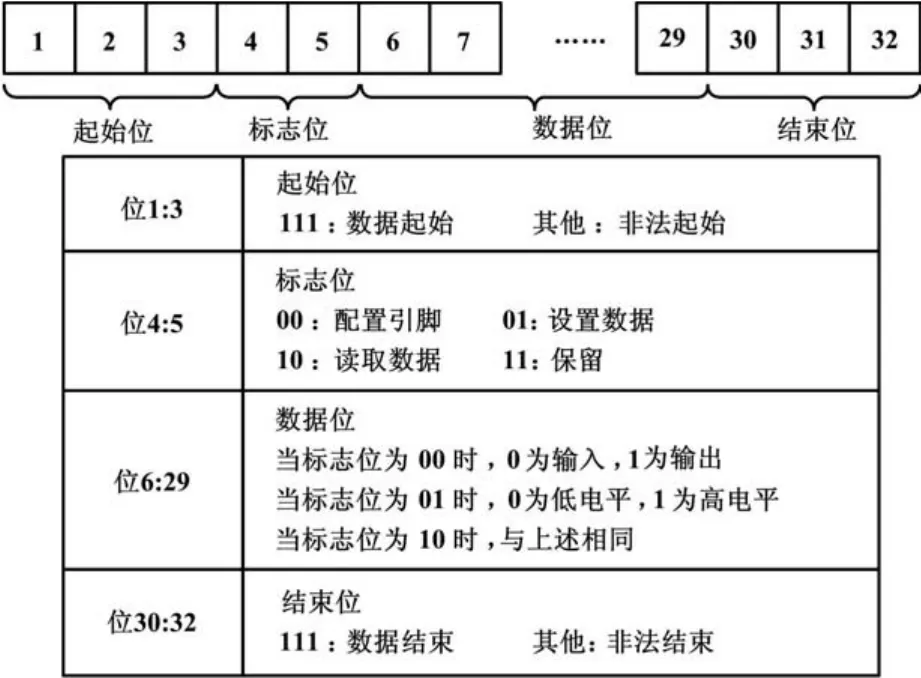

1.3 通信格式

系統中上位機與下位機的通信需要有特定的格式,使上位機和下位機程序的編寫遵循一定的依據,同時保證數據的完整性。上下位機間的數據通信協議具體格式如圖2所示。

圖2 上位機與下位機間的數據通信格式Fig.2 The data communication format between host computer and lower computer

上位機與下位機間的通信是通過數據幀來完成的。一個標準的數據幀分為32位:1~3位為起始位,標示該幀數據發送開始;4~5位為標志位,用于說明該幀數據的作用;6~29位為端口引腳的設置信息或輸入輸出情況;30~32位為結束位,標示該幀數據發送結束。

2 上位機設計實現

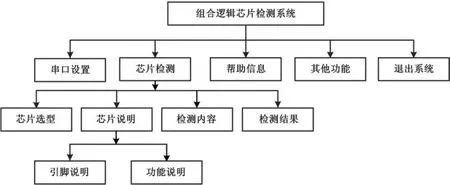

上位機軟件使用C#語言編寫,在Microsoft Visual Studio 2005環境和DotNetBar開發工具支持下完成。系統具有2個特色功能:一是能夠由芯片的功能表達式生成測試集和結果集,二是芯片的測試集和結果集能夠導出導入。這兩個功能均需要在上位機上實現。由此可見,上位機是整個系統的指令控制樞紐。為實現有效的測試數據傳輸和數據存儲管理,系統將上位機功能劃分為4個模塊。

上位機的軟件體系架構如圖3所示。

圖3 上位機軟件體系架構圖Fig.3 The architecture of the host computer software

①編譯模塊,為有效擴展測試芯片,需要為每一個新增加的被測試芯片添加相應的測試集,這里采用編譯模塊來完成該項工作。根據用戶輸入的芯片功能表達式,利用編譯原理的思想,結合測試集生成算法,生成被測芯片的測試集和結果集,并將測試集、結果集和被測芯片基本信息存入SQLite數據庫中。編譯模塊的作用是根據用戶要求動態添加新的芯片測試支持。

目前,常用的測試集生成算法有臨界通路法、D-算法、FAN算法[6-9]、布爾差分法[10]等,每種算法各有其優缺點。本文采用操作簡單、易于程序實現的臨界通路法為數字芯片的測試集生成算法。

②數據管理模塊,主要是通過操作SQLite數據庫,完成對已存在的數字芯片的類型、基本信息及其測試集和結果集進行查找、修改、刪除等基本數據操作。同時,數據管理模塊具備整體數據的導入和導出功能,通過該功能及時更新數據庫,從而滿足用戶對被測試芯片種類的及時更新要求。

開源的關系型數據庫SQLite數據庫,支持大部分標準SQL語言[11]。它沒有獨立的數據引擎,本文使用可視化管理工具SQLite Expert Pro v3.4.17實現對SQLite文件的構建和編寫。SQLite數據庫的數據文件是后綴名為.db的文件。該文件可直接由上位機程序通過API接口進行調用,實現對數據庫的存取操作。

③測試模塊,是直接實現對數字芯片進行檢測的關鍵模塊。測試模塊根據用戶對芯片類型的選擇信息,從SQLite數據庫中提取出對應芯片的測試集與結果集。同時,測試模塊根據串口設置模塊提供的串口傳輸信息,輸出測試集、接收反饋信息,與結果集進行對比分析得出測試結論并顯示。

④串口設置模塊,是設置串口通信的基本配置模塊,主要是針對不同的下位機對測試的串口設置要求不同而進行設計的。Microsoft Visual Studio 2005開發環境提供了SerialPort類,用于實現對串口通信的支持。通過初始化該類的實例即可完成對串口資源參數的配置。

除上述4個基本模塊功能外,為滿足用戶的多樣性要求,軟件還包括如工具軟件、快捷方式、日期提示、幫助文檔、主題風格等多種功能。

3 下位機設計實現

3.1 程序流程設計

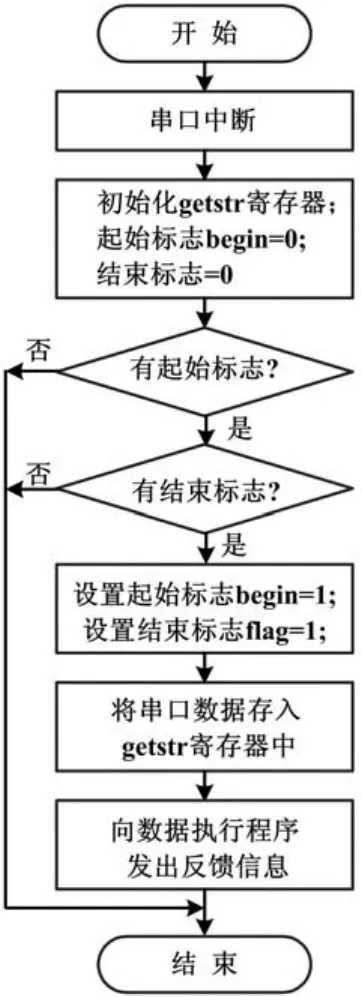

下位機是系統中具體的指令執行體,負責執行設備的控制指令,同時將測試結果反饋到上位機。下位機程序的執行主要分為串口中斷處理程序和數據執行程序兩部分。

①串口中斷處理程序流程圖如圖4所示。

圖4 串口中斷處理程序流程圖Fig.4 The flowchart of the serial port interrupt program

每當下位機接收到上位機通過串口發送的指令時,下位機執行串口中斷程序。根據定義的通信協議,中斷程序首先判斷該組數據的起始位和結束位是否完全正確。若不正確,則舍棄該組數據;若正確,則將數據存入getstr寄存器中,同時對數據執行程序進行信息反饋。

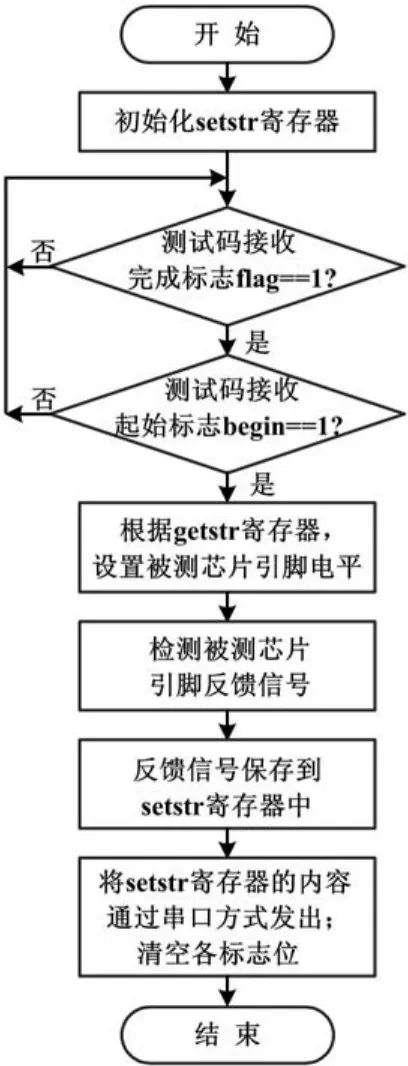

②下位機數據執行程序流程圖如圖5所示。

圖5 數據執行程序流程圖Fig.5 The flowchart of the data execution program

收到串口中斷程序的反饋信息后,數據執行程序開始執行,程序首先判斷flag和begin標志位是否均為1。若是,則執行測試程序;否則退出程序。

3.2 硬件設計

根據上述下位機程序的分析可知,下位機需要識別處理上位機的串口數據請求,需要有引腳與被測芯片進行連接,并具有一定的指令執行能力。經過仔細分析,系統采用STC89C52芯片作為下位機MCU,配合其他外部設備構成。下位機主要分為3個部分:USB轉串口通信、STC89C52芯片最小系統、40引腳芯片鎖緊座。

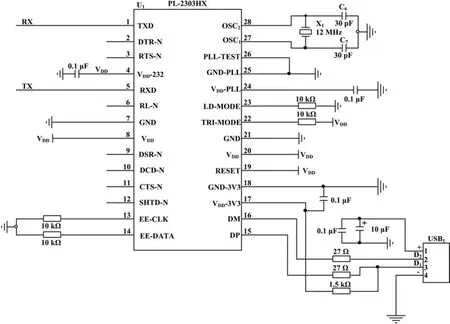

完成上位機與下位機進行通信數據解析的USB轉串口通信電路圖如圖6所示。模塊中采用PL2303芯片作為主要的數據處理芯片,另外包含驅動芯片工作的晶振電路以及穩壓電路等。PL2303芯片能夠將上位機提供的5 V電壓進行轉換,可提供3.3 V和5 V的兩種電壓型號,實現對不同工作電壓芯片的檢測。

圖6 USB轉串口通信電路圖Fig.6 The conversion circuit of USB to serial port communication

下位機工作的STC89C52最小系統電路由晶振電路、開關復位電路等構成。為使芯片的P1引腳能夠正常工作,將P1引腳進行上拉,上拉電阻為10 kΩ。

系統通過40引腳芯片鎖緊座,將被測芯片與STC89C52的3組(P0、P1、P2)I/O口連接。由于被測芯片的最后一個引腳為VCC,因此本設計將最后一個引腳直接接電源,并通過STC89C52的P1.0引腳選擇是連接3.3 V還是連接5 V電源。

3.3 硬件測試

硬件測試既是對所設計的下位機硬件電路的檢測也是對上位機軟件功能的檢驗。如對一片AT28C16芯片進行測試,需將芯片置放于芯片放置端,用鎖緊座將其固定供電,在上位機的“其他芯片”一欄中選擇AT28C16芯片,對其雙擊進行檢測,實現硬件檢測的目的。

4 結束語

本設計通過在上位機軟件中引入編譯功能和SQLite輕型數據庫,以及對相應下位機硬件電路的設計,實現了新型數字芯片測試儀。該儀器具有兩個突出特性:一是能夠檢測多種型號、不同功能的數字芯片;二是在系統中沒有該芯片的測試集和結果集的情況下,可以通過編譯功能實現測試集和結果集的生成,也可以通過數據導入的方式對測試芯片種類進行更新。因此,本設計具有更強的適應性和靈活性。

另外,本設計只能對24位以內引腳數目的芯片進行檢測,在下一步的研究中本設計會在鎖緊座引腳上引入數據鎖存器,通過分時加載測試信號的方式實現測試引腳數的擴充。

[1] 尹超平,張秉仁,趙吉祥.基于VIIS-EM平臺的虛擬數字集成電路測試儀的設計[J].電子技術應用,2013(5):89-92.

[2] 江麗君.數字集成電路故障模型研究及故障注入平臺設計[D].哈爾濱:哈爾濱工業大學,2013.

[3] 余波,李維,吳兆耀.新型數字IC測試儀的設計[J].成都師范學院學報,2013(7):122-124.

[4] 肖寶森.多功能數字芯片測試儀的設計與應用[J].實驗技術與管理,2010(12):133-136.

[5] 包本剛,劉坤,鄒帥,等.基于FPGA/DSP的數字芯片測試儀[J].儀表技術與傳感器,2010(7):42-45.

[6] 付鵬.專用電路測試方法的研究與實現[D].北京:北京理工大學,2011.

[7] 劉剛,黎放,狄鵬.基于融合算法的測試優化選擇問題研究[J].計算機科學,2013(S1):54-57.

[8] 王紅霞,潘紅兵,葉曉慧.多故障的測試序列問題研究[J].兵工學報,2011(12):1518-1523.

[9] 付欣,付帥.求解測試集優化問題[J].科技通報,2012(6):96-97,100.

[10] 孫昌愛,程慶順.基于故障的布爾表達式測試技術綜述[J].計算機科學,2013(3):16-23-40.

[11] 付蔚,劉謀黎,蔡林沁.智能家居系統嵌入式家庭服務器設計與實現[J].自動化與儀表,2013(4):37-40.

Design and Realization of a New Digital Chip Tester

Aiming at the problems of traditional digital chip test equipment,such as the tested chips are fixed,PC software cannot be extended,and the testing circuit is complex,etc.,a new digital chip tester has been designed.The design consists of two parts:the host computer,and the lower computer,and the role of the software in host computer is highlighted emphatically.The compositions of host computer,including compilation module,data management module,SQLite database,test module and serial port setup module are researched, in addition,the serial communication module based on PL2303 as the core,and the circuit with STC89C52 as control chip in lower computer are designed.The system can precisely detect combinational logic chip,positioning the fault point,and dynamically create test set,expand measurable combinational logic chip.

Compilation function SQLite database Chip test Test set Result set Fault detection

TP36

A

國家自然科學基金青年基金資助項目(編號:31100711);

河北省高等學校科學技術研究青年基金資助項目(編號:20111122)。

修改稿收到日期:2014-02-20。

李天義(1986-),男,現為河北工業大學計算機應用技術專業在讀碩士研究生;主要從事嵌入式系統的研究。