激光測距高速采集和處理電路的設計

周少杰

(華中光電技術研究所 武漢光電國家實驗室,湖北 武漢 430223)

激光測距高速采集和處理電路的設計

周少杰

(華中光電技術研究所 武漢光電國家實驗室,湖北 武漢 430223)

針對激光測距儀經典接收方法,設計了一種高速數字化采集電路。論文采用ADC+FPGA+DSP的設計方案,具有可調分辨率,最小分辨率可達0.3mv。詳細介紹了電路的具體設計方法。對脈沖信號進行測量,結果表明該方案可行。

激光測距;高速ADC

0 引言

激光測距儀是利用激光良好的準直性及非常小的發散角度來測量距離的一種儀器。但目前激光測距儀主要采用脈沖法進行測距,通過測量激光器發出光脈沖的時刻與光脈沖到達目標并由目標返回接收機的時間差計算出目標距離。準確判斷回波的到達時刻是測距的關鍵。激光測距儀經典信號檢測一直采用模擬電路來完成,主要利用分離元件和小規模集成電路對回波進行放大、濾波、閾值觸發、整形,在信噪比較大的條件下,能夠準確的判斷回波到達時刻,當信噪比變小時,由于噪聲的干擾,回波到達時刻就難以確定。近年來隨著高速AD、存儲器以及高速并行處理器的飛速發展,為回波檢測提供了新的方向。本文提出了一種激光測距的數字化方案,它采用以高速數字采集為核心的數字化接收電路,利用高速FPGA進行數據存儲和信號控制,最后利用DSP進行處理以實現回波信號檢測。

1 硬件電路設計

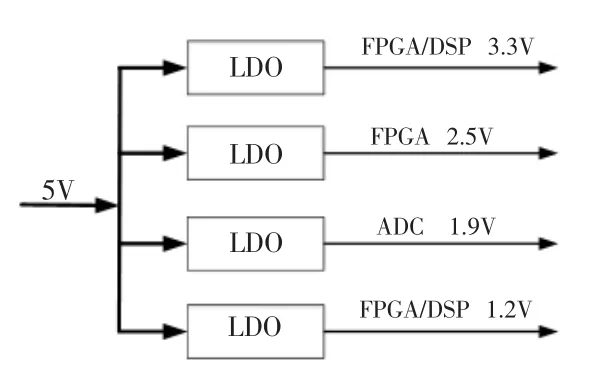

1.1 電源設計

高速電路板設計的一個重要的考慮就是電源的設計和網絡分配。電源的設計是選擇合適的電源芯片,滿足電壓強度、電壓紋波以及電流強度的要求。電源的網絡分配必須為高速電路板上各部分的電路提供一個低噪聲的電壓信號,包括VCC和接地匹配。電源分配網絡同時還得為電路板上所有產生或接受的信號提供一個信號回路,合理的分配電源層和地層可以有效減少電磁干擾。本電路采用5V供電,采用線性穩壓芯片對各電源單元供電,對重要電源增加濾波電路設計。布局布線方面,在避免使信號線跨電源平面的前提下,對電源層進行分割, 以減少成本。詳細設計參考如圖1所示。高速的模擬器件一般對數字噪聲很敏感,所以我們將模擬電源和數字電源分開,在電源的入口處接在一起。

圖1 電源設計框圖Fig.1 Block diagram of power supply

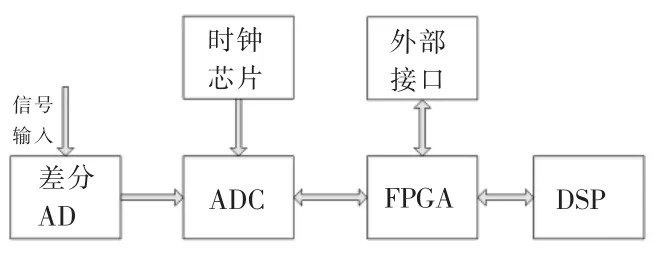

1.2電路設計

電路包括以下幾個部分:差分AD模塊、超低抖動時鐘芯片模塊、高速ADC模塊、FPGA,DSP以及所需要的外部接口模塊。電路組成框圖如圖2所示。差分AD和超低抖動時鐘芯片模塊組成了高速ADC模塊的信號輸入端,FPGA為高速ADC提供必要的初始化和控制信號,以及存儲ADC采樣數據。DSP通過EMIF總線讀取FPGA中的采樣數據后進行數據處理。

圖2 電路原理示意圖Fig.2 Schematic of circuit

由香農采樣定理可知,要想通過采樣信號對原始信號進行恢復,采樣頻率至少得是原始信號最高頻率的兩倍[1]。 目前激光回波信號為幾十到幾百ns,因此采樣頻率至少為MHz。通過比較,我們選擇ADC08D500作為高速采樣AD。它是一款高速雙通道低功耗CMOS模數轉換器,內置2個ADC電路,1.9V單電源供電,單個ADC電路工作時,功耗為1.4W[2]。單路最高采樣率為500 MSPS,8位的分辨率(250MHz信號輸入時,有效位為 7.5)。每個 ADC都有一個分解器,它可以將單個ADC的采樣值分兩路LVDS總線輸出,從而可以降低總線輸出頻率。ADC08D500提供了一種DES的工作模式,該模式利用其內置的2個ADC對一個通道的輸入模擬信號進行雙沿采樣,可以在500 MHz的時鐘頻率下實現1GSPS的采樣頻率。ADC08D500的輸入信號和時鐘要求采用LVDS電平標準。目前主要由兩種方式將單端信號變成差分信號:①單端放大器+變壓器;②采用專用全差分放大器。對于第一種方式,放大器要消耗大量功耗來使HD2變低,如果不用放大器,信號的增益調節受到限制(只能采用改變變壓比的方式),并且變壓器限制了低頻信號的通過。第二種方式消耗的功耗小,并且具有靈活的增益調節能力。通過比較,我們選用第2種方式,采用AD8138作為信號差分放大器。AD8138是一款低成本、差分或單端輸入至差分輸出放大器,通過電阻設置增益,能夠抑制諧波并降低輻射電磁干擾[3]。它具有較高的增益帶寬,當增益為 10時,-3dB帶寬為20MHz。對于微弱信號,可以方便利用合適的電阻來設置放大增益,來配合ADC08D500提高電路分辨率。高頻時鐘產生電路主要由以下三種方式:①以 PLL和VCO等分離器件構成;②以專有的集成芯片產生;③直接通過FPGA的內部鎖相環倍頻電路產生。通過比較,我們選用專有的集成芯片來作為時鐘發生器。CDCM61001是一款超低抖動的時鐘芯片,通過配置外部電阻,可以產生合適的差分時鐘頻率,最高可達600MHz, CDCM61001芯片尺寸僅有5×5mm,便于布線和放置[4]。

FPGA采用了StratixⅡ系列芯片,其IO端口支持LVDS信號,省去了電平轉換芯片,并且IO端口速度快,可以滿足ADC08D500的輸出采樣頻率要求。FPGA時序和邏輯控制部分包括ADC控制模塊、雙口RAM模塊、RAM寫控制模塊、DSP復位,對外接口。ADC控制模塊包括控制ADC的供電電源芯片的使能端和ADC的狀態設置。使FPGA在上電過程中ADC08D500的電源芯片處在禁止狀態。配置ADC08D500寄存器,選擇ADC的工作方式和模式,本設計中利用QuartusⅡ自帶的工具產生雙口RAM。寫控制模塊產生同步的地址信號和寫信號。對外接口包括數據和控制信號的輸入輸出。DSP復位模塊為DSP提供上電復位信號。FPGA內部各功能模塊如圖3所示。

圖3 FPGA內部各功能模塊示意圖Fig.3 Diagram of function blocks in FPGA

DSP采用C6000系列處理器,通過 EMIF總線與FPGA內部雙口RAM相連,激光測距算法的實現在DSP上完成。

1.3 PCB設計與實現

本系統PCB設計需要實現>=200MHz的模擬采樣信號,>=200MHz的高速時鐘,32bit差分高速數據信號以及多個電源信號的布局布線。在PCB設計中合理地布局器件,分開模擬電路和數字電路,盡量縮短高頻元器件之間的連線,同時兼顧信號完整性和高速信號的阻抗匹配[5]。基于上述考慮,PCB設計采用FR-4板材,8層板設計,各層信號依次為:頂層(信號)-地層-信號層-電源層-信號層-電源層-地層-底層(信號)。待采樣信號在頂層走線,32bit差分高速數據線對分布在頂層和底層。布局時使集成高速時鐘芯片盡量靠近ADC的時鐘輸入管腳,差分時鐘線布置在頂層。在PCB設計中,嚴格控制差分線對的長度和特征阻抗,使得數據線與時鐘線的誤差在100mil以內,差分阻抗100Ω[6]。由于電路中采用4種電源供電。因此在PCB設計時多種電源信號出現在同一平面層,在考慮信號完型性的前提下使各種不同的電源信號以分割的方式實現,防止電源信號對其他電路造成影響。

2 實驗測試

利用SignalTapⅡ觀察的結果如圖4所示。實驗中配置ADC08D500工作在非擴展模式,禁止ADCQ工作,使得ADCI單獨工作,利用外部電阻配置相應管腳,使得LVDS輸出電壓峰峰值為710mV,上升沿輸出,采用內部校驗,輸入電壓范圍為870mV。配置ADC8138的增益為2。通過選用合適的阻值,配置CDCM61001輸出為200MHz的LVDS時鐘信號。模擬輸入信號采用信號發生器產生的脈沖信號。脈沖信號頻率為1MHz,寬度為50ns,幅度為100mV。

從圖中可以看出本設計的電路可以滿足測量要求。

圖4 SignalTap II數據采集圖Fig.4 Diagram of data acquised by SignalTap II

3 結論

本文提出了一種對激光測距儀回波進行高速采樣的方案,通過實際測量,證明該方案能夠滿足測量要求。FPGA+ DSP的構造為采用靈活的信號處理方法提供了便利。

[1]Charles L.Philips,等.信號、系統和變換[M].機械工業出版社,2006.

[2]TEXAS INSTRUMENTS.ADC08D500 Datasheet.

[3]TEXAS INSTRUMENTS.AD8138 Datasheet.

[4]ANALOG DEVICES.CDCM61001 Datasheet.

[5]阮瓊,廖紅華.高速電路板的信號完整性設計與仿真[J].湖北民族學院學報(自然科學版),2010.

[6]張健楠,鮑丹,劉婷婷.差分線對在高速PCB設計中的應用[J].新特器件應用,2011.

High Speed Acquisition and Processing Circuit for Digital Laser Range Finding

ZHOU Shao-Jie

(Huazhong Institute of Electro-optics,Wuhan National Laboratory for Optoelectronics,Wuhan Hubei 430223,China)

Against traditional echo acquisition in laser distance finding,a circuit to sample echo in high speed is introduced.In the cicuit,An ADC+FPGA+DSP mode is used..It has a flexible dissolution,which has a very slow value 0.3mv.The design is discussed in detail,a measurement of pulses with frequencies 5K Hz and pulse width 50ns shows that this circuit is practicable.

laser distance finding;high speed ADC

TP274

:Adoi:10.3969/j.issn.1002-6673.2014.03.050

1002-6673(2014)03-132-03

2014-03-09

周少杰,男,工程師。主要研究方向:數字電路設計與信號處理。