基于C8051F500的SPI接口研究

夏 琳,鄭大勇

(1.中國電子科技集團公司第四十七研究所,沈陽110032;2.工業(yè)和信息化部電子第五研究所,廣州510610)

基于C8051F500的SPI接口研究

夏 琳1,鄭大勇2

(1.中國電子科技集團公司第四十七研究所,沈陽110032;2.工業(yè)和信息化部電子第五研究所,廣州510610)

主要介紹了C8051F500中的SPI(Serial Perripheral Interface)接口,尤其是對SPI0CKR時鐘速率控制寄存器、SPI0CFG配置寄存器、SPI0CN控制寄存器、SPI0DAT數(shù)據(jù)寄存器、Shift Register移位寄存器的結(jié)構(gòu)和功能進行了詳細介紹,并深入研究了SPI接口的通信過程。通過仿真,驗證了主機與從機之間的數(shù)據(jù)傳輸以及各個寄存器的功能。

SPI接口;配置寄存器;控制寄存器;數(shù)據(jù)寄存器;移位寄存器

1 引 言

SPI(Serial Perripheral Interface)串行外圍設(shè)備接口,是Motorola公司推出的同步串行接口技術(shù),是一種靈活的、全雙工,同步的串行通信總線。SPI可以作為主機和從機方式工作,具有三線和四線工作模式,在同一SPI總線上可支持多個主機和從機間的通信。從機選擇信號NSS可被設(shè)置為輸入以選擇工作在從機方式的SPI,以避免兩個以上主機同時進行數(shù)據(jù)傳輸時發(fā)生 SPI沖突。SPI在C8051F500芯片上只占用了四個引腳實現(xiàn)數(shù)據(jù)傳輸,節(jié)約了芯片的引腳數(shù)目,節(jié)省了布局空間,簡單易用。

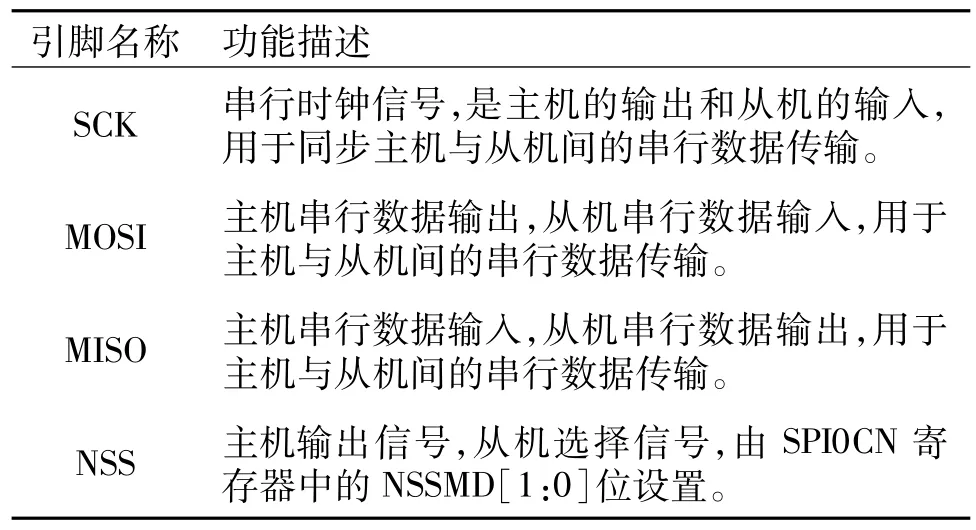

SPI通信結(jié)構(gòu)是一個環(huán)形總線結(jié)構(gòu),由串行時鐘信號SCK、串行數(shù)據(jù)MOSI和串行數(shù)據(jù)MISO、從機選擇信號NSS構(gòu)成,其時序簡單,主要是在串行時鐘信號SCK的控制下,兩個雙向移位寄存器進行數(shù)據(jù)交換。其引腳功能描述見表1。

2 SPI接口結(jié)構(gòu)

C8051F500中的增強型SPI結(jié)構(gòu)如圖1所示,主要由SPI0CKR時鐘速率控制寄存器、SPI0CFG配置寄存器、SPI0CN控制寄存器、SPI0DAT數(shù)據(jù)寄存器、Shift Register移位寄存器和相關(guān)控制電路組成。

表1 引腳功能描述

2.1 SPI0CKR時鐘速率控制寄存器

SPI0CKR是一個8位的時鐘速率控制寄存器,當(dāng)SPI被配置成主機工作方式時,由該寄存器控制輸出的串行時鐘SCK頻率。串行時鐘SCK頻率是從系統(tǒng)時鐘(SYSCLK)分頻得到的,由以下公式進行計算可得出,其中SYSCLK是系統(tǒng)時鐘,SPI0CKR[7:0]是SPI0CKR寄存器中的8位數(shù)值。

圖1 SPI接口結(jié)構(gòu)圖

2.2 SPI0CFG配置寄存器

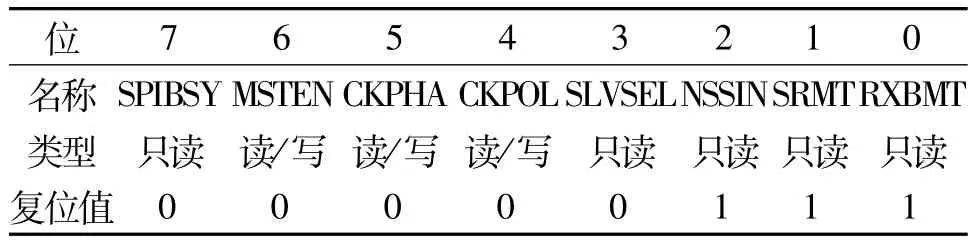

可以通過SPI0CFG配置寄存器對SPI串行時鐘的極性和相位以及主從工作方式進行設(shè)置,其組成如表2所示。

表2 SPI0CFG配置寄存器

每一位的功能如下:

·Bit7-SPIBSY:SPI工作繁忙標(biāo)志,當(dāng)SPI傳輸正在進行時(主/從機),該位被置1;

·Bit6-MSTEN:主機工作方式允許位,0表示禁止主機工作方式,1表示允許主機工作方式;

·Bit5-CKPHA:SPI時鐘相位配置,0表示在時鐘SCK周期的第一個邊沿進行數(shù)據(jù)采樣,1表示在時鐘SCK周期的第二個邊沿進行數(shù)據(jù)采樣;

·Bit4-CKPOL:SPI時鐘極性配置,0表示在空閑時時鐘SCK為低電平,1表示在空閑時時鐘SCK為高電平;

Bit3-SLVSEL:從機選擇標(biāo)志位,當(dāng)NSS引腳為低電平時,該位被置1,表示SPI是被選中的從器件;當(dāng)NSS引腳為高電平時,該位被清0,表示SPI是未被選中的從器件;

·Bit2-NSSIN:NSS引腳輸入的瞬間值;

·Bit1-SRMT:移位寄存器空標(biāo)志位(從機模式有效),當(dāng)所有數(shù)據(jù)都被移入/移出移位寄存器,并沒有新數(shù)據(jù)從緩沖器讀出/寫入時,該位被置1;當(dāng)數(shù)據(jù)從發(fā)送緩沖器傳送到移位寄存器或時鐘SCK發(fā)生變化時,該位被清0;主機工作方式時,該位為1;

·Bit0-RXBMT:接收緩沖器空標(biāo)志位,當(dāng)接收緩沖器中的數(shù)據(jù)被讀出且沒有新的數(shù)據(jù)時,該位被置1;如果接收緩沖器中有新數(shù)據(jù)未被讀出,則該位被清0;主機工作方式時,該位為1;

通過上述的功能簡介可以看出,SPI數(shù)據(jù)傳輸模式被設(shè)置成CPOL=1和CPHA=1時,在一個SCK時鐘周期內(nèi),每個單獨的SPI都能以全雙工方式,同時發(fā)送和接收一位數(shù)據(jù)。因此,SPI總線的頻率越快,時鐘周期越短,則SPI間數(shù)據(jù)交換的速率就越快。

2.3 SPI0CN控制寄存器

通過SPI0CN控制寄存器可以查看一些標(biāo)志和設(shè)置SPI三/四線通信模式,主要是用到SPIF這個標(biāo)志位,接收完成和發(fā)送完成都會置位這個標(biāo)志,進入中斷服務(wù)程序。其組成如表3所示。

表3 SPI0CN控制寄存器

每一位的功能如下:

·Bit7-SPIF:SPI中斷標(biāo)志位,在數(shù)據(jù)傳輸結(jié)束后,該位由硬件置1;如果中斷允許,該位置1將會使CPU轉(zhuǎn)到SPI中斷服務(wù)程序。該位不能被硬件自動清0,必須用軟件清0。

·Bit6-WCOL:寫沖突標(biāo)志位,該位由硬件置1,并產(chǎn)生一個SPI中斷,表示在數(shù)據(jù)傳送期間對SPI數(shù)據(jù)寄存器進行了寫操作。該位不能被硬件自動清0,必須用軟件清0。

·Bit5-MODF:方式錯誤標(biāo)志位,當(dāng)檢測到主機工作方式?jīng)_突時,該位由硬件置1;該位不能被硬件自動清0,必須用軟件清0。

·Bit4-RXOVRN:接收溢出標(biāo)志位,當(dāng)前傳輸?shù)淖詈笠晃灰岩迫隨PI移位寄存器,而接收緩沖器中仍保存著前一次傳輸未被讀取的數(shù)據(jù)時,該位由硬件置1,并產(chǎn)生一個中斷。該位不能被硬件自動清0,必須用軟件清0。

·Bit3/2-NSSMD[1:0]:選擇模式位,通過該兩位選擇NSS工作方式:00表示三線主/從機工作方式,NSS信號不連接到端口引腳;01表示四線從機或多主機工作方式,NSS是輸入引腳;1X表示四線單主機工作方式,NSS是一個輸出引腳。

·Bit1-TXBMT:發(fā)送緩沖器空標(biāo)志位,當(dāng)新數(shù)據(jù)被寫入發(fā)送緩沖器時,該位被清0;當(dāng)發(fā)送緩沖器中的數(shù)據(jù)被傳送到移位寄存器時,該位被置1,表示可以向發(fā)送緩沖器寫入新的數(shù)據(jù)。

·Bit0-SPIEN:SPI使能位,1表示SPI允許,0表示SPI禁止;

2.4 SPI0DAT數(shù)據(jù)寄存器

SPI0DAT是一個8位的可讀寫數(shù)據(jù)寄存器,用于發(fā)送和接收SPI數(shù)據(jù)。在主機工作方式下,向SPI0DAT寫入數(shù)據(jù)時,數(shù)據(jù)被放到發(fā)送緩沖器中并啟動發(fā)送,讀SPI0DAT返回接收緩沖器的數(shù)據(jù)。

寫數(shù)據(jù)是將數(shù)據(jù)傳輸?shù)桨l(fā)送緩沖器中,通過移位寄存器將發(fā)送緩沖器中的數(shù)據(jù)串行發(fā)送出去;讀數(shù)據(jù)是將移位寄存器接收到的串行數(shù)據(jù)傳輸?shù)浇邮站彌_器中。

2.5 ShiftRegister移位寄存器

Shift Register是SPI內(nèi)部的8位移位寄存器,它的主要作用是根據(jù)SPI時鐘信號狀態(tài),往接收/發(fā)送緩沖器里移入/移出數(shù)據(jù)。

3 SPI功能驗證

結(jié)合仿真,對主、從機之間的數(shù)據(jù)傳輸進行驗證,深入了解SPI的通信方式。

3.1 SPI仿真驗證

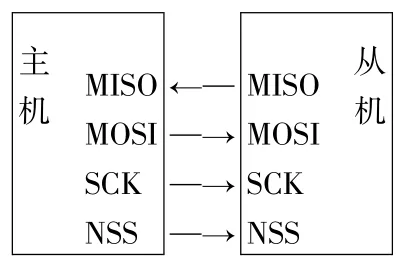

利用仿真軟件,以四線主/從機工作方式為例,SPI主從機數(shù)據(jù)傳輸仿真驗證環(huán)境如圖2所示。

圖2 仿真驗證圖

基于C8051F500的SPI主機初始化程序:

MOV A7,#0FH;//SFRPAGE=0F頁;

MOV A4,#0DH;//將端口設(shè)置為輸出推挽方式;

MOV E1,#04H;//交叉開關(guān)中允許SPI;

MOV C7,#40H;//交叉開關(guān)允許、I/O端口弱上拉;

MOV A7,#00H;//SFRPAGE=00頁;

MOV A1,#40H;//SPI主機模式;

CKPHA=0;

CKPOL=0;

MOV F8,#0DH;//SPI四線主機模式;SPI允許;

MOV A2,#17H;//SYSCLK=24MHz,fSCK=500KHz;

MOV A3,#AAH;//向主機SPI0DAT寫入數(shù)據(jù)AAH;

基于C8051F500的SPI從機初始化程序:

MOV A7,#0FH;//SFRPAGE=0F頁;

MOV A4,#0DH;//將端口設(shè)置為輸出推挽方式;

MOV E1,#04H;//交叉開關(guān)中允許SPI;

MOV C7,#40H;//交叉開關(guān)允許、I/O端口弱上拉;

MOV A7,#00H;//SFRPAGE=00頁;

MOV A1,#00H;//SPI從機模式;

CKPHA=0;

CKPOL=0;

MOV F8,#05H;//SPI四線從機模式;SPI允許;

3.2 SPI主機工作方式

SPI總線上的所有數(shù)據(jù)傳輸都由SPI主機啟動。通過將主機允許標(biāo)志位MSTEN(SPI0CN.6)置1,將SPI置于主機工作方式。當(dāng)處于主機工作方式時,向SPI數(shù)據(jù)寄存器(SPI0DAT)寫入一個數(shù)據(jù)字節(jié)時是寫發(fā)送緩沖器。如果SPI移位寄存器為空,發(fā)送緩沖器中的數(shù)據(jù)字節(jié)被傳送到移位寄存器,數(shù)據(jù)傳輸開始。SPI主機立即在MOSI線上串行移出數(shù)據(jù),同時在SCK上提供串行時鐘。在傳輸結(jié)束后SPIF(SPIOCN.7)標(biāo)志位被置為邏輯1。如果中斷被允許,在SPIF標(biāo)志置位時將產(chǎn)生一個中斷請求。在全雙工操作中,當(dāng)SPI主機在MOSI線向從器件發(fā)送數(shù)據(jù)時,被尋址的SPI從機可以同時在MISO線上向主機發(fā)送其移位寄存器中的內(nèi)容。因此,SPIF標(biāo)志既作為發(fā)送完成標(biāo)志又作為接收數(shù)據(jù)準(zhǔn)備好標(biāo)志。從從機接收的數(shù)據(jù)字節(jié)以MSB在先的形式傳送到主器件的移位寄存器。當(dāng)一個數(shù)據(jù)字節(jié)被完全移入移位寄存器時,便被傳送到接收緩沖器,處理器通過讀SPIODAT來讀該緩沖器。

3.3 SPI從機工作方式

當(dāng)SPI被使能而未被配置為主機時,它將作為SPI從機工作。作為從機,由主機控制串行時鐘SCK,從MOSI移入數(shù)據(jù),從MISO引腳移出數(shù)據(jù)。SPI邏輯中的位計數(shù)器對SCK邊沿計數(shù)。

當(dāng)8位數(shù)據(jù)經(jīng)過移位寄存器后,SPIF標(biāo)志位被置為邏輯1,接收到的字節(jié)傳送到接收緩沖器中。通過讀數(shù)據(jù)寄存器SPI0DAT來讀取接收緩沖器中的數(shù)據(jù)。從機不能啟動數(shù)據(jù)傳送,通過寫數(shù)據(jù)寄存器SPI0DAT來預(yù)裝要發(fā)送給主機的數(shù)據(jù)到移位寄存器。寫往SPI0DAT的數(shù)據(jù)是雙緩沖的,首先被放在發(fā)送緩沖器,如果移位寄存器為空,發(fā)送緩沖器中的數(shù)據(jù)會立即被傳送到移位寄存器。當(dāng)移位寄存器中己經(jīng)有數(shù)據(jù)時,SPI將在下一次(或當(dāng)前)SPI傳輸?shù)淖詈笠粋€SCK邊沿過去后再將發(fā)送緩沖器內(nèi)的數(shù)據(jù)裝入移位寄存器。

在從機檢測到第一個SCK邊沿后,移位寄存器中的數(shù)據(jù)被鎖定。在第一個SCK邊沿之后寫入SPI0DAT的數(shù)據(jù)被保持在發(fā)送鎖存器中,直到當(dāng)前傳輸結(jié)束。

4 結(jié)束語

結(jié)合仿真驗證對C8051F500中的SPI接口進行了深入研究,詳細了解了主機與從機之間的數(shù)據(jù)傳輸過程。如今,SPI串行接口主要應(yīng)用在EEPROM、Flash、實時時鐘(RTC)、數(shù)模轉(zhuǎn)換器(ADC)、數(shù)字信號處理器(DSP)以及數(shù)字信號解碼器等器件中。它在芯片中只占四個引腳,用來完成控制以及數(shù)據(jù)傳輸,具有簡單易用的特性,現(xiàn)在越來越多的芯片上都集成了SPI技術(shù)。

[1]李剛,林凌.與8051兼容的共性能、高速單片機-C8051FXXX[M].北京:北京航空航天大學(xué)出版社,2002.

[2]潘琢金,施國君.C8051FXXX高速SOC單片機原理及應(yīng)用[M].北京:北京航空航天大學(xué)出版社,2002.

[3]張毅剛,彭喜源.MCS-51單片機應(yīng)用設(shè)計[M].哈爾濱:哈爾濱工業(yè)大學(xué)出版社,2003.

Study of SPIBased on C8051F500

XIA Lin1,ZHENG Da-yong2

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.CEPREI,Guangzhou 510610,China)

This paper mainly describes the Serial Perripheral Interface(SPI)in C8051F500,especially introduces the structure and the functions of SPI0CKR,SPI0CFG,SPI0CN,SPI0DAT and Shift Register,and studies the communication process of Serial Perripheral Interface(SPI)between master and slave device by simulation.

SPI;SPI0CFG;SPI0CN;SPI0DAT;Shift Register

10.3969/j.issn.1002-2279.2014.03.004

TN4

:A

:1002-2279(2014)03-0011-03

夏琳(1981-),女,沈陽市人,工程師,主研方向:集成電路設(shè)計。

2013-12-26