HDLC協議IP核的設計與實現

閆軍虎,張明社,郗海燕

(中國電子科技集團公司 第39研究所,陜西 西安 710065)

HDLC協議IP核的設計與實現

閆軍虎,張明社,郗海燕

(中國電子科技集團公司 第39研究所,陜西 西安 710065)

文中針對專用ASIC芯片實現HDLC協議針對性強,使用不靈活等特點,提出了使用FPGA IP核來實現HDLC接口的設計方案。HDLC IP核包括3個模塊:對外接口模塊、接收模塊和發送模塊。IP核接收到新數據后存入接收FIFO,對外接口模塊將接收到的數據通過總線將數據送入數據處理單元;當需要發送數據時數據處理單元通過總線將數據存入發送FIFO,啟動發送模塊將數據送出。接收和發送模塊自動完成數據的"插零"及"刪零"操作。仿真結果表明該IP核能夠正確的接收和發送數據。該方法已在某雷達天線的同步引導數據的收發通信鏈路中,成功實現了雙向數據通信。

FPGA;HDLC協議;IP核;FIFO;CRC 校驗

在某雷達測控系統中,采用面向位的、簡化的高級數據鏈路控制(High-Level Data Link Control或簡稱HDLC)協議進行數據交換。 HDLC協議具有數據報文透明傳輸、全雙工通信、傳輸可靠性高等特點,從而廣泛應用于數據通信領域。

通常HDLC協議的實現是采用專用的ASIC 器件來實現的[1]。HDLC的ASIC芯片有ST公司的MK5025、Motorola公司的MC92460、Zarlink公司的MT8952B等[2]。這些集成電路功能針對性強,性能可靠,適合應用于特定用途的大批量產品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執行速度慢,對信號的時延和同步性不易預測。

FPGA(Field Programmable Gate Array, 現場可編程門陣列)采用硬件技術處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。在中小批量通信產品的設計生產中,

用FPGA實現HDLC功能是一種值得采用的方法。正是有鑒于此,Innocor、Xilinx等公司推出了能在FPGA中實現HDLC功能的IP Core(Intellectual Property Core,知識產權核),但這些IP Core需要付費購買許可(License)才能使用,且在應用中受到各種限制。本文從HDLC的基本定義出發,通過對FPGA設計輸入的模塊化描述,介紹一種能夠在FPGA中實現HDLC功能的方法。

1 HDLC的幀結構

首先回顧一下HDLC基本的幀結構形式。HDLC是面向比特的鏈路控制規程,其鏈路監控功能通過一定的比特組合所表示的命令和響應來實現,這些監控比特和信息比特一起以幀的形式傳送。每幀的起始和結束以"7E"(01111110)做標志,兩個"7E"之間為數據段(包括地址數據、控制數據、信息數據)和幀校驗序列。幀校驗采用CRC算法,對除了插入的"零"以外的所有數據進行校驗。為了避免將數據中的"7E"誤為標志,在發送端和接收端要相應地對數據流和幀校驗序列進行"插零"及"刪零"操作。

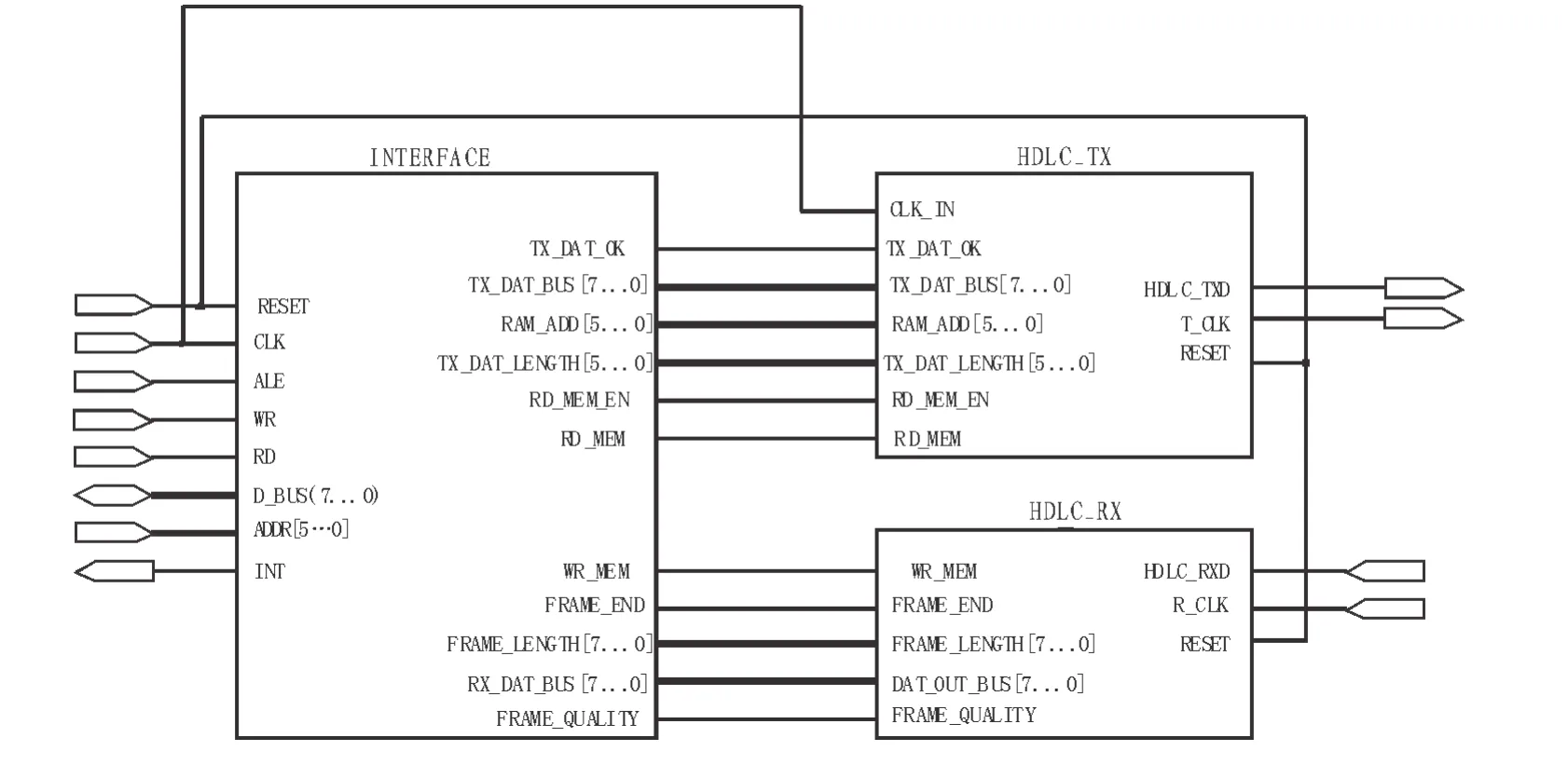

2 原理框圖

基于FPGA的HDLC協議的實現原理框圖如圖1所示。該框圖包括3個部分:對外接口部分、HDLC發送部分、HDLC接收部分。以下對3個部分的實現分別進行論述。

2.1 對外接口模塊

圖1 HDLC協議原理框圖Fig. 1 Block diagram of HDLC protocol

對外接口部分主要實現HDLC對外的數據交換。包括CPU接口、發送FIFO、發送接口、接收FIFO以及接收接口。本設計是以總線的形式實現HDLC與外部CPU的通信。當需要發送數據時,外部CPU通過總線將待發數據寫入FIFO(FIFO的IP核在各開發軟件中都是免費提供的,在程序中只需直接調用即可,故在此不再詳細描述)。之中。發送數據準備就緒標志(TX_DAT_OK);接收數據時,當對外接口模塊接收到數據有效信號時,根據接收模塊發來的寫信號(WR_MEM)將數據寫入接收FIFO中。接收完一幀數時向CPU發送中斷信號(INT),通知CPU讀取數據。

2.2 HDLC發送模塊

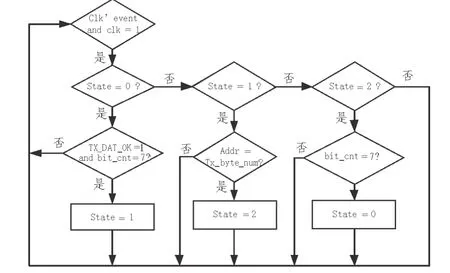

HDLC發送部分主要實現HDLC發送功能。當接收到數據準備就緒標志(TX_DAT_OK)后,向對外接口模塊發送讀使能(RD_MEM_EN)和讀信號(RD_MEM),通過局部總線將待發數據存入發送緩沖區,在T_CLK的控制下將數據從HDLC_TXD管腳發出。數據發送模塊采用狀態機來完成發送各個階段的切換。狀態切換流程圖如圖2所示。

圖2 發送模塊狀態切換流程圖Fig. 2 Switch flow diagram of transmit module

State0狀態是發送的起始狀態也是空閑狀態。當沒有數據要發送時(TX_DAT_OK=0),程序以7E填充發送;當程序檢測到有新數據時(TX_DAT_OK=1),程序檢測7E是否發送結束如果沒結束則繼續發送7E,如果7E發送結束則狀態在下一周期切換為State1。

State1狀態主要完成接收并發送數據功能,在第二個CLK周期先將讀使能和讀信號拉高,在第三個CLK周期再將其拉低,在第五個CLK周期開始讀數。在并行的數據發送PROCESS中根據CLK周期和發送計數器,將接收到的數據通過移位進行發送同時對連續‘1’的個數和發送個數進行計數。當連續‘1’的個數為5時在下一個周期插入發送‘0’,將連續‘1’的計數器清零,發送個數不變。在發送數據的同時進行CRC校驗的計算。幀校驗序列字段使用CRC-16,對兩個標志字段之間的整個幀的內容進行校驗。CRC的生成多項式為X16+X12+X5+1,對在校錯范圍內的錯碼進行校驗。標志位和按透明規則插入的所有‘0’不在校驗的范圍內。程序設計中的CRC校驗算法的原理框圖如圖3所示。

圖3 CRC校驗算法的原理框圖Fig. 3 Block diagram of CRC verfiy

State3 狀態主要完成發送字尾,發送完成后直接轉入state0。

2.3 HDLC接收模塊

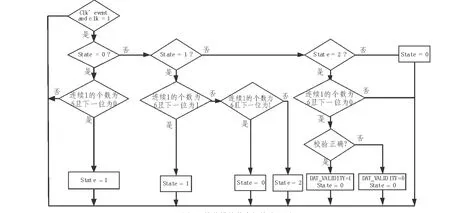

接收模塊接收到一個非“7E”字節時,即判定為地址數據,直到再次接收到“7E”即判定為接收到了一個完整的一幀數。當接收到一個非“7E”數據后就通過內部數據總線(DAT_OUT_BUS)傳送給接口模塊,接口模塊根據FRAME_LENGTH和DAT_VALIDITY來判斷數據幀的長度和有效性。接收數據個階段的狀態切換流程如圖4所示。

在State0狀態程序判斷接收到的數據是否為7E,如果為

圖4 接收模塊狀態切換流程圖Fig. 4 Switch flow diagram of receive module

7 E,則表明已收到了幀頭,狀態切換到State1。在State1狀態程序接收到的下一個數不是7E則表明收到了地址數據,將狀態機切換到State2。在State2狀態判斷是否收到字尾,如果不是字尾則將接收的數據存入接收緩沖區同時啟動寫數據,將接收到的數據通過總線寫入接收fifo。在收數的過程中同時進行刪除‘0’的操作,即當收到連續5個1時將下一個‘0’主動刪除。當收到字尾時對地址數據、控制數據和信息數據的CRC校驗結果與最后兩個字節進行比對形成數據有效標志(DAT_VALIDITY)。

圖5 發送數據仿真波形Fig. 5 Simulation waveform of transmit data

3 仿真與應用

根據上述設計,在Quartus II 9.0上對發送數據和接收數據進行了仿真如圖5、6所示。

圖6 接收數據仿真波形Fig. 6 Simulation waveform of receive data

從仿真波形可以看出發送模塊能夠將FIFO中的數按照設計的波形輸出到HTXD管腳;接收模塊能夠正確的將HRXD管腳的波形數據解出來并存入接收緩沖區中,接收完成后給接口模塊發出END標志。根據上述設計方法,已成功地在可編程邏輯芯片上實現。FPGA芯片選用的是Altera公司的Cyclone系列FPGA:EP1C6T144。

4 結束語

上述詳細介紹了一種基于FPGA的HDLC協議IP核的方案及設計實現方法。根據本文介紹的實現方法設計出的HDLC接口板已應用于某雷達天線的同步引導數據的收發通信鏈路中,成功實現了雙向數據通信。應用結果表明該方法具有簡單實用、性能可靠以及成本低等特點。能夠廣泛應用于HDLC協議應用場合。

[1] 韓露.專用HDLC協議芯片的應用[J].移動通信,2003,27(11):231-232.

HAN Lu.Application of special HDLC protocol chip[J]. Mobile Co mmunication,2003,27(11):231-232.

[2] 付新虎,史浩,等.HDLC協議在通信系統中的應用[J].電子技術,2005,32(8):58-60.

FU Xin-hu,SHI Hao,et al.Application of HDLC protocol in a communication system[J].Electronic Technology,2005,32(8):58-60.

[3] 李宥謀,房鼎益.CRC編碼算法研究與實現[J].西北大學學報:自然科學版,2006,36(6):895-898

LI You-mou,FANG Ding-yi.Research and implementation of a new CRC coding algorithm[J].Journal of Northwest University:Natural Science Edition,2006,36(6):895-898.

[4] 劉巖俊,閆海霞.HDLC通訊協議中CRC的應用[J].電子測量技術,2010,33(3):21-23.

LIU Yan-jun,YAN Hai-xia.Application of CRC during HDLC protocol [J].Electronic Measurement Technology,2010,33(3):21-23.

[5] 肖靜嫻,戴亞文.基于FPGA的異步FIFO緩存設計[J].電子測量技術,2010,32(11):92-94.

XIAO Jin-xian,DAI Ya-wen.Implementation of asynchronous FIFO buffer based on FPGA[J].Electronic Measurement Technology,2010,32(11):92-94.

[6] 范昌平,應三叢.多雷達的一種高可靠智能接入和規范處理[J].四川大學學報:自然科學版,2006.43(4):763-765.

FAN Chang-pin,YIN San-cong.a high reliable intelligent access and standard treatment of multi radar[J].Journal of Sichuan University:Natural Science Edition,2006,43(4):763-765.

Design and realization of the HDLC protocol with FPGA IP core

YAN Jun-hu, ZHANG Ming-she, XI Hai-yan

(The 39th Institute ,Electronic Science and Technology Group Corporation of China, Xi’an 710065, China)

Using the special ASIC to realize the HDLC protocol is not flexible. The paper describes a scheme which using the FPGA IP core to realizing the HDLC protocol. The IP core includes the external interface module;receive module; transmit module. When the IP core receive new data ,it will storage the data in receive fifo. The external interface module will send out the data to the processor form the data bus. When send data, the processor will send the data to the transmit fifo,and startup the transmit module. The receive and transmit module will execute the“insert zero”and“delete zero”automatic. The emulational result indicate that the IP core can receive and transmit date correctly. The scheme has carried out the communication of the synchronous lead date in radar antenna.

FPGA; HDLC protocol; IP core; FIFO; CRC verify

TN820.4

A

1674-6236(2014)11-0181-04

2013–09–16 稿件編號:201309121

閆軍虎(1971—),男,陜西渭南人,高級工程師。研究方向:微電子技術應用。