鎖相環頻率合成器相位噪聲改善方法研究*

廖小健

(1.華中科技大學 武漢 430074)(2.武漢軍械士官學校 武漢 430075)

1 引言

頻率合成器以一個高穩定度、高準確度的標準頻率作為參考,通過對參考頻率進行倍頻、混頻、分頻等處理產生大量與參考頻率具有相同穩定度和準確度的不同頻率的系統。頻率合成器在電子設備中發揮著重要作用,直接影響著電子設備的性能,所以被稱為電子設備的心臟。

目前用于實現頻率合成器的技術主要有三種:直接模擬頻率合成技術(DAS)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)。鎖相環頻率合成技術相比于DDS和DAS具有更高的雜散抑制,頻譜更加純凈。相對于DDS,鎖相環頻率合成技術的頻段更寬;相對于DAS,鎖相環頻率合成技術又具有結構簡單的特點[1]。鑒于鎖相環頻率合成技術的以上優點,鎖相環式頻率合成技術已成為目前通信、儀表、雷達等電子設備中應用最廣泛的一種頻率合成技術。

但相對于另兩種頻率合成技術,鎖相環頻率合成技術的相位噪聲較大。相位噪聲會影響電子設備的各項性能。在通信系統中相位噪聲會使話路信噪比下降,誤碼率增加;在雷達系統中影響雷達對目標的分辨能力;而混入接收機本振中的相位噪聲,當接收機遇到強干擾信號時,會產生“倒混頻”使接收機有效噪聲系數增加。所以隨著電子技術的發展,改善相位噪聲是鎖相環頻率合成器研制的關鍵。

2 鎖相環頻率合成器的結構及相位噪聲分析

鎖相環頻率合成的基本方法是:采用鎖相環路對高穩定的參考振蕩器鎖定,利用環內所連接的可編程程序分頻器,通過改變程序分頻器的分頻比N,獲得N倍參考頻率的輸出頻率。

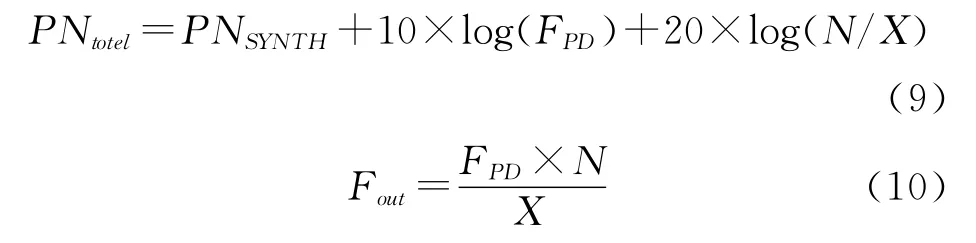

鎖相環頻率合成器結構如圖1所示。

圖1 鎖相環頻率合成器結構

鎖相環頻率合成器由參考晶振(OCXO)、鑒頻鑒相器(PFD)、環路低通(LP)、壓控振蕩器(VCO)、R分頻器和N分頻器組成。由上圖可知,VCO 經過N分頻和參考晶振經過R分頻后的信號都輸入PFD 進行相位和頻率比較,如果這兩個頻率不相等,PFD 的輸出會改變,而VCO 的輸出頻率是由PFD 的輸出控制的,所以VCO 的輸出頻率也會改變,直到兩個頻率相等,環路穩定工作。輸出信號的頻率為

式中Fref是參考晶振輸出的參考頻率,Fout是頻率合成器的輸出信號。如果要改變輸出頻率,只用改變分頻比N就可以了。

按照上述方法構成的單環鎖相頻率合成器是鎖相環頻率合成的基本單元,這種基本單元在電子設備中有廣泛的應用。但是,對于信號質量要求高的電子設備,這種頻率合成器輸出信號的相位噪聲很難滿足要求。

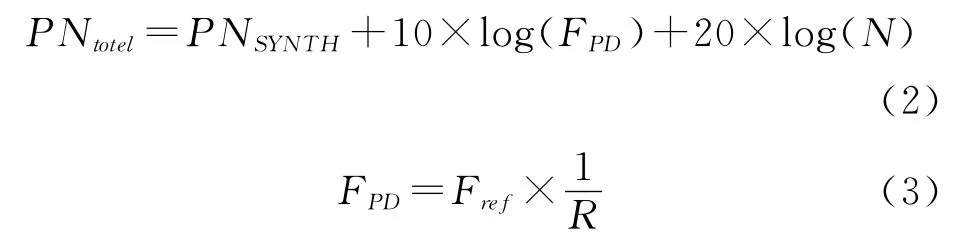

鎖相頻率合成器對參考晶振、R和N分頻器引入的相位噪聲表現為低通,而對VCO 引入的相位噪聲表現為高通特性。現在主流的鎖相環芯片都集成了鑒頻鑒相器、R、N分頻器,而參考晶振的相位噪聲性能一般可以做得很好,所以通帶內鎖相環芯片(鑒頻鑒相器、R、N分頻器)產生的相位噪聲占鎖相頻率合成器相位噪聲的主導[2]。鎖相環芯片產生相位噪聲為

PNtotel表示鎖相環芯片(鑒頻鑒相器、R、N分頻器)對輸出信號貢獻的相位噪聲,PNSYNTH是鑒頻鑒相器(PFD)1Hz歸一化相位噪聲基底,FPD是鑒相頻率,其值由式(3)給出,N為鎖相環的分頻比。

由式(2)可知,鎖相環芯片產生的相位噪聲隨著N值的增加上升速度是鑒相頻率FPD上升的兩倍。由式(1)和式(3)得到,輸出頻率一定時,分頻比N和鑒相頻率FPD的乘積是一定的,所以選用更大的鑒相頻率可以降低鑒相器產生的相位噪聲。鑒相頻率提高一倍,相位噪聲降低3dB。但單環鎖相頻率合成器的鑒相頻率必須等于輸出頻率的頻率步進,所以不能通過增大鑒相頻率來降低相位噪聲。

由式(2)可知,在鑒相頻率一定的情況下,輸出信號的相位噪聲還取決于分頻比N。頻率合成器的相位噪聲增加量為20logN,頻率合成器要輸出高頻段信號,則分頻比N會很大,必然造成噪聲增加量20logN也很大,這時相位噪聲往往很差,達不到工程應用的要求。通過上面的分析,可看出輸出頻率的相位噪聲受分頻比N的影響較大。為了解決這一問題需要對頻率合成器的基本單元進行改造,使鎖相環的分頻比N減小。目前比較常用且能減小分頻比N從而有效降低相位噪聲的鎖相頻率合成器結構有以下五種:雙鎖相環環內混頻結構、鎖相環+分頻器結構、DDS 激勵鎖相環結構、DDS內插鎖相環結構和小數分頻結構。下面逐一介紹它們的結構及適用的場合。

3 低相位噪聲鎖相環頻率合成器結構

由于頻率合成器相位噪聲對電子設備的性能有著重要的影響,所以降低相位噪聲是頻率合成器設計和制作的一個重點。下面對當前流行的低相位噪聲鎖相環頻率合成器結構進行分析研究,最后總結各結構對相位噪聲的改善值及結構的優缺點。

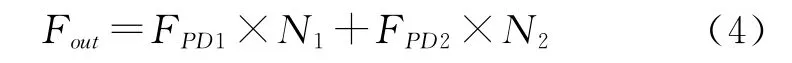

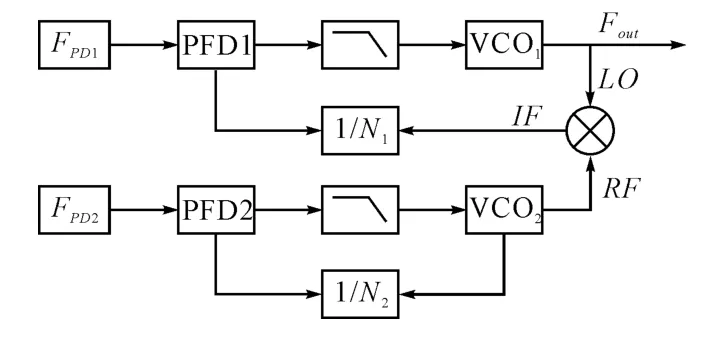

3.1 雙鎖相環環內混頻結構

如圖2所示,雙鎖相環環內混頻結構由兩個鎖相環和一個混頻器組成,主環和輔環輸出頻率關系為

其中,FPD1、FPD2分別是主環和輔環的鑒相頻率,N1、N2則分別為主環和輔環的分頻比[3]。

主鎖相環輸出的信號作為LO 信號和輔鎖相環信號進行下變頻,混頻輸出較低頻率的IF 信號,降低主鎖相環分頻比N1。主鎖相環的鑒相頻率等于頻率步進,這樣只用通過改變N1就可以實現跳頻。輔環輸出的頻率為定頻信號,所以它的鑒相頻率可以隨意選取。

圖2 雙鎖相環結構

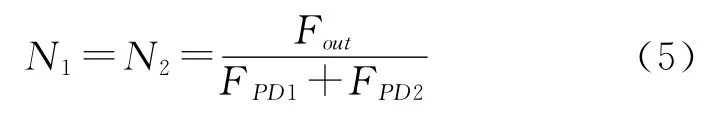

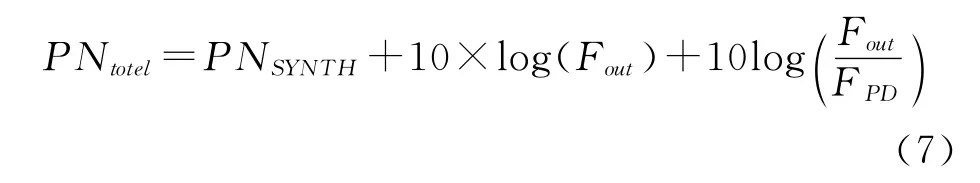

對雙環的相位噪聲進行計算得出,當兩環的分頻比為

雙環的相位噪聲取得最小值,為

單環頻率合成器的相位噪聲公式也可以改寫為

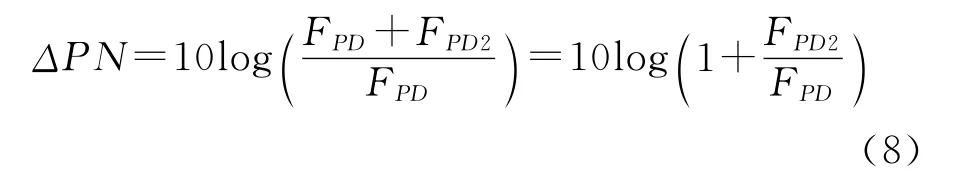

而單鎖相環的鑒相頻率FPD=FPD1,式(7)與式(6)相減得到雙環相對于單鎖相環的相位噪聲改善為

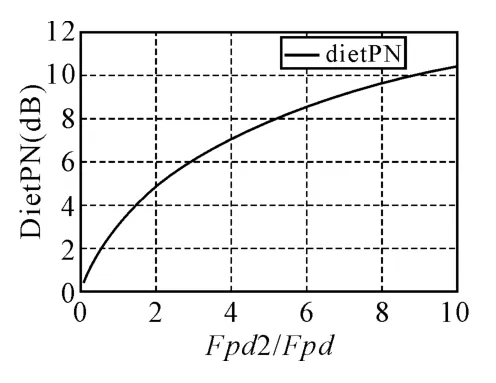

圖3 ΔPN—FPD2/FPD

圖3給出了雙環結構相位噪聲改善效果和鑒相頻率比值之間的關系。如圖3所示,比值越大,改善效果越好。但這種結構也有其缺點,首先,盡管通過輔環降低了主環的分頻比,當頻率步進很小時,主環的相位噪聲仍然會很大;相對于單鎖相環,這種結構需要的器件多了一倍;輔環的信號通過混頻器可能會給輸出信號帶入一個大的雜散。

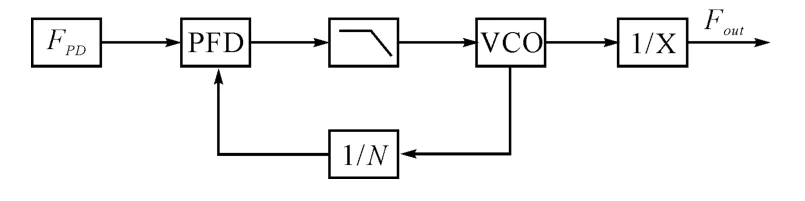

3.2 鎖相環+分頻器結構

鎖相環+分頻器結構如圖4所示。這種結構就是在鎖相環后面加一個分頻器[4]。輸出信號的相位噪聲為

由式(10)得到,使FPD和X同比例地增加時可保持輸出頻率不變;由式(9)得到,輸出相位噪聲卻降低了。X每增大一倍,FPD也增大一倍,PNtotel則降低3dB。

圖4 鎖相環+分頻器結構

但這種結構也有其不足之處,通過原理可知,這種方案間接提高了鎖相環的輸出頻率,增加了鎖相環芯片的選擇和設計的難度;同時跟結構一類似,當頻率步進很小要求的輸出頻率又很高時相位噪聲仍然會很大。

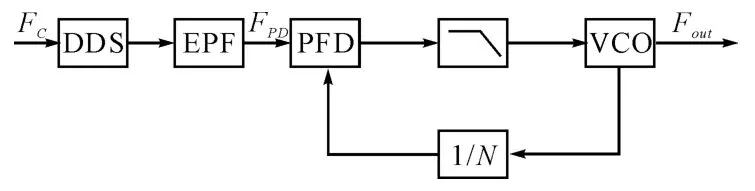

3.3 DDS激勵鎖相環結構

DDS激勵鎖相環結構如圖5所示。

圖5 DDS激勵鎖相環結構

這種方案利用DDS 作為鎖相環的參考頻率。工作時,保持鎖相環的分頻比N不變,通過改變DDS的輸出頻率來實現跳頻[5]。這樣在較低的分頻比N的情況下可以得到較低的頻率步進;而鎖相環不僅可以增大DDS的輸出頻率范圍,也可以對DDS產生的雜散進行濾除。實現了低相噪、高雜散抑制和寬頻率范圍的頻率合成。但這種結構也有一個缺點就是如果DDS產生的雜散落在環路低通帶內,就無法通過鎖相環濾除。

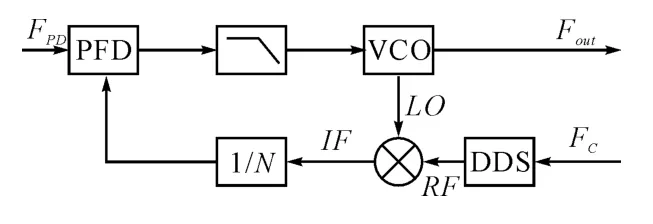

3.4 DDS內插鎖相環結構

DDS內插鎖相環結構如圖6所示。跟結構三相似,DDS改進了鎖相環的相位噪聲和頻率步進,而鎖相環則濾除了DDS 的雜散[6];而且由于鎖相環沒有對DDS的信號進行倍頻,DDS的相位噪聲和雜散不會被鎖相環放大,保證了輸出信號的頻譜純度。

圖6 DDS內插鎖相環結構

相對于結構三,這種結構中混頻器會給輸出信號帶入一個大的雜散。

3.5 小數分頻鎖相環結構[7]

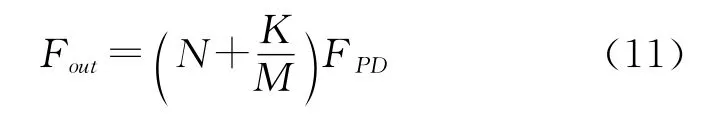

小數分頻的結構如圖7所示。它的結構基本和整數分頻鎖相環相同,但在分頻器部分增加了相位累加和脈沖扣除的功能[8~9],這實現了鎖相環的小數分頻。式(11)給出了輸出頻率的計算公式

其中N代表整數部分,M是模數,K是小于等于M的整數,最小頻率步進為Fr/M。在小數分頻鑒相器中M可以取到很大的值,比如AD 公司的ADF4159為225。

對于整數分頻鎖相環,鑒頻鑒相頻率必須等于頻率步進,當頻率步進很小的時候,分頻比就會很大,相位噪聲會惡化。小數分頻鎖相環解決了這個問題,在比較大的參考頻率下,仍可以實現小的頻率步進,降低了相位噪聲。但小數分頻鎖相環引入的脈沖扣除會產生小數雜散。

圖7 小數分頻鎖相環結構

前面對目前比較常用且能有效降低相位噪聲的鎖相頻率合成器結構做了具體的分析,現在將他們的相噪改善效果、優點、缺點做如下總結。

表1 鎖相頻率合成器相噪改善效果、優缺點表

4 結語

以鎖相環為基礎構成的頻率合成技術是目前通信、儀表、雷達等電子設備中廣泛應用的頻率合成技術。頻率合成器相位噪聲的好壞對設備的性能有很大的影響。本文介紹了目前比較常用且能有效降低相位噪聲的鎖相頻率合成器結構,這些結構都是通過降低分頻比N實現相位噪聲的降低。通過分析可以看出采用這些結構的頻率合成器對相位噪聲都有改善,同時由于結構不同,他們又有各自的優缺點,所以在設計頻率合成器時,要根據不同的系統要求采用不同的結構。

[1]盧炳.Ku波段低相噪頻率源的設計與仿真[J].艦船電子工程,2013,33(5):83-85.

[2]陳剛.鎖相環路的相位噪聲分析[J].科技信息,2009(3):112-113.

[3]李晉,劉光祜.C 波段寬帶低噪聲頻率源的研制[J].現代電子技術,2008(274):53-55.

[4]Mike Curtin.Design a Direct 6-GHz Local Oscillator with a Wideband Integer-N PLL Synthesizer.USA:Analog Device,2001:33-39.

[5]Jaehung Choi,Minsu Kim,Seungha Shin,et al.Low Phase Niose S-band PLL Frequency Synthesizer Using DDS and Offset Mixing Techniques[C]//APMC,Singapore,2009:1409-1412.

[6]Li Yongke.The Design of Wide BW frequency synthesizer based on the DDS&PLL hybrid method[C]//ICEMI,Beijing,2009:689-692.

[7]趙偉波,管鳳仁,祁佑光.S頻段小數分頻鎖相環頻率合成器實現與應用[J].飛行器測控學報,2011,30(4):31-34.

[8]N.Fatahi,H.Nabovati.Design of Low Noise Fractional-N Frequency synthesizer Using Sigma-Delta Modulation Technique[C]//International Conference on Microelectronics Proceedings,Serbia,2010:369-372.

[9]Jun Zhao,Yong-Bin Kim.A Novel All-Digital Fractional-N Frequency Synthesizer Architecture with Fast Acquisition and Low Spur[C]//International Symposium on Quality Electronic Design,CA,2010:213-216.