基于DDS 的寬帶信號發生器的設計

張 萍

(江陰職業技術學院 電子信息工程系,江蘇 江陰214405)

在雷達系統、通信系統以及自動控制系統中,一個高精度、高穩定度、輸出頻率范圍寬且可調的信號源往往是設備和系統實現高性能的關鍵。而常用的信號發生器往往只能輸出低頻信號,或者只能輸出高頻信號,因此設計一種既能提供低頻信號,又能提供高頻信號的信號發生器就顯得非常必要。

信號發生器一般有這樣幾種實現方法:(1)用專門的函數信號發生器IC 產生,如L8038 等,其功能較少,精度不高,頻率上限只有300 kHz,無法產生更高頻率的信號;(2)用單片集成芯片的函數發生器實現,如MAX038,能產生多種波形,達到較高的頻率,但是MAX038 輸出頻率是用模擬信號控制的,需要將微處理器輸出的數字信號經過D/A 轉換,并經過信號調理之后進行控制,不但增加了電路的復雜程度,輸出頻率精度也不高。

為了解決以上問題,系統采用內部集成了高速數字電路和高速D/A 轉換電路,直接數字合成DDS芯片實現信號發生器,其輸出波形具有頻率范圍寬、頻率轉換時間短、頻率分辨率高、輸出相位連續、穩定程度高、可編程、全數字化等特點[1-2],有效克服了上述方案的不足。

1 系統總體方案

系統以TMS320LF2407 DSP 為控制核心,AD9854 為DDS 模塊構成寬頻帶信號發生器,能夠產生正弦波、方波和三角波3 種波形,如圖1 所示。TMS320LF2407 和AD9854 的工作電壓都是3.3 V,兩者電平完全匹配,兩者之間可以直接進行數據傳輸,不需要進行電平轉換。AD9854 功耗較大,圖1 中的電源電路采用低壓差穩壓器LM1085IS-3.3 將系統輸入的5 V 電源轉換為3.3 V 電壓,其輸出電流為3 A,具有足夠的驅動能力,完全滿足AD9854 功耗要求。

圖1 系統總體框圖Fig.1 Overall system diagram

頻率輸入鍵盤采用4 ×4 矩陣鍵盤,可以通過此鍵盤輸入任何大小頻率。幅值選擇電路采用電阻分壓電路實現,電路輸出的不同電壓對應不同的信號幅值,DSP 的A/D 轉換模塊采樣輸入電壓,控制系統輸出不同幅值的信號。

TMS320LF2407 根據從鍵盤輸入的頻率大小和從幅值選擇電路輸入的幅值大小,對AD9854 頻率寄存器、幅值寄存器和其他寄存器進行編程,控制AD9854 輸出指定頻率和幅度的正弦信號,此正弦信號經過濾波電路濾除雜波。由于AD9854 直接輸出的正弦波幅值最大只能達到1 V,而實際使用中,往往需要更大幅值的正弦波,因此濾波輸出的正弦波還需要經過放大電路進行幅值放大。而AD9854 輸出的正弦波頻率最高可達到150 MHz,因此這里使用的放大電路帶寬必須足夠寬才能進行正確放大。

AD9854 內置高速比較器,其產生的正弦波與參考電壓通過高速比較器進行比較輸出方波信號,此方波信號經過時鐘緩沖電路緩沖,并經過寬帶放大電路進行放大,即可得到所需幅值的方波信號[3-4]。此方波信號可通過積分電路進一步得到三角波。

2 主要功能模塊的設計

2.1 DDS 波形產生電路

數字頻率合成(DDS)芯片AD9854 是用于高端DDS 技術的一款芯片,該芯片帶有兩個高速、高性能的正交D/A 轉換器,可以同時輸出I/Q 兩路正交信號。該芯片內部還帶有一個超高速比較器,將芯片輸出的正弦信號與參考電壓進行比較,可以輸出一路方波信號。當參考時鐘源有很高精度時,AD9854 能夠產生高穩定度的頻率、相位、幅度均可編程的正弦信號和方波信號。在最高300 MHz 的參考時鐘信號下理論上允許輸出信號的頻率最大為150 MHz,輸出信號頻率可達100 MHz,內部相位截斷保證了良好的無雜散動態范圍(SFDR),內部集成兩路14 位相位寄存器、一個鍵控整形功能、兩路48 位頻率控制字寄存器、兩路12 位高精度幅度控制寄存器。AD9854 具有多種工作模式,能夠實現單音調、頻移鍵控(FSK)、二元相移鍵控(BPSK)、相移鍵控(PSK)和脈沖調頻(CHIRP)等多種輸出方式。

可以通過配置AD9854 的48Bit 頻率字F、14 Bit相位字Phase 和12 Bit 幅值字得到所需頻率和幅值的波形。AD9854 頻率控制字[5-6](對應并行地址為04H ~09H)、相位控制字(并行地址為00H ~01H)和幅值控制字(I 路并行地址為21H ~22H,Q 路并行地址為23H ~24H)可分別根據式(1),(2),(3)得到:

系統中AD9854 采用30 MHz 晶振,通過并行地址為IEH 的控制字配置倍頻系數為10 倍,則系統時鐘頻率為300 MHz。如果要得到輸出頻率為1 MHz、相位為450,幅值為0.5 V 的波形,則頻率、相位和幅值控制字應分別為

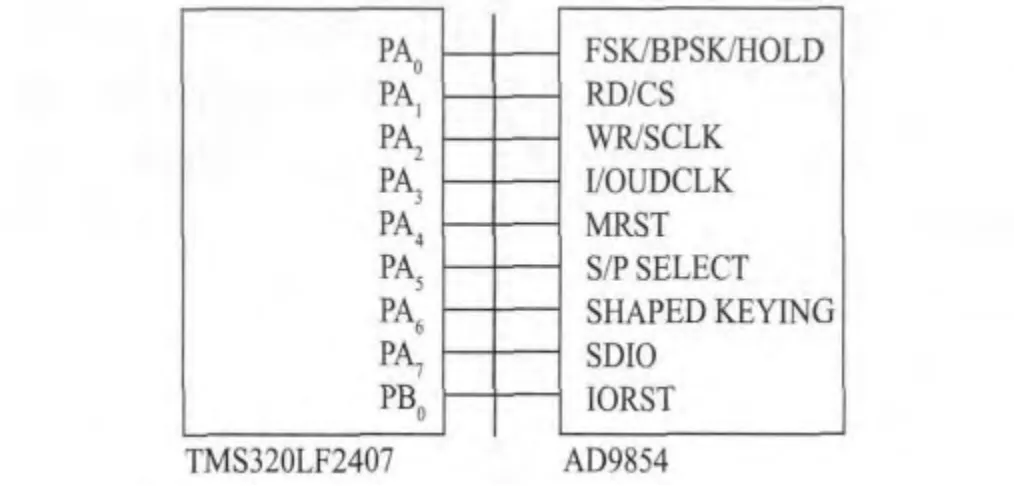

AD9854 用常用的串行編程方式與DSP 進行接口,圖2 為TMS320LF2407 與AD9854 接口電路示意圖。

圖2 TMS320LF2407 與AD9854 串行接口電路示意Fig.2 TMS320LF2407 and AD9854 serial interface circuit schematic

由于采用的是串行編程方式, 工作時TMS320LF2407 的引腳PA5應該提供給S/P SELECT低電平。IORST 是IO 復位,MRST 是主復位,上電復位以后,TMS320LF2407 首先通過引腳MRST 給AD9854 一個主復位脈沖,使AD9854 處于一個初始工作狀態。FSK/BPSK/HOLD 和SHAPED KEYING是實現不同工作模式時的控制信號,CS,SCLK,SDIO 分別是與DSP 之間進行數據傳輸的片選、時鐘和數據端,在工作模式配置字、頻率控制字、相位控制字和幅值控制字寫入后,最后通過引腳I/OUDCLK 輸入給AD9854 一個更新脈沖,控制字才能真正進入到AD9854 內核。

2.2 濾波電路

根據DDS 頻譜可知,由于相位截斷和D/A 轉換的存在,使得輸出端存在高次諧波分量干擾,尤其是在高頻率信號輸出時干擾越大。為了得到良好的輸出信號必須要對輸出信號進行濾波處理。本系統采用7 階切比雪夫濾波器[7],如圖3 所示,采用電感與電容(0 ~100 pF)連接,通過掃頻儀調整電感和電容的值使濾波器的帶寬滿足要求。

圖3 濾波電路Fig.3 Filter circuit

2.3 寬帶放大電路

系統采用的是TI 公司推出的一款低功耗、電流反饋型放大器OPA695,該放大器能夠提供1.4 GHz的帶寬增益積,非常適合對高頻信號進行放大。通常適用于視頻信號處理、線纜調制解調器、無線通信以及測試儀器等領域的各種應用[8]。

由于系統輸出信號頻率很高,導致干擾的因素很多,因此高速放大器在布局布線時要非常注意。如圖4 所示,在電源和地線之間要加上去耦電容,在OPA695 電源的正負極分別串聯一個磁珠,以進一步減小電源所帶來的干擾。在PCB 布局時,電容、電阻等元器件應盡量靠近OPA695 芯片的引腳,以使走線長度最短,從而進一步減小因走線所帶來的干擾。電阻也最好采用貼片、噪聲小的電阻。

圖4 放大電路Fig.4 Amplifying circuit

系統采用±5 V 雙電源供電,并通過去耦電容和磁珠去除電源中的干擾。輸入信號經過一個0 Ω電阻進行濾波,輸出信號串聯一個50 Ω 電阻進行阻抗匹配,輸入輸出信號都是采用屏蔽線連接,以防引入干擾。

高速放大器的反饋電阻為560 Ω,反向輸入端和地之間串聯一個27 Ω 固定電阻和一個1 kΩ 的可調電阻。通過調節可調電阻,可以改變電路的放大倍數。

3 實驗測試與結果分析

在實驗室采用數字示波器對系統輸出波形進行測試,結果表明,其最低輸出頻率可達到毫赫茲,最高輸出頻率可達到百兆赫茲。圖5 和6 所示是示波器上顯示的系統輸出500 mHz 和90 MHz 的正弦波。從圖中可以看出,其輸出波形比較理想。當輸出波形頻率大于500 mHz、小于90 MHz 時,波形更為理想。由此可見,系統輸出波形頻率范圍不但包括音頻(200 ~20 000 Hz)、視頻(1 Hz ~10 MHz)和高頻(100 kHz ~30 MHz),而且還達到了超低頻(mHz)和甚高頻(90 MHz),表明系統性能優良,能提供很寬頻率范圍的波形。

圖7 和8 所示是1 kHz 正弦波5 倍放大前后在示波器上顯示的波形。放大之前峰-峰值為1.04 V,放大之后峰-峰值為5.03 V,放大后的幅值與放大前5倍之間的微小差異可以通過調節圖4 中的可調電阻RF 消除,此寬帶放大電路放大后波形仍然非常理想,說明系統寬帶放大電路放大效果良好。

圖5 500 mHz 的信號Fig.5 500 mHz signal

圖6 90 MHz 的信號Fig.6 90 MHz signal

圖7 幅值放大之前的1 kHz 正弦波Fig.7 1 kHz sine wave before amplitude amplification

圖8 幅值放大5 倍后的1 kHz 正弦波Fig.8 1 kHz sine wave after amplitude amplication 5 times

通過調節圖4 中的可變電阻RF 可以得到不同的放大倍數,從而可使系統輸出波形幅值變化范圍進一步擴大。

4 結 語

針對常用的信號發生器很難既能輸出低頻,又能輸出高頻信號,設計了一款基于AD9854 的信號發生器,系統由頻率輸入鍵盤、幅值選擇電路、DDS波形產生電路、低通濾波電路、時鐘緩存電路、寬帶放大電路和積分電路等組成。通過實驗驗證了當系統輸出波形頻率在500 mHz ~90 MHz 時波形理想,輸出波形的頻率、幅度、相位等能實現精確控制,其輸出波形頻率范圍不但包括低頻和高頻,而且還可以達到超低頻和甚高頻,性能優良,在雷達系統、通信系統以及自動控制系統中具有較好的實用價值。

[1]韓旭,于小億.基于PSOC 的DDS 信號發生器設計[J].電測與儀表,2012(3):85-88.

HAN Xu,YU Xiaoyi.Design of DDS signal generator based on PSOC[J].Electrical Measurement and Instrumentation,2012(3):85-88.(in Chinese)

[2]李雪梅,張宏財,王學偉.基于DDS 技術的信號源設計[J].電測與儀表,2010(1):55-56.

LI Xuemei,ZHANG Hongcai,WANG Xuewei.The design of a signal source based on DDS technology[J]. Electrical Measurement and Instrumentation,2010(1):55-56.(in Chinese)

[3]袁輝.基于FPGA 的數字信號發生器的設計與實現[J].電子技術應用,2011,37(9):67-69.

YUAN Hui. Design and implementation of digital signal generator based on FPGA[J]. Application of Electronic Technology,2011,37(9):67-69.(in Chinese)

[4]劉哲,韓焱,姚金杰.基于DDS 的多模信號發生器設計[J].計算機測量與控制,2010,18(3):731-733.

LIU Zhe,HAN Yan,YAO Jinjie. Design of signal generator with multi-mode based on DDS[J]. Computer Measurement and Control,2010,18(3):731-733.(in Chinese)

[5]劉春梅,鄒傳云,曹文,等.基于DDS 芯片的相位相關雙通道信號源設計[J].電子技術應用,2013,39(1):43-46.

LIU Chunmei,ZOU Chuanyun,CAO Wen,et al. Design of double channel signal source with related phase based on DDS chip[J].Application of Electronic Technology,2013,39(1):43-46.(in Chinese)

[6]張海濤,苗圃,李珍.DDS 雜散抑制技術研究與仿真[J].計算機仿真,2011,28(2):397-400.

ZHANG Haitao,MIAO Pu,LI Zhen.Research and simulation on DDS spurious suppression[J]. Computer Simulation,2011,28(2):397-400.(in Chinese)

[7]苗圃,張海濤,龐永星.基于DDS 的低通濾波器設計與仿真[J].電子技術應用,2010(5):52-56.

MIAO Pu,ZHANG Haitao,PANG Yongxing.Design and simulation of low pass-filter based on DDS[J].Application of Electronic Technology,2010(5):52-56.(in Chinese)

[8]張凱琳,蘇淑靖,劉利生,等.基于FPGA 的DDS 多路信號源設計[J].電測與儀表,2011(3):63-65.

ZHANG Kailin,SU Shujing,LIU Lisheng,et al. Design of multi-channel DDS signal generator based on FPGA[J]. Electrical Measurement and Instrumentation,2011(3):63-65.(in Chinese)