一種面向智能傳感器的低功耗高精度sigma-delta調制器設計

周文彬 , 賈紹磊 , 梅年松 , 張釗鋒

(1.中國科學院 上海高等研究院 微納器件中心,上海 201210;2.中國科學院研究生院 北京 100190)

隨著物聯網不斷發展,人們要求智能傳感器能準確感知環境,兼顧使用壽命長,自校準,自檢測等功能,而模數轉換器(ADC)連接模擬域與數字域,其性能嚴重制約著智能傳感器性能發揮。為了有效檢測傳感器輸出微弱信號,對處理微弱信號接口電路(含ADC模塊)功耗要求嚴格[1]。在微弱信號輸入高精度的開關電容(SC)系統中,確定采樣電容及過采樣率(OSR)后,需要熱噪聲低于計算值,但增加了OTA功耗。盡管隨著CMOS集成電路工藝的不斷進步,大幅度減少了傳感器系統的數字功耗,但是含有ADC的模擬前端電路功耗并沒有顯著改善[2]。

在基于傳感器的高精度信號檢測系統中,要求信號帶寬在20 Hz~50 kHz的范圍內具有良好的性能。數字化傳感器SOC常使用高分辨率、低帶寬的 ΣΔADC[3-4]。 在設計 ΣΔADC核心調制器時如何兼顧高精度和低功耗是當今研究熱點,如Nam、Sang-MinSu等[5]采用多比特量化技術達到高精確度,但是數字功耗過大,其中DWA和誤差校準單元精確度要求極高。同時,為了積分器留有足夠輸出擺幅裕量,Z Cao,T Song等[6]采用分離路徑偽差分放大器節約功耗,但是諧波失真明顯,導致精度降低。

針對物聯網傳感器節點應用,本文選擇四階前饋單位量化ΣΔ調制器避免以上研究缺陷,利用MatlabSD-TOOLBOX及Simulink確定系統參數和電路子模塊的系統指標。電路采用SMIC 0.18μCMOS工藝及1.2 V電壓實現,設計目標為輸入信號帶寬在10 kHz范圍內時,調制器精度達到14 bit,而功耗在同類設計中優秀。

1 系統設計

1.1 DT-ΣΔ調制器結構

離散時間(DT)ΣΔ調制器常被應用于低頻智能傳感器領域[7]。本文采用DT-ΣΔ調制器應用在物聯網高精度信號檢測接口電路中,設計目標是信號帶寬在10 kHz范圍內,精度達到14 bit。盡管級聯結構比高階ΣΔ調制器穩定性好,但級聯結構的調制器對元器件的匹配性要求很高,否則就會有噪聲泄露到信號中,同時需要高增益OTA。而多比特量化結構需要動態匹配單元(DEM),增加了功耗和系統設計的復雜性。

本文采用四階前饋單位量化結構,主要具有以下優勢:1)相對于傳統的局部反饋結構調制器,前饋結構不僅可以實現相同的噪聲傳遞函數(NTF),而且信號傳遞函數(STF)與環路參數不相關;2)輸入信號直接加到量化器的輸入端,一方面使信號傳遞函數在信號帶寬內為單位增益;另一方面,積分器只處理量化噪聲,降低了對積分器輸出擺幅的要求,減小調制器的失調,同時為放大器的設計提供更大裕度,提高了整個調制器的動態范圍,非常適合低電源電壓使用。

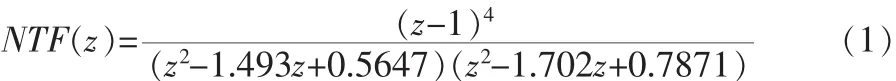

系統參數通過Matlab SD-ToolBox中的synthesizeNTF函數,得到初始NTF:

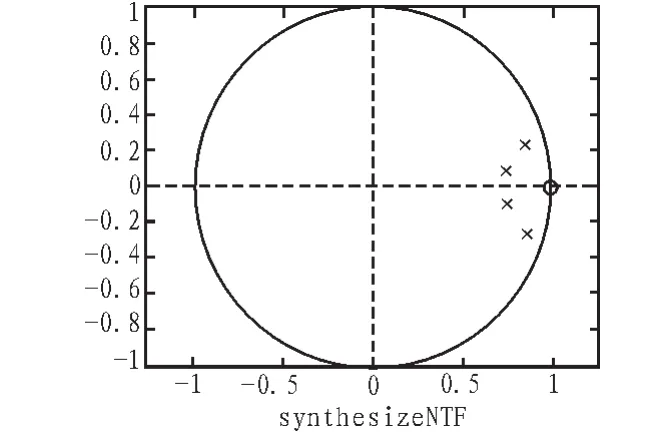

圖1為ΣΔ調制器的零極點分布圖,圖2為SNR與輸入信號幅度關系圖。

圖1 ΣΔ調制器零極點分布圖Fig.1 Zero and Pole ofΣΔmodulator

圖2 SNR隨輸入信號幅值變化圖Fig.2 SNR vs.input amplitude

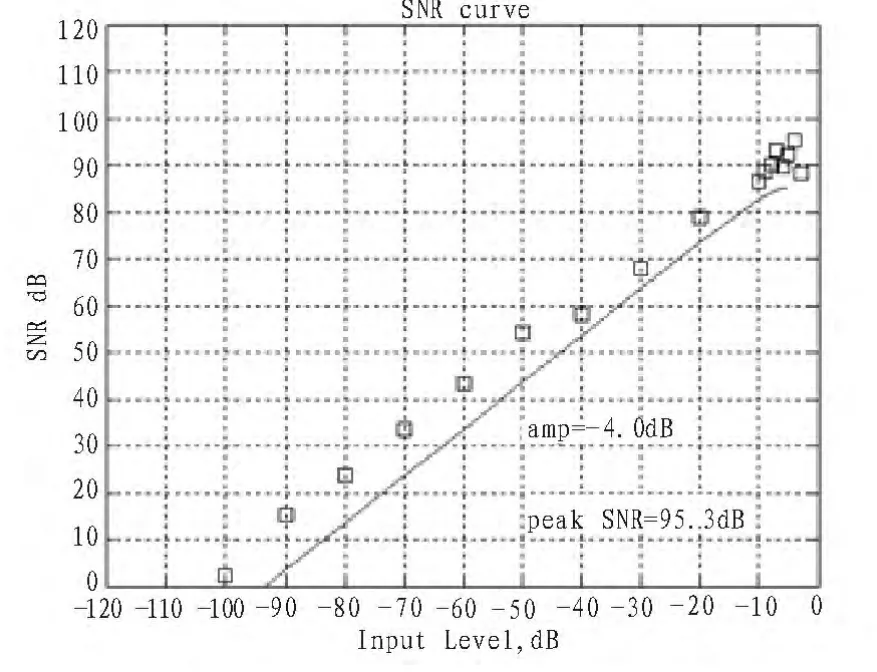

1.2 行為級驗證

為了能得到一個穩定的調制器系統,需要對調制器系統模型進行行為級仿真驗證,本文采用SIMULINK建模,包括積分器建模、采樣噪聲建模、量化器建模等。運用數值迭代算法對從synthesizeNTF函數中得到的系統參數進行優化,得到最優參數值,結合實際電路綜合考慮,確定[a1 a2 a3 a4]=[0.2 0.4 0.1 0.1],[c1 c2 c3 c4]=[1 1 1 2]。 加入-4dBFs、3.4 kHz 的正弦輸入信號,OSR等于64可以實現14.74 bit ENOB,系統仿真結果如圖3所示。通過以上行為級仿真可以得到OTA增益大于43 dB,擺率大于4 V/μs即可滿足系統要求,各級積分器輸出幅度分別為 0.3、0.15、0.1、0.15。

圖3 ΣΔ調制器輸出頻譜Fig.3 PSD of input signal

2 電路設計

2.1 ΣΔ調制器結構

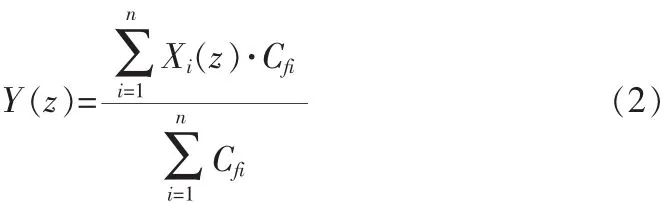

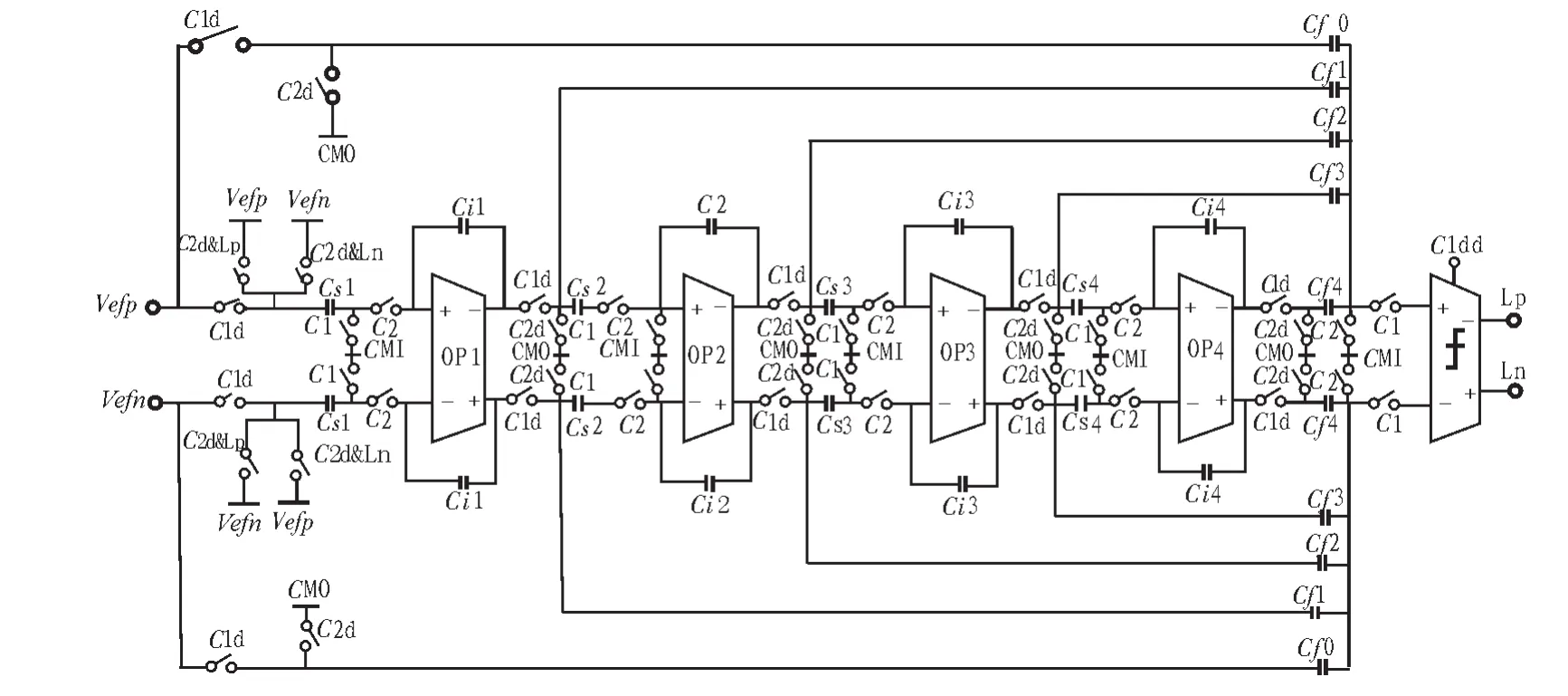

本文設計的四階前饋單位量化ΣΔ調制器采用開關電容技術實現,整體電路如圖4所示。在1.2 V電源電壓下,調制器的輸入共模電壓V cmi設為0.5 V,輸出共模電壓V cmo取在0.6 V,因此無需軌到軌OTA設計。量化器輸入信號由電容求和電路提供,無直流功耗,而量化器輸出直接反饋到第一級積分器,因此只需要在參考電壓和采樣電容間增加開關,即可完成1bit DAC功能。積分器開關由兩相非交疊時鐘控制,同時為了降低溝道電荷注入效應,對C1、C2進行延時C1d、C2d。 C1、C1d 為高電平時,完成采樣;C2、C2d 為高電平時,完成積分。由于比較器是在電路輸出穩定后工作,需要對C1d進一步延時為C1dd。本文前饋結構ΣΔ調制器采用開關電容實現加法器功能。該加法器的傳遞函數表示為:

式中Xi表示第i級積分器輸出,Cfi表示第i級求和電容。

2.2 采樣電容選擇

ΣΔ調制器中采樣電容越大,噪聲抑制效果越好,但是增加了面積,因此在設計時需要折中考慮。由于第一級積分器沒有噪聲整形,需要大電容抑制噪聲。與其相關的信噪比為:

圖4 ΣΔ調制器電路架構Fig.4 Structure of the proposedΣΔmodulator

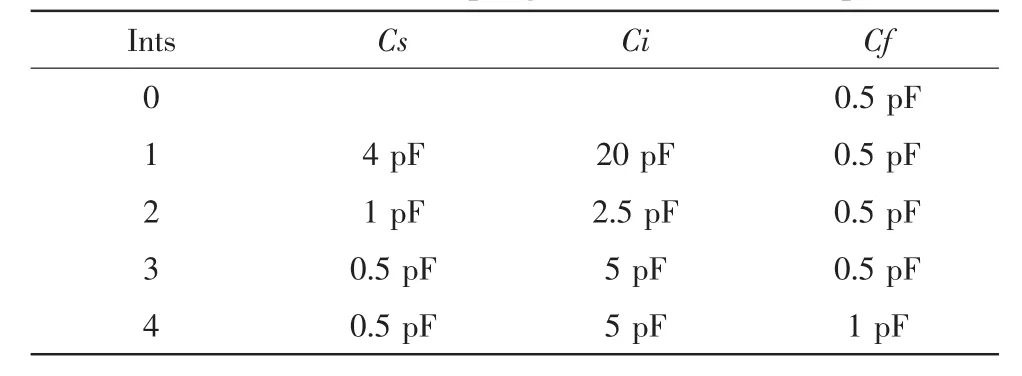

其中V p-p是輸入信號的峰峰值,V p為輸入信號峰值,M為第一級積分器的噪聲,C s1是第一級積分的采樣電容,k為玻爾茲曼常數,T為絕對溫度,本文ΣΔ調制器反饋電壓V refp、V refn分別為 0.75 V、0.25 V。14bitΣΔ 調制器的 SNR 需要達到86 dB,C s1大約為3.2 pF,考慮一定的設計裕度,取4 pF。經過第一級積分器噪聲整形,后面各階只需要考慮匹配即可。詳細電容值如表1所示。

表1 采樣及前饋電容值Tab.1 Parameters of sampling and feed-forward capacitors

2.2 調制器各級OTA設計

本文采用全差分折疊共源共柵結構,其優點是可提供較大的直流增益和輸出擺幅。如圖5所示,OTA用PMOS管作為輸入級,以此來優化擺率、單位增益帶寬,減小低頻1/f噪聲。采用開關電容共模反饋電路控制OTA直流工作點。通過行為級仿真得到各級積分器輸出范圍及第一級積分器OTA的基本參數,對第二三四級OTA進行適當增益縮放,以達到節約功耗的目的。各級放大器的性能指標見表2。控制信號檢測電路主要是用來實現對輸出控制信號的準確檢測。

2.3 時鐘產生電路

積分器工作需要兩相非交疊時鐘控制,同時為了消除與輸入信號相關的溝道電荷注入,還需要同相時鐘的延時。一般設計中都是采用與非門和反相器鏈路來實現,為了增大時鐘的驅動能力在輸出級都串聯了逐級增大的延遲單元。

2.4 量化器

單位量化的ΣΔ調制器對量化器失調要求相對寬松,非理想因素如失調、非線性等都被調制器當做噪聲進行了整形所以對系統的性能影響很小。采用動態可再生鎖存比較器和SR鎖存器組成的量化器即可,該結構特點是無靜態電流,功耗低。

圖5 折疊共源共柵OTAFig.5 Folded-Cascode OTA

表2 運算放大器性能指標Tab.2 Performance of the operational amplifier

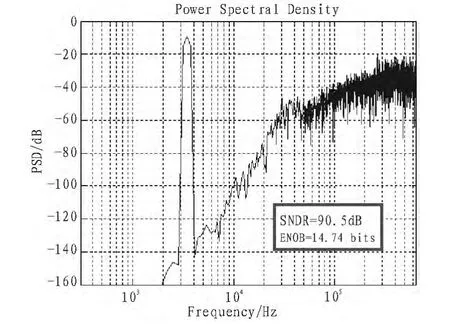

3 仿真結果

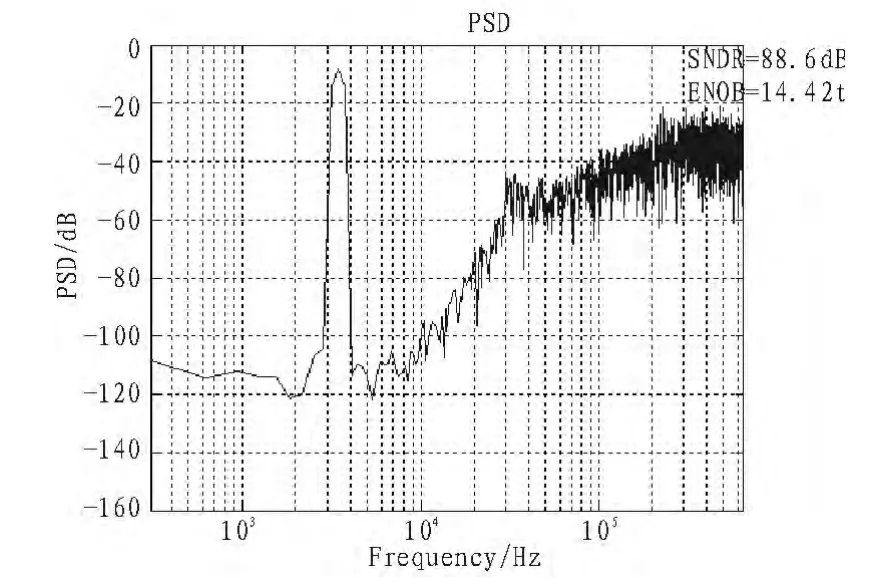

本文ΣΔ調制器采用SMIC 0.18μCMOS工藝實現,加入0.3 V、3.4 kHz正弦波,在電壓1.2 V,采樣時鐘為1.28 MHz的條件下,經過FFT得到功率譜密度,如圖6所示,SNDR達到88.6 dB,有效位數為14.42 bit,帶寬滿足10 kHz要求。調制器功耗為196μW。采用如下公式計算FOM值:

將本文研究結果與相關文獻結果進行對比,如表3所示。

圖6 輸出信號功率譜密度Fig.6 PSD of the output signal

表3 ΣΔ調制器性能對比Tab.3 Comparisons ofΣΔmodulator

4 結束語

文中針對智能傳感器節點低功耗應用,通過系統行為級建模確定ΣΔ調制器各項參數,及OTA性能指標,提高了設計效率。同時通過電路模塊進行低功耗分析,實現了一款低功耗高精度四階前饋單位量化ΣΔ調制器,該類前饋結構降低了對第一級積分器OTA設計要求,同時對后幾級OTA進行增益縮放,降低了功耗。該調制器可與數字濾波器構成高精度低功耗ΣΔADC,應用于物聯網節點芯片中。

[1]Wu R,Huijsing J H,Makinwa K A.A 21b ±40mv range read-out ic for bridge transducers[C]//Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, IEEE, Year:110-2.

[2]Chiu Y,Nikolic B,Gray P.Scaling of analog-to-digital converters into ultra-deep-submicron CMOS[C]//Custom Integrated Circuits Conference,2005 Proceedings of the IEEE 2005,IEEE,Year:375-82.

[3]Le H-B,Lee S-G,Ryu S-T.A regulator-free 84dB DR audio-band ADC for compact digital microphones[C]//Solid State Circuits Conference (A-SSCC), 2010 IEEE Asian,IEEE,Year:1-4.

[4]Michel F,Steyaert M.A 250mV 7.5μW 61dB SNDR CMOS SCΔΣmodulator using a near-threshold-voltage-biased CMOSinverter technique[C]//Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, IEEE, Year:476-8.

[5]Nam K,Lee S-M,Su D K,et al.A low-voltage low-power sigma-delta modulator for broadband analog-to-digital conversion[J].Solid-State Circuits, IEEE Journal of,2005,40(9):1855-64.

[6]Cao Z,Song T,Yan S.A 14 mW 2.5 MS/s 14 bit ΣΔ modulator using split-path pseudo-differential amplifiers[J].Solid-State Circuits, IEEEJournal of,2007,42(10):2169-79.

[7]Aziz P M,Sorensen H V.An overview of sigma-delta converters[J].Signal Processing Magazine, IEEE,1996,13(1):61-84.

[8]Goes J,Vaz B,Monteiro R,et al.3.7 A 0.9 VΔ Σ Modulator with 80dB SNDR and 83dB DR Using a Single-Phase Technique[J].2006,

[9]Kuo C-H,Shi D-Y,Chang K-S.A Low-Voltage Fourth-Order Cascade Delta-Sigma Modulator in 0.18-CMOS[J].IEEETransactions on Circuits and Systems I:Regular Papers,2010,57(9):2450-61.