基于CY7C68013A和FPGA的4路數據采集系統設計

智 丹,石云波,董勝飛,陳艷香,楊志才

(中北大學 電子測試技術國家重點實驗室 儀器科學與動態測試教育部重點實驗室,太原 030051)

數據采集系統是計算機智能儀器與外界物理世界聯系的橋梁,是獲取信息的重要途徑。通常數據采集系統主要通過RS232接口、RS485接口、ISA總線、PCI總線或EPP/ECP實現數據傳輸。采用傳統接口的數據采集設備存在以下缺陷:安裝麻煩;價格昂貴;受計算機插槽數量、地址、中斷資源的限制,可擴展性差,而通用串行總線USB的出現,很好地解決了這些問題[1]。

USB設備具有即插即用、接口數目多、數據傳輸速率快等優點,USB2.0最快可達到480 Mb/s,能夠滿足高速采集系統的要求。如果采用單獨的USB接口芯片,需要研發者對USB協議有十分全面的了解,并且能夠熟悉應用才能更好地處理USB總線事務,這無疑加大了編程設計人員的開發難度、延長了產品的開發周期[2]。CY7C68013A是一個內部嵌入微處理器的USB2.0接口芯片,支持USB2.0協議,只需要配置訪問一些寄存器和存儲器,就可以完成對USB數據口的數據傳輸,進而簡化了程序的設計,提高傳輸速率,增強了可靠性。

文中提出了一種基于CY7C68013A和FPGA數據采集系統的設計方案,主要完成彈體侵徹試驗中加速度信號的采集存儲,供其試驗后回收原始數據,通過上位機軟件在PC機讀取彈體侵徹中獲得的原始數據并對其進行拆分以及繪圖,進而供試驗后對其數據分析,從而對彈體侵徹試驗的各項指標進行評估和驗證。

1 系統總體設計

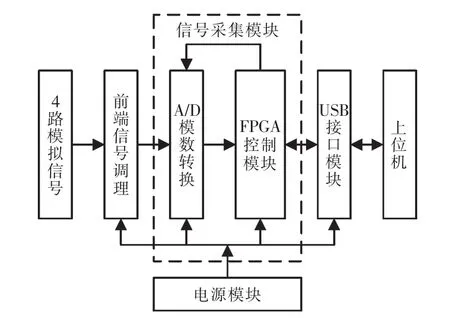

本文設計的數據采集系統主要由前端信號調理、數據采集存儲和數據傳輸3大部分組成。控制單元采用的FPGA是Xilinx公司生產的XC2S30芯片,該芯片擁有高達60個I/O口數量,216個可編程邏輯模塊,24 KB的雙口RAM。它的內核采用低電壓2.5 V供電,有靜態功耗低、成本低等特點。XCF01S作為它的配置芯片,由外部20 MHz的晶振提供時鐘信號。系統總體設計原理如圖1所示。

圖1 系統結構框圖Fig.1 System structure diagram

系統外部供電采用5 V,經電源轉換模塊轉換成 2.5 V、3.3 V 電壓,分別給 FPGA 內核、FPGA I/O及其它電路模塊供電。4路傳感器信號先經前端信號調理模塊放大調理,然后送入數據采集模塊。FPGA控制A/D轉換器對輸入模擬信號進行模數轉換并進行采集,再按照一定的幀格式存儲到Flash芯片中。數據傳輸過程中,上位機軟件通過USB口發送讀數指令,經CY7C68013A以一定的幀格式傳給上位機,將Flash存儲器中的數據讀到上位機顯示并分析處理。

2 系統硬件設計

2.1 前端信號調理模塊

前端信號調理模塊主要由RC高通濾波電路、運算放大電路、電壓跟隨電路組成。

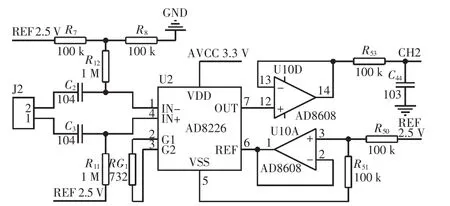

在彈體侵徹試驗中,傳感器信號主要為高頻沖擊信號(>1 kHz),YZ1-和 YZ+為傳感器的差分信號輸入端,在信號輸入端接RC高通濾波電路,可以很好地消除傳感器零位偏差對輸出零位的影響,如圖2所示。

圖2 信號調理電路Fig.2 Signal conditioning circuit

由于輸入信號比較微弱,需要經過運算放大電路對其進行放大后再進行采集。本系統采用ADI公司的AD8226芯片,對信號進行放大調理。AD8226支持單電源供電,配置方便,僅需要一個外部電阻來設置增益,增益范圍為1~1000,增益為50時,帶寬約為30 kHz。電路中放大倍數的計算公式為可以通過調整RG1的阻值來改變電路的放大倍數。

基準電壓跟隨電路主要是為4路AD8226芯片的REF引腳提供1.25 V的基準電壓,將AD8226的有效輸出范圍調至0~2.5 V,實現對正負差分信號的有效放大。經過AD8226放大的輸出信號進入電壓跟隨電路,可以提高帶載能力,實現前后信號隔離,提高抗干擾能力。接著信號進入RC低通濾波電路去除高頻噪聲之后輸出給A/D轉換器。

2.2 數據采集模塊

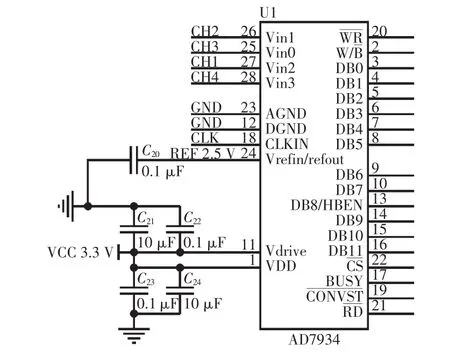

本系統數據采集采用的是ADI公司的4通道12位A/D轉換芯片AD7934,它采用5 V供電,內置1個精確的2.5 V片內基準電壓源,可用作模數轉換的基準電壓源[3]。該芯片擁有1個高寬帶、低噪聲的差分/保持放大器,可以處理高達50 MHz的輸入頻率,采樣的吞吐率可達1.5 MS/s。本設計中利用外部提供的時鐘信號,在20 MHz時鐘工作頻率下,采樣率達150 kHz。AD7934的外圍電路如圖3所示。

圖3 AD7934的外圍電路Fig.3 Peripheral circuit of AD7934

2.3 數據傳輸模塊

數據傳輸采用的是Cypress公司生產的EZUSB FX2LP系列的CY7C68013A,該芯片將USB2.0收發器、串行接口引擎(SIE)、增強的8051單片機及各種外圍接口集成于一體[4]。擁有480 Mb/s的高速傳輸速率和12 Mb/s的全速傳輸速率,芯片能自動檢測高速主機,并切換到高速模式下。

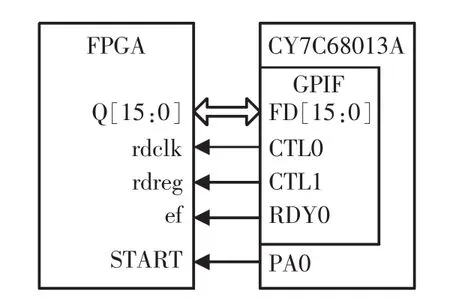

CY7C68013A的數據傳輸有3種不同的工作模式:GPIF主控模式、Slave FIFO模式和Ports模式。其中可編程接口GPIF模式是主機方式,可以通過軟件編程讀寫控制波形,幾乎可以對任何8/16 bit接口的控制器、存儲器和總線進行數據的主動讀寫,傳輸速率快,靈活性非常強[5]。本系統采用的就是通過GPIF模式來實現FPGA與外圍設備的數據通信。CY7C68013A與FPGA連接圖如圖4所示。

圖4 硬件連接圖Fig.4 Hardware connection diagram

3 系統軟件設計

3.1 FPGA程序設計

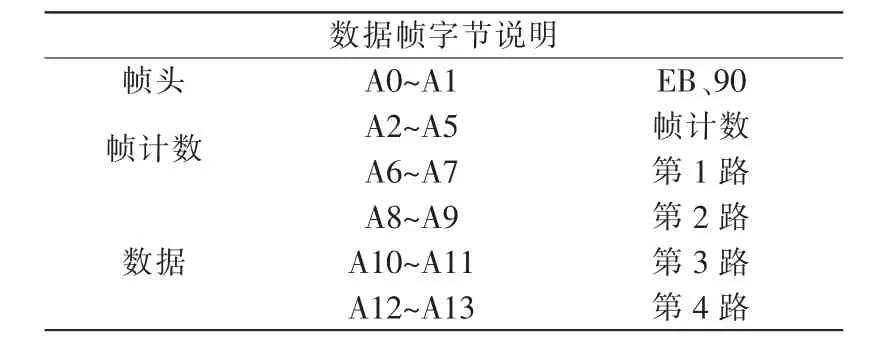

本系統FPGA的程序設計在Xilinx的ISE10.1開發環境中用VHDL語言實現,FPGA主要程序模塊有A/D采集控制模塊、Flash存儲控制模塊、CY7C68013A傳輸控制模塊等。FPGA與AD的接口程序根據AD的時鐘輸出信號將AD輸出的數據正確存入FPGA的FIFO中,為了便于數據的存儲和分離,模擬量經AD7934轉換后的數字量需要按照一定的編碼方式進行編碼,本設計轉換的數據采用如表1所示的通訊數據幀編碼方式進行編碼。

表1 通訊數據幀編碼方式Tab.1 Encoding of communication data frame

由表1可知,一幀數據為14個字節,A0為低字節,A13為高字節。A0~A1為幀頭,用于數據處理時判斷數據幀的起始位置;A2~A5為幀計數,用來判別采集數據的數據量和驗證存儲數據的完整性;A6~A13字節為4路數據,其中2個字節構成1路數據,分別對應每個通道采集到的模擬信號。

FPGA將編碼后的數據存儲到Flash中,本系統采用的Flash存儲器是SAMSUNG公司生產的K9K8G08U0E,該芯片是一種NAND Flash Memory,具有1 G×8 bit的數據存儲空間和256 Mb的空閑空間,空閑空間可以用來存儲壞塊信息及其它分區劃分信息。FPGA控制Flash數據存儲流程如圖5所示。

在FPGA將FIFO中的數據存入Flash之前,FPGA先對Flash進行檢測,判斷存儲空間是否有數據,如果為空則進行寫入,如果有數據則停止寫入,并通過LED閃爍警示,這樣可以防止已回收的存儲器由于誤啟動造成侵徹數據被覆蓋、丟失。寫入數據時,先向Flash寫數據命令80H,然后寫入數據存入的具體地址,之后執行寫入命令10H,此時Flash開始進行寫入數據工作,此時R/B信號呈現低電平,表示Flash處于寫數據的工作狀態,待R/B信號變為低電平時,表示Flash寫數據的工作狀態結束。最后,讀取狀態寄存器,如果I/O0=0則說明數據寫入成功,反之寫入失敗。

圖5 Flash數據存儲流程圖Fig.5 Flow chart of flash data storage

3.2 PC應用程序設計

應用程序主要包括動態鏈接庫和操作界面程序,其中動態鏈接庫只需調用DLL68013.dll封裝的API函數,先將DLL68013.dll復制到系統盤的“C:WindowsSystem”下面,然后在Visual Basic的集成編程環境下的模塊Module中對引用動態鏈接庫DLL68013.dll的API函數進行聲明,通過調用通用驅動程序來完成對外設的控制和通信[6]。操作界面程序采用Visual Basic來編寫完成,所實現的功能包括對USB設備連接、設備檢測、數據回讀、數據擦除、分析處理等。

4 實驗驗證

利用信號發生器向4路模擬輸入端輸入1 kHz峰峰值為20 mV的正弦信號,采集系統對此測試信號進行采集、模數轉換、編幀和存儲,將存儲的數據通過USB上傳給上位機,通過上位機軟件對采回的4路數據進行分離、分析繪圖,繪圖如圖6所示,可以清楚地看到4路正弦曲線。通過多次連續的采集和分離數據測試,驗證了系統的準確性和可靠性。

圖6 4路數據驗證曲線Fig.6 4-way data validation curve

5 結語

本文基于CY7C68013A和FPGA設計的4路數據采集系統,能夠對傳感器信號進行實時采集、存儲,通過采用CY7C68013A接口與上位機進行通信,實現了回傳數據、存儲、顯示并分析數據的功能。通過實驗驗證,該系統具有體積小、傳輸速率快、高采樣率、高可靠性、功耗低等特點,可廣泛應用于彈體侵徹試驗中對加速度信號的采集存儲。

[1]賈寶金.基于USB的數據采集系統的研究與設計[D].河北:河北工業大學,2007.

[2]李俊萍,靳鴻,張艷兵.基于CY7C68013A的存儲器測試臺的USB 通信設計[J].電子器件,2014,37(2):361-366.

[3]楊小勇,葛彥麟,毛瑞娟.基于FPGA+A/D的數據采集設計及驗證[J].西安郵電學院學報,2011,16(1):98-102.

[4]吳磊,郭超平,申世濤.基于CY7C68013與FPGA的便攜式數據采集系統[J].計算機應用,2012,32(S1):164-166.

[5]付斌,丁月寧,黃勇,等.基于USB的便攜式導彈導航遙測艙數據采集系統設計[J].計算機測量與控制,2014,22(3):790-792.

[6]代月松,董力科,孫正席,等.基于CY7C68013A的并口轉USB口數據采集系統設計[J].電子設計工程,2011,19(16):42-44.