多通信接口外系統等效器設計

張亮紅,杜文略,劉文怡

(中北大學 儀器科學與動態測試教育部重點實驗室 電子測試技術重點實驗室,太原 030051)

隨著科技的快速發展,航空航天設備、軍用系統等高科技產品的開發規模和復雜程度都有了質的飛躍。自動測試系統ATS的高可靠性使其逐漸替代人工檢測并廣泛地應用于航空航天領域,為航空航天產品研發、生產等各個環節提供了有效保障。測試系統及控制系統有許多接口,為了在實驗室情況下對測量系統各種對外接口進行全面測試,提高等效器應用的廣泛性,設計了基于FPGA的多通信接口的外系統等效器,使其可以與PCI接口、USB接口或以太網接口的測試系統進行聯合使用[1]。

該等效器采用模塊化設計,以增強其通用性、可靠性、智能性,而且出現問題后可以高效解決。等效器系統通過PCI接口、USB接口或以太網接口接收上位機的下發命令,再通過光電轉換模塊經光纖將命令、數據與背板進行交互,再由背板通過RS422接口向各個功能板卡轉發命令控制相應板卡電路產生相應信號,各個信號在不同板卡上,避免其相互干擾,且方便進行功能改造及升級。

1 系統的總體結構

等效器系統框架如圖1所示,外系統等效器主要包括雙模通信接口板、背板、模擬信號板、指令信號板、數字量信號板、脈沖信號板,實現外系統等效器的信號源功能。

圖1 系統總體結構Fig.1 System architecture

工控機通過VB編寫的上位機軟件與外系統等效器多通信接口板的PCI接口、USB接口或以太網接口進行命令、數據的交互。外系統等效器采用模塊化設計方式,按照功能設計板卡,外系統等效器通過光纖將多通信接口板接收的上位機命令及數據傳輸給背板,再通過背板RS422接口將命令轉發至各功能板。各功能板接收到背板發送的數據或命令信息進行命令解析,按照寄存器執行各通道功能[2]。

2 系統硬件設計

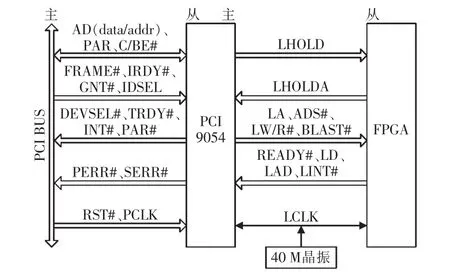

2.1 PCI接口電路設計

PCI總線傳輸速率高,數據位為32位時,數據傳輸最大可達132 MB/s,當數據寬度擴展為64位時,傳輸速率可達到264 MB/s。因此本設計將PCI接口作為與上位機通信的接口之一。PCI9054是PXI公司的PCI接口芯片,它集成了PCI接口協議,在本設計中采用PCI9054作為PCI總線與FPGA的橋接芯片,PCI9054符合PCI2.2協議,工作時鐘支持33 MHz和66 MHz,數據總線支持32位和 64位,它與FPGA的硬件接口框圖如圖2所示。

圖2 PCI與FPGA硬件連接圖Fig.2 Hardware connection diagram of PCI and FPGA

PCI9054的數據傳輸模式有3種:主模式、從模式、DMA模式。本設計選擇PCI9054從模式,PCI9054作為本地總線主控設備通過和進行本地總線仲裁。仲裁過程為當PCI9054收到PCI端發出的讀寫命令后,向LOCAL端即FPGA發出信號,表明PCI端已經準備就緒,返回信號至PCI9054,表明雙方都已準備好,可以進行正常的數據傳輸,否則需等待12個CLK就釋放總線。

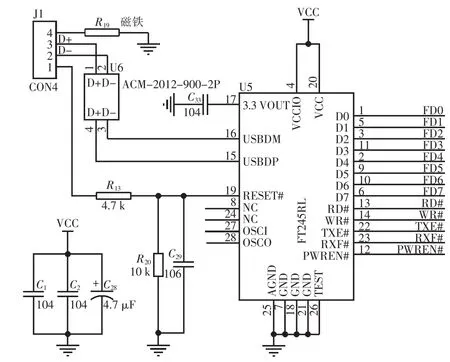

2.2 USB接口電路設計

USB接口是PC機常用的通信接口之一,以數據傳輸可靠穩定、通用性強、擴展性強、支持熱插拔等優勢廣泛應用于各個領域的產品開發。FTDI公司的FT245L避免了計算機驅動程序及對其固件程序開發,有效縮短開發周期,傳輸速率1 MB/s可以滿足本設計要求。FT245RL接口電路如圖3所示,FT245RL有總線供電和自供電2種供電模式,本系統功耗較大,設計中選擇自供電模式。FT245RL供電電壓支持3.3 V~5 V,設計中選用5 V供電以滿足大功耗需求。

圖3 正弦交流信號電路圖Fig.3 Circuit diagram of sinusoidal AC signal

為了降低外界及電磁干擾對USB接口數據傳輸造成的影響,一方面在USB接口電源接口需增加磁珠以減少設備與主機的干擾,另一方面在USB接口數據傳輸線中串入濾波器ADCM2012減少紋波引起的干擾。

2.3 以太網接口電路設計

本系統選用WizNet公司的W5300設計以太網接口與主機通信。此芯片集介質訪問控制管理、物理層控制、固件通信協議于一體,大大簡化了接口設計工作,提高了設計效率。設計中W5300采用直接尋址模式,FPGA將W5300配置成接收模塊,在直接尋址模式下,FPGA通過地址總線可以訪問W5300的內部寄存器。以太網與FPGA的連接如圖4所示。

圖4 W5300與FPGA管腳連接圖Fig.4 Pin connection diagram of W5300 with FPGA

設計中BIT16EN為高電平,設置為16位數據總線;TEST_MODE[3:0]和 OP_MODE[3:0]引腳接地,配置為全功能自動握手工作模式;W5300與RJ45之間接入隔離變壓器,既能提高穩定性和抗噪性又能保護接口電路[3]。

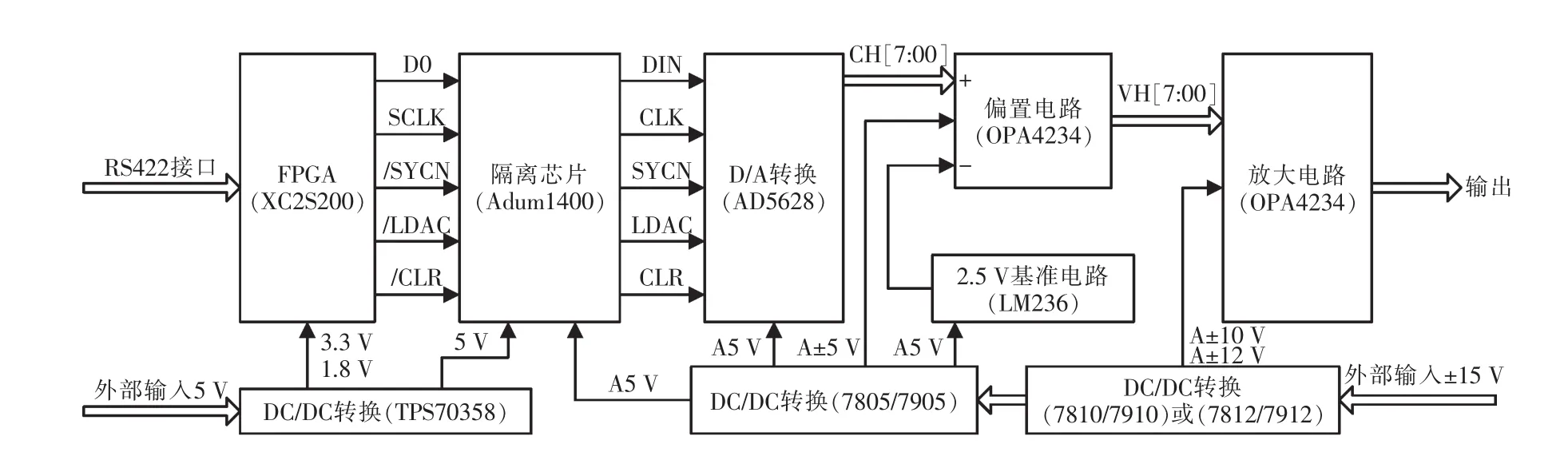

2.4 模擬量板電路設計

模擬量板的電路設計中,數字隔離電路設計、D/A轉換電路設計及調理電路設計是設計關鍵。此板卡主要功能是通過FPGA控制輸出48路12 bit包含數字量信息的串行數據,經過ADuM1400進行數模隔離后由AD5628實現DA轉換,再經軌到軌的運算放大器OPA4234進行電壓偏置、電壓放大或電壓跟隨, 得到-10 V~10 V、-5 V~5 V、0~5 V、-5 V~0的直流量。對于不同幅值的直流量信號,上位機通過控制寄存器及命令配置改變數字信號,通過DA轉換產生小幅度的電壓變化,經過信號調理電路得到所需電壓。一般數模轉換會采取DA轉換芯片與模擬開關相結合的方法實現,而本設計中1片AD5628可以通過芯片內部寄存器實現8路DA模擬輸出,替代了模擬開關的功能,優化了設計。如圖5所示以1片AD5628八路模擬量輸出為例介紹了模擬板硬件原理圖設計。

3 系統控制邏輯設計

3.1 PCI9054控制邏輯設計

FPGA對PCI9054邏輯控制過程如下:

(1)復位。當全局復位信號reset#使能,狀態機進入全局復位狀態;

(2)仲裁。PCI9054通過有效hold來申請本地總線,若hold置高,表示PCI總線已經準備好數據,FPGA檢測到hold有效后,向PCI9054返回hold有效值(高電平),說明PCI總線和本地總線都已準備好,可以進行下一步操作[4];

(3)啟動讀寫操作。FPGA檢測地址鎖存信號ads#是否有效,ads#為低電平意味著開啟了新的總線訪問有效地址,可以進行讀寫操作;

圖5 模擬量板硬件電路設計Fig.5 Hardware circuit design of analog board

(4)讀寫操作。FPGA檢測PCI9054的wr來確定是讀操作還是寫操作,wr為低進入讀模式,否則進入寫模式,在讀模式中,FPGA會讀取對應地址寄存器中的內容,包括讀取PCI卡的狀態信息、讀取批量的上傳數據。在寫模式中,通過判斷寄存器地址,向FPGA的緩存寄存器中寫入32位命令,并按照標準協議對32位命令進行打包下發。

3.2 W5300控制邏輯設計

系統中主要以FPGA控制W5300實現以太網通信,在正確配置之前先對其進行初始化,分為3步。

第1步建立后綴名為coe的文件:先建立后綴名為txt的文本文檔,定義數據的進制,以及定義寄存器地址及寄存器的值,每個寄存器地址和值之間以逗號結束,然后將后綴名改為coe文件;

第2步在ISE10.1軟件中新建一個IP core,并將其命名為rom,深度為64,寬度為16,讀取方式為只讀。按照索引載入第一步建立的后綴名為coe的文件。點擊生成,就可以生成rom;

第3步編寫VHDL程序,并讀取IP核中的數據[5]。

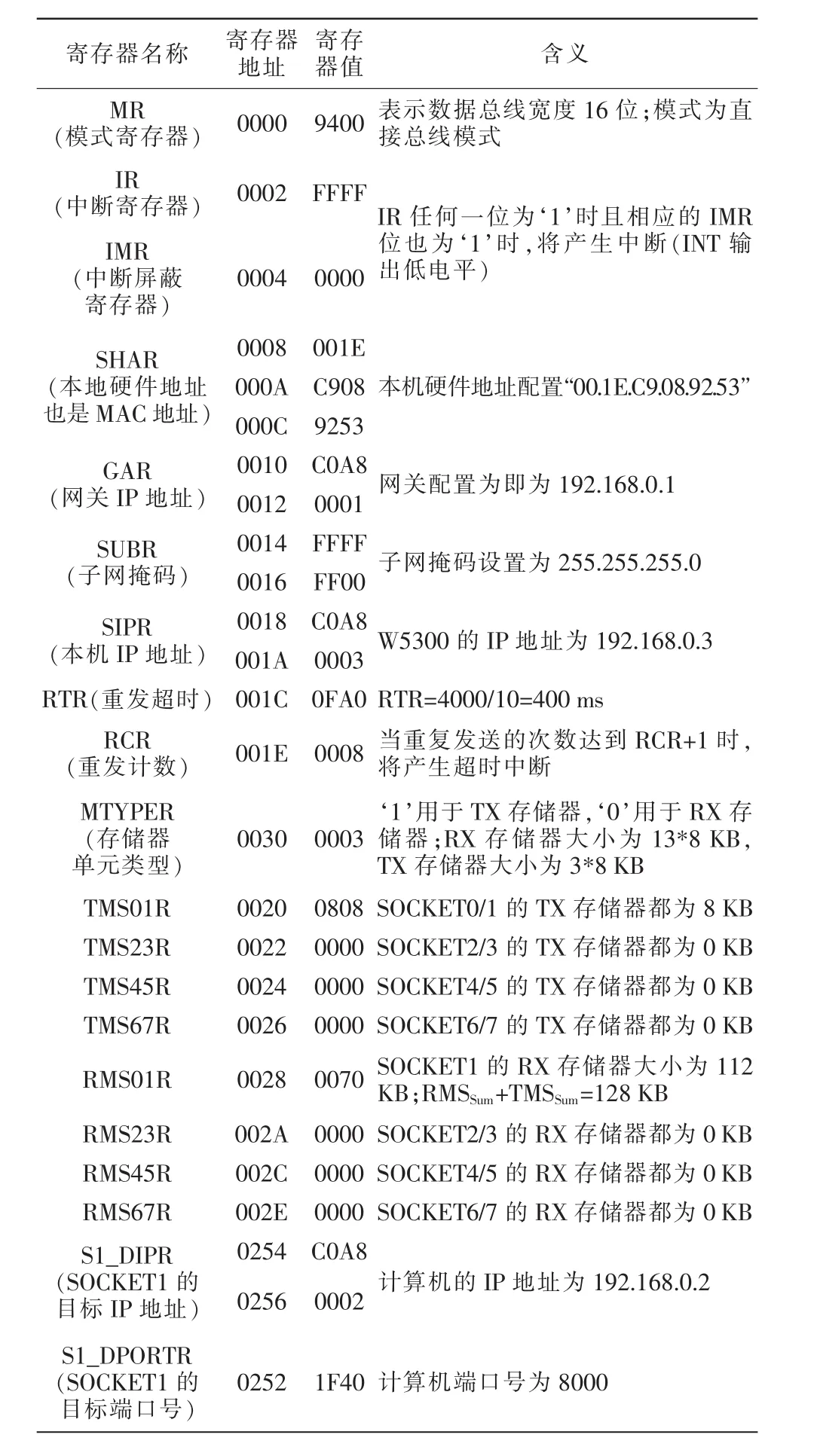

data.coe文件中存儲的寄存器值及其含義如表1所示。

表1 寄存器值及其含義Tab.1 Register values and meanings

4 系統試驗結果與分析

以產生的PCM碼流為例,PCM碼流的檢測需要另一塊數字量板實現發送字同步信號、位同步信號,并將接收到的PCM碼流上傳到上位機進行檢測。如圖6所示為測試板發出的字同步、位同步信號[6]。

圖6 測試板字同步和位同步信號Fig.6 Test board word synchronization and bit synchronization signal

如圖7所示為在位同步上升沿發送的一個PCM數據,測試系統接收PCM數據會在位同步的下降沿接收。

圖7 位同步信號與PCM信號Fig.7 Sync signal and PCM signal

測試板收到PCM數據會上傳至上位機,上位機會存儲數據文件,如圖8所示。此數據包設定模式為遞增數,幀頭、幀尾分別設為0xEB90、0x146,幀長度設為256字節。

圖8 PCM碼流數據文件Fig.8 PCM stream data file

5 結語

本文研究設計了一種應用于測量系統與飛行器控制系統的等效接口,產生各種測試所需的信號,以達到在實驗室、總裝廠以及技術陣地能全面模擬外系統配合測量系統進行系統測試。通過對系統實測數據和波形的分析結果顯示,系統能準確通過PCI、USB或以太網接口接收上位機發送的命令,控制各個功能模塊產生所需的信號,已成功用于某航天測試系統中。

[1]蘇虎平.集成多總線的等效測試系統設計與實現[D].太原:中北大學,2013.

[2]連恒興.集成多總線接口的外系統等效器設計與實現[D].太原:中北大學,2012.

[3]李勛,劉文怡.基于FPGA的以太網接口設計與實現[J].自動化與儀表,2014,29(5):57-60.

[4]任永峰.飛航導彈遙測匹配裝置自動監測系統研究[D].太原:中北大學,2000.

[5]陳嫣然,張會新,鄭燕露.基于PCI9054的通信卡設計[J].電視技術,2012,36(5):33-34.

[6]蘇虎平,沈三民,劉文怡,等.基于USB和FPGA的多功能等效器設計[J].電視技術,2012,36(23):50-53.