基于FPGA的侵徹加速度信號采集系統設計

董勝飛 ,石云波 ,陳艷香 ,智 丹 ,楊志才

(1.中北大學 電子測試技術國防科技重點實驗室,太原 030051;2.中北大學 儀器科學與動態測試教育部重點實驗室,太原 030051;3.中北大學 儀器與電子學院,太原 030051)

現代戰爭中,為了攻擊如機場跑道、機庫、航母和高級指揮要地等各種高強度、綜合防護的高價值目標,相繼出現一系“智能型”的鉆地彈藥。為了實現彈體在到達對目標的最大毀傷效果時引爆,就要求彈載電子裝置既能識別不同層次目標,又能抵抗不同軟硬防護層產生的多次高過載沖擊。因此,要使引信在高沖擊下適時作用,就必須現場測試侵徹過程中的加速度信號[1-3]。

目前,現有的侵徹加速度測試技術仍以彈載存儲測試技術較為先進。這種測試方式能記錄膛內發射、出膛飛行和侵徹穿靶整個過程中的實時加速度,為彈體強度設計、引信可靠性設計、戰斗部安全性等各方面的分析提供準確直接的依據[4]。

文中提出一種基于FPGA和INA827的侵徹加速度信號采集系統的設計方案,用于彈體侵徹試驗中,3軸MEMS加速度傳感器電壓信號的采集存儲。

1 系統總體設計

系統采用Xilinx公司FPGA芯片XC2S30作為主控單元,完成數據采集、存儲和傳輸的時序控制。XC2S30擁有24 KB的雙口RAM,216個可編程邏輯模塊,I/O口數量達到60個,豐富的I/O資源能對FPGA靈活配置,采用低功耗2.5 V內核供電電壓,系統以XCF01S為配置芯片,由40 MHz的外部晶振提供時鐘信號,主要由前端信號調理、數據采集存儲和傳輸等部分組成,總體設計如圖1所示。

圖1 系統結構框圖Fig.1 System structure diagram

系統采用7.4 V鋰電池和4.5 V氧化銀電池構成雙電源供電,以增強彈載采存器供電系統的抗過載能力,提高系統的可靠性。經電源模塊轉成2.5 V、3.3 V電壓后,為系統各模塊、芯片供電。3軸侵徹加速度信號先經前端信號調理模塊放大調理,然后送入數據采集模塊,FPGA控制A/D轉換器對輸入模擬信號進行模數轉換、采集,再按照一定的幀格式存儲到Flash芯片中。數據回收時,上位機通過USB口發送命令,經FT245RL將上位機指令轉換為并行數據,FPGA通過識別FT245RL轉換的數據指令,把Flash中的數據上傳至上位機進行顯示、處理分析。

2 系統硬件設計

2.1 前端信號調理模塊

前端信號調理模塊主要由RC高通濾波、儀表運算放大、有源低通濾波和電壓跟隨器組成。

在彈體侵徹試驗中,沖擊加速度信號具有較高的高頻成分,尤其在對花崗巖、鋼靶等硬目標侵徹時,沖擊加速度信號頻率可達20 kHz以上。因此,為保證采集的信號不失真,就需前端信號調理電路有較高的帶寬。系統采用TI公司的INA827芯片作為調理電路的主放大芯片,它是一款低成本單電源儀表放大器,通過單一外部電阻器RG可在5~1000倍之間設定任一增益,增益G=80 kΩ/RG+5。此放大器具有較高的帶寬,放大100倍時帶寬可達150 kHz,線性失真度小于0.0005%,且功耗極低。

如圖2所示,VIN-和VIN+為壓阻加速度傳感器的差分信號輸入端,在信號輸入端接一RC高通濾波電路,可以很好地消除傳感器零位偏差對輸出零位的影響。濾波后信號接入INA827儀表放大器進行放大,放大增益G1可由R5、R6的串聯阻值RG設置。

圖2 信號調理電路Fig.2 Signal conditioning circuit

為了提高系統對低靈敏度傳感器信號的處理采集能力,并進一步增大系統的工作帶寬,對IN-A827放大后的信號進行了二級放大。由基本運算放大器、電容、電阻構成一階有源低通濾波電路,可實現對信號的二級放大、低通濾波,放大增益G2可由R7、R10設置。電源分壓后,經電壓跟隨器為3個通道的INA827芯片、二級放大同相輸入端提供基準電壓VREF。經計算,整個調理通道的輸出電壓為

設計中將一級放大增益設置為66.54,第二級放大增益設置為3,可得到近200倍的信號放大,且理論帶寬超過100 kHz。將基準電壓VREF設置為1.65 V,可實現加速度傳感器正負量程的信號調理。調理電路將傳感器信號處理為0~3.3 V的標準信號后輸出至A/D轉換器。

2.2 數據采集模塊

系統A/D轉換器采用的是ADI公司的AD7934芯片。AD7934是12位高速、低功耗、逐次逼近型(SAR)模數轉換器,采用2.7 V~5.25 V單電源供電,最高吞吐量達1.5 MSPS。內置一個低噪聲、寬帶寬、差分采樣保持放大器,可處理最高達50 MHz的輸入頻率[5]。AD7934具有4個帶通道序列器的模擬輸入通道,可以通過預先編程選擇通道轉換順序。

設計中AD7934采用3.3 V供電,基準電壓引腳REF外接一個精確的3.3 V電壓源用作模數轉換的基準電壓,從而將轉換量程設置為0~3.3 V。利用外部提供20 MHz時鐘信號,采樣率達400 kHz。AD7934的外圍電路如圖3所示。

圖3 AD7934的外圍電路Fig.3 Peripheral circuit of AD7934

2.3 數據傳輸模塊

系統數據傳輸接口采用的是FTDI公司USB通信接口解決方案FT245RL。FT245RL無需編寫片內固件程序,在內部硬件邏輯的控制下即可實現USB串行協議與并行I/O協議之間的自動轉換。FT245RL通過8位并行接口與FPGA、DSP、MCU等微控制器外設接口連接,實現信息和數據的交換。上位機通過USB接口與FT245RL傳輸數據,通信時只需在PC安裝FTDI公司提供的官方驅動程序,無需用戶編寫設備驅動,簡單的Matlab的GUI、VB、VC編程,就可很容易地進行上位機軟件開發。FT245RL的外圍電路如圖4所示。

圖4 FT245RL的外圍電路Fig.4 Peripheral circuit of FT245RL

3 系統軟件設計

3.1 FPGA程序設計

系統FPGA程序設計基于Xilinx ISE10.1開發環境由VHDL語言編寫,主要程序模塊有:A/D采集控制模塊、Flash存儲控制模塊、數據傳輸控制模塊等。FPGA與AD的接口程序設計中,根據AD7934工作時序,FPGA將12位配置數據通過DB0~DB11雙向數據總線寫入AD芯片,完成對A/D轉換的工作模式、轉換通道等配置。A/D轉換完成后,FPGA從雙向總線一次性把12位數據讀出并存入FPGA的FIFO中。

為便于數據的存儲和分離,經AD7934轉換后的數字量需按照一定的編碼方式編碼,設計中采用如表1所示的通訊數據幀編碼方式進行編碼。

由表1可知,一幀數據共14個字節,B0為低字節,B13為高字節。B0、B1為幀頭,用于數據處理時判斷數據幀的起始位置。B2~B5為幀計數,用來判斷存儲數據的完整性和計算采集的數據量。B6~B11字節為3路數據,其中2個字節構成1路數據,分別對應每個通道采集到的模擬信號。B12~B13為幀尾,用于數據處理時判斷數據幀的結束位置。

表1 通訊數據幀編碼方式Tab.1 Encoding of communication data frame

數據編碼后,FPGA將數據存儲到Flash中,系統采用的存儲器是SAMSUNG公司的NAND Flash K9K8G08U0E,具有8 Gb數據存儲空間和256 Mb空閑空間,空閑空間可用來存儲壞塊信息及其它分區劃分信息。將數據存入Flash之前,FPGA先對Flash進行檢測,判斷是否已存入數據,如果有數據則停止寫入,并通過LED提示,可防止已回收的存儲器由于誤觸發造成侵徹數據被覆蓋、丟失。

寫入數據時,先向Flash寫數據命令80H,然后寫要存入數據的地址,之后再寫入命令10H,Flash開始存儲數據,此時R/B信號清零,表示Flash處于忙碌狀態,待R/B信號置位時,表示Flash存儲數據完成,進入空閑狀態。最后,讀取狀態寄存器,如果I/O 0=0則說明數據寫入成功,反之寫入失敗。

3.2 PC軟件設計

USB設備的PC軟件設計包括設備驅動程序和用戶程序2部分。FT245RL與上位機通訊時,不需用戶編寫設備驅動程序,只要使用FTDI公司提供的2種驅動模式[6]:一種為VCP,將USB接口虛擬為串行通信端口,在PC上的編程和實現串口編程一樣,可利用串行通信控件來簡化上位機用戶程序設計,使用該驅動數據傳輸速率最大只達300 kb/s。另一種是D2XX驅動程序,通過調用驅動程序的動態鏈接庫直接訪問USB,在編寫用戶程序時只需調用FTD2XX.DLL中的函數,便可完成USB接口設備的讀寫操作,使用該驅動傳輸速率可達到1 Mb/s[7],本系統即采用D2XX驅動程序。

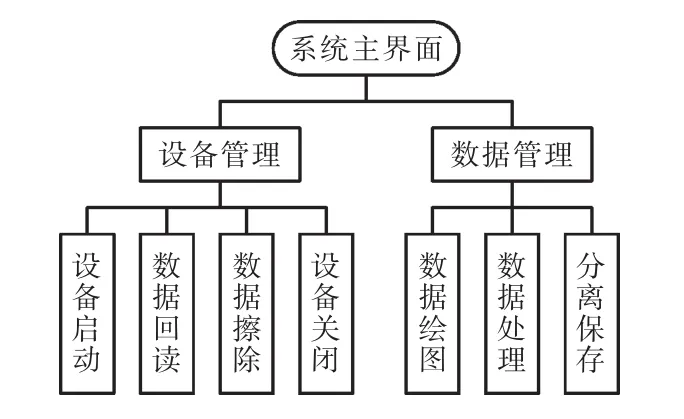

上位機用戶程序采用VB編寫,主要有數據讀取、擦除數據、分離數據等操作,結構圖如圖5所示。

圖5 上位機軟件結構Fig.5 PC software structure

4 實驗驗證

利用信號發生器、分壓電路,向3路模擬輸入端輸入峰峰值為8 mV,頻率為40 kHz的正弦信號,采集系統對此測試信號進行放大、模數轉換、采集、編幀和存儲。將存儲數據通過USB上傳給上位機,通過上位機軟件對采回的3路數據進行分離。用Matlab對分離后的數據進行繪圖分析,如圖6所示,可清楚地看到3路標準正弦曲線。通過多次連續采集和數據分離測試,驗證了系統的準確、可靠。

圖6 3路數據驗證曲線Fig.6 3-way data validation curve

5 結語

基于FPGA和INA827設計的侵徹加速度信號采集系統,可實現3軸MEMS加速度信號的放大調理、采集存儲,能夠滿足彈載侵徹加速度信號采集系統高精度、高帶寬、高采樣率、高集成度、低功耗等要求,可廣泛應用于彈體侵徹試驗中對加速度信號的采集存儲。

[1]宋萍,李科杰.硬目標侵徹武器高沖擊試驗和高過載傳感器技術國外發展概況[J].測控技術,2002,21(l):30-32.

[2]屈新芬,商順昌,楊晴.影響彈丸侵徹性能的因素分析及引信方案探討[J].信息與電子工程,2003,1(3):51-55.

[3]黃崢.國外兵器遙測技術的發展現狀及國內兵器遙測技術發展的需求[J].探測與控制學報,2000,22(1):3-5.

[4]景鵬.高g值沖擊測試關鍵技術研究[D].太原:中北大學,2009.

[5]楊小勇,葛彥麟,毛瑞娟.基于FPGA+A/D的數據采集設計及驗證[J].西安郵電學院學報,2011,16(1):98-102.

[6]安榮,任勇峰,李圣昆.基于FPGA和USB2.0的數據采集系統[J].儀表技術與傳感器,2009(3):49-51.

[7]王留全,焦海戀,安都勛.基于FT245RL的USB接口設計[J].國外電子元器件,2008(10):10-14.