微震動同步數據采集器的設計

嵇達龍,韓瑞瑞,孫 磊,顧正東,李紹鵬,陳 迅

(江蘇科技大學電子信息學院,江蘇鎮江212003)

巖體在變形的整個過程中幾乎都伴隨著裂紋的產生和擴展,其積蓄的能量以應力波的形式釋放,從而產生微震動事件.整個過程中的微震動信號從初始階段就包含了大量關于巖體受力變形破壞以及巖體裂縫活動的有用信息.通過監測、分析微震動事件,可以推斷巖體發生破壞的程度、位置,從而實現對巖體破壞的預測預報.上世紀90年代,微震動監測逐步發展并成為一項新的物探技術.由于微震監測范圍靈活,定位精度較高,逐漸成為邊坡、隧道、礦山和大壩等領域中巖質或混凝土工程結構穩定性監測的主要技術手段.在國外微震監測技術已發展成為采礦安全管理的一個有機組成部分,如在南非、加拿大、澳大利亞等國,已將微震動監測技術廣泛應用于礦山安全檢測,建立了200余套微震動監測系統.而國內還處于起步階段,從加拿大、南非等國家進口了少量微震動監測系統,用于凡口鉛鋅礦、冬瓜山銅礦等少數礦山企業[1-3].隨著我國礦山開采深度的日益增加,在高應力作用下誘發的巖爆災害嚴重制約礦山生產.微震監測技術通過實時監測巖體破裂情況,可以及時圈定災害危險區,從而在很大程度上實現災害的預測和防治,對減少傷亡事故具有十分重要的意義.

文中針對微震動信號的特點,結合高精度數據同步采集、高精度時鐘同步、網絡通信等技術,設計了微震動信號同步數據采集器,并在此基礎上構建了一套完整的微震信號數據同步采集系統.實際應用表明,該系統在信號的測量精度、時鐘同步精度等方面具有優異的表現,可滿足實際應用的需求.

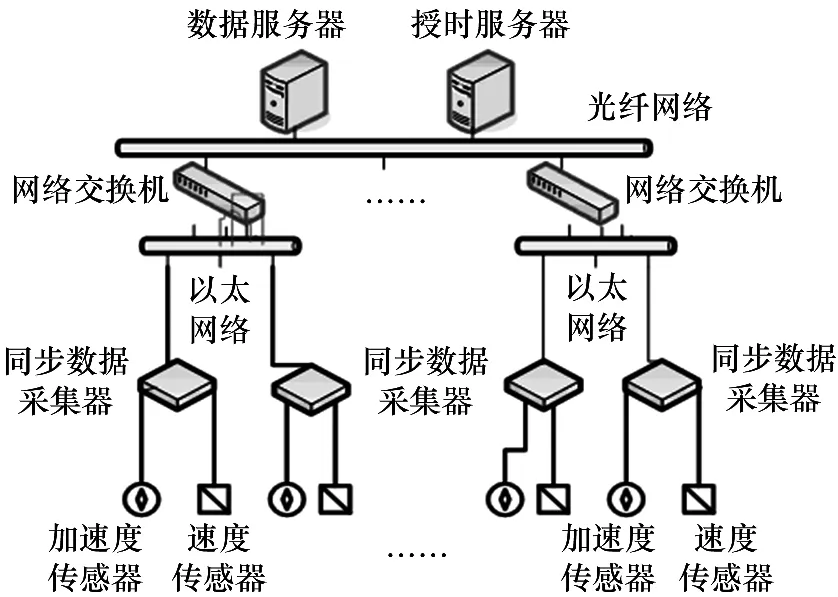

圖1 系統結構Fig.1 System structure

1 系統構成

系統主要由速度、加速度傳感器、同步數據采集器、網絡交換機、數據服務器和授時服務器幾部分構成(圖1).其中速度、加速度傳感器分別安裝在各個監測斷面和礦井坑道內,通過差分信號電纜將傳感器采集的模擬信號傳送到同步數據采集器,每個同步數據采集器具有12個數據采集通道,可以根據實際需要接入速度傳感器和加速度傳感器,用于巖層斷面微震信號的獲取.在礦井坑道內,根據需要安裝多臺同步數據采集器,以擴展監測點覆蓋范圍.每個同步數據采集器通過工業以太網接入,安裝在礦井井口的網絡交換機上,網絡交換機上行數據端口通過光纜與遠端服務器相連,實現數據遠程傳輸.為了保證系統的同步授時,每個同步數據采集器通過專用的網絡端口接入網絡交換機,通過交換機接入遠端的授時服務器,以實現全網同步數據采集器的時鐘同步.

系統運行時,速度和加速度傳感器將采集的反應微震動的速度和加速度的信號轉換成電信號、以差分信號的形式送到同步數據采集器.同步數據采集器完成速度和加速度信號的數字量化、采集數據時間戳的標記以及數據網絡傳輸等主要工作.每個同步數據采集器都有時間計數單元,為了保證所有同步數據采集器的時間的一致性,所有的同步數據采集器都需要與授時服務器通信.一般系統的時鐘同步可以采用GPS同步授時,但該系統主要用于礦井內,無法收到GPS信號,不能使用GPS授時的時鐘同步方式.因此該系統中采用基于IEEE1588協議的網絡時鐘同步算法,實現每個同步數據采集器與授時服務器的時間同步,從而達到系統內所有同步數據采集器節點的時鐘同步,為數據的同步采集提供高精度時間基準.

該系統中網絡交換機選用銳捷RG-IS2712G交換機,其具有8個千兆電口,4個千兆光口,完全滿足現場數據傳輸的需要,遠端設有數據服務器和授時服務器.系統中的同步數據采集器為自主開發設計的系統關鍵設備,文中將對同步數據采集器的結構和設計進行著重說明.

2 同步數據采集器

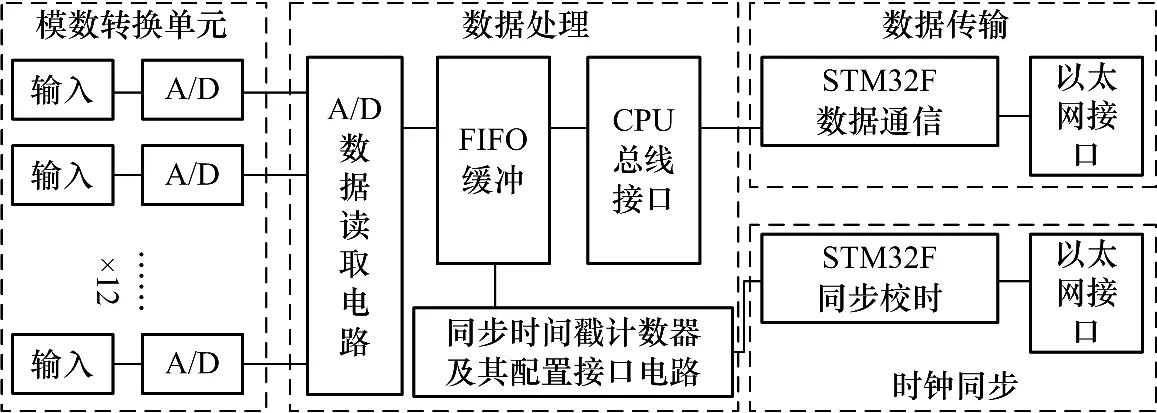

同步數據采集器內部主要有模數轉換單元、數據處理單元、數據傳輸單元、時鐘同步單元4部分組成(圖2).

圖2 同步數據采集器結構Fig.2 Structure of data synchronous collector

現場的速度和加速度傳感器采集的電信號以差分信號的形式通過電纜送到模數轉換單元,模數轉換電路由12片ADS1282模數轉換芯片構成,該A/D芯片的轉換位數為32位,最大采樣速率為4ksps.電路的12片ADS1282采取4片構成一組,共分成3組完成對12路信號的模數轉換.

數據處理單元采用FPGA可編程芯片實現,在FPGA內部將每片A/D芯片送來的32位串行數據轉換成32位并行數據,存入FPGA內部設計的FIFO數據緩沖存儲區.與此同時將每組數據采集對應的時間值作為時間戳一起存入FIFO數據緩沖存儲區.FIFO數據緩沖存儲器數據寬度為192位,深度為32個,當FIFO數據緩沖存儲區滿時,就向數據傳輸單元發出請求信號.

數據傳輸單元主要由一片STM32F429微控制器實現,該控制器采用32位ARM內核,從數據處理單元讀取數據并通過以太網接口將數據通過網絡發送到遠端的數據服務器.此外還接收遠端服務器發送的控制命令,實現對數據處理單元和A/D芯片的配置等工作.

時鐘同步單元主要由一片STM32F107微控制器構成,該控制器也為32位ARM內核.這部分電路主要通過網絡與遠端的授時服務器通信,實現基于IEEE1588協議的網絡時鐘同步.

2.1 數據處理單元FPGA實現

數據處理單元主要由ARM總線接口、A/D數據接收緩沖單元、時間戳單元、A/D配置單元4個主要部分構成,電路采用Verilog語言編寫設計(圖3).

1)ARM總線接口.主要完成FIFO數據讀取時序和ARM總線時序的轉換,主要將ARM總線的讀信號,根據ARM高位地址和片選信號,產生3個A/D數據接收緩沖單元所需的內部FIFO讀信號,該FIFO讀信號寬度需要嚴格限定為一個時鐘周期.

2)A/D數據緩沖單元.該單元主要由A/D數據讀取電路和FIFO存儲器構成.A/D讀取電路通過一個有限狀態機實現,其由空閑等待、串行數據讀取、FIFO寫入3個主要狀態構成.狀態機在空閑等待狀態下收到A/D芯片的數據轉換完成信號后,鎖存當前的64位時間戳數據,并將狀態機切換到A/D數據串行讀取狀態,A/D數據串行讀取狀態由多個子狀態構成,在主時鐘的驅動下可同時對4片A/D進行數據讀操作,每片A/D數據長度為32位,共計128位數據.在串行讀取過程中同時實現了數據的串行轉并行的轉換.32位數據讀取完成后,進入FIFO寫入狀態,在該狀態下將串并轉換后的128位數據和時間戳數據送到FIFO的數據寫端口,同時產生寬度為一個時鐘周期的FIFO寫控制信號,將數據寫入到FIFO存儲器.每當FIFO內數據緩存滿時,發出存儲器滿信號通知負責數據通信的微控制器將數據讀出.

3)時間戳單元.由時間戳計數器和時間戳配置接口構成,時間戳計數器由64位的微秒計數單元和10位的納秒計數單元兩部分構成,該計數器在100MHz主時鐘的驅動下實現10 ns的計數分辨率.

2.2 時鐘同步

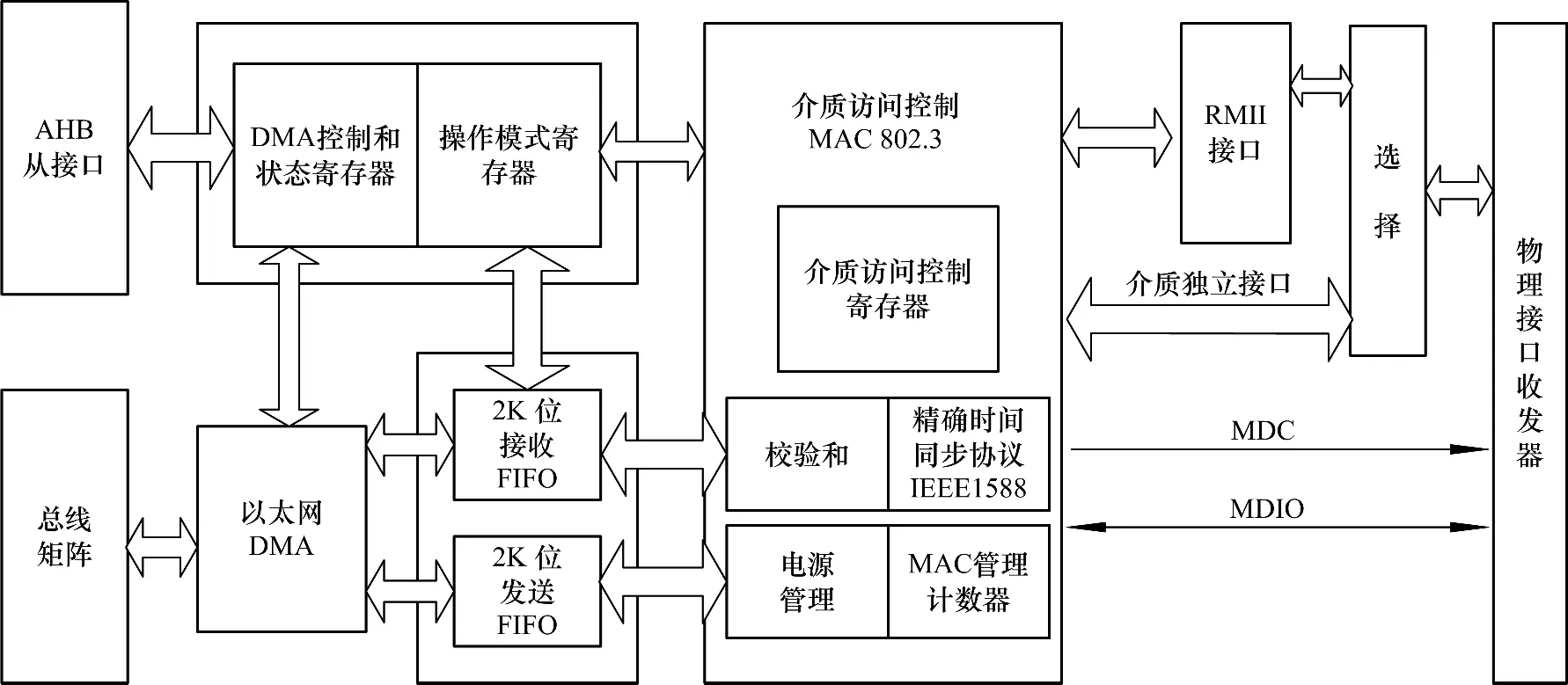

系統采用了IEEE1588時鐘同步協議,該協議將UDP/IP數據包作為消息傳遞的載體.在系統中,根據發送和接收時間的角色分為主節點和從節點,網絡中的所有同步數據采集器作為從節點,授時服務器為主節點.各同步數據采集器與授時服務器進行時鐘同步消息的交換,實現與授時服務器的時鐘同步,從而實現全網所有同步數據采集器的時鐘同步.時鐘同步的過程主要分為時鐘偏移測量和傳輸延遲測量兩個階段,時鐘偏移測量主要用于修正主從節點之間時鐘的偏移;傳輸延遲測量主要完成從節點與主節點之間的報文傳輸延遲的測量,以提高修正精度.目前實現IEEE1588時鐘同步協議的方式有:①采用 FPGA 的實現時鐘同步[4-6];②采用支持IEEE-1588協議的微處理器實現時鐘同步[7];③采用支持IEEE-1588協議的以太網物理層控制芯片[8];④采用純軟件方式實現[9].同步精度和實現復雜度兩方面考慮,最終選擇第二種方案,采用意法半導體的STM32F107VC微處理器實現時鐘的同步.

如圖4,在STM32F107VC的以太網MAC控制器單元內含有 IEEE1588處理單元,為實現IEEE1588協議的時鐘同步提供了硬件支持.該硬件提供兩個功能支持:①記錄接收和發送以太網幀的時間戳:當以太網幀通過MII端口與物理層以太網驅動芯片進行收發時,IEEE1588硬件模塊就會自動記錄時間戳,時間戳和數據幀的狀態信息一起,存放在相應的描述符里寄存器內;②提供粗調和精調的校正方法.

圖4 STM32F107VC以太網接口Fig.4 STM32F107VC network interface

3 系統實現

如圖5,數據同步采集器安裝在封閉鑄鐵的殼體內,所有的輸入輸出信號通過殼體上的插座與傳感器相連接.數據同步采集器本體按照IP65防護標準封裝,且滿足防爆要求.

圖5 數據同步采集器實物Fig.5 Data synchronous collector

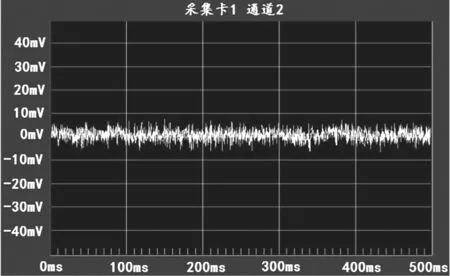

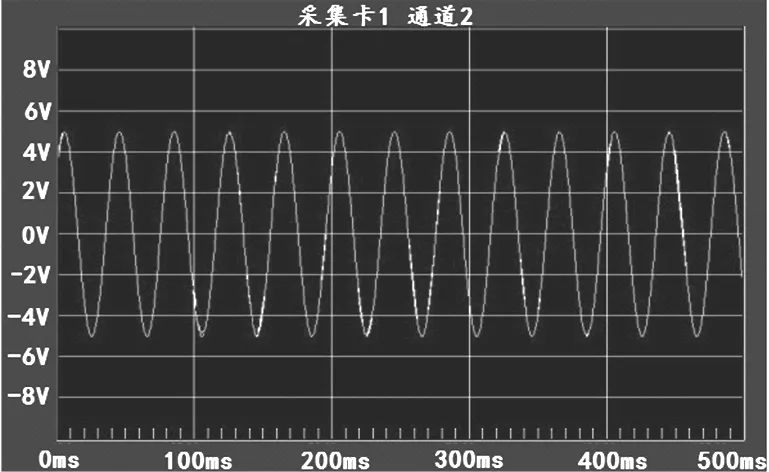

該裝置將傳感器置于無環境的震動的情況下,數據同步采集器采集的信號波形如圖6,其本地噪聲的峰值在20 uV以內.傳感器接口輸入5 V的標準正弦信號代替傳感器,大信號激勵情況下數據同步采集器采集結果如圖7,實際測試轉換信號最大幅度為±5 V,測量動態范圍可達到約116 dB,完全滿足微震動信號的采集要求.

圖6 本底噪聲采集數據Fig.6 Background noise data

圖7 大信號輸入采集數據Fig.7 Large signal data

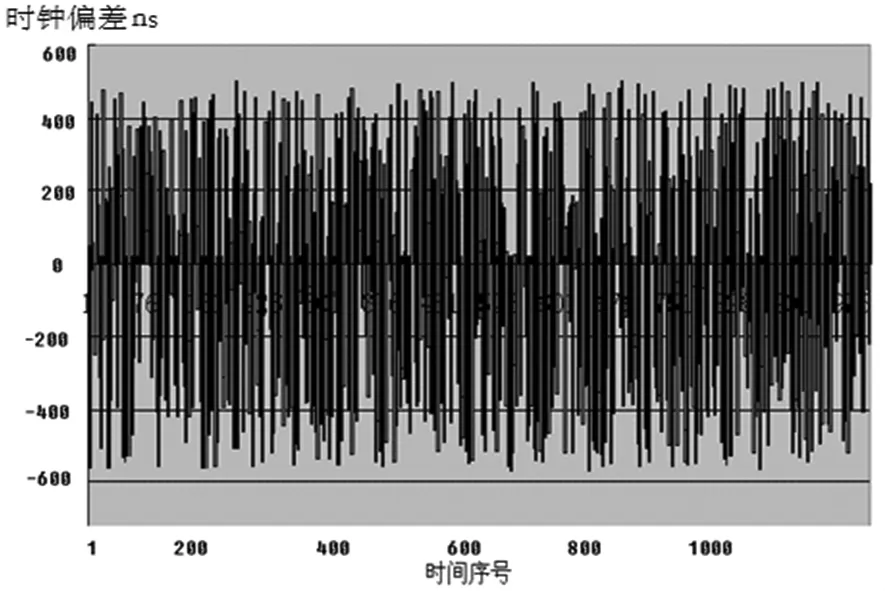

為了測試同步時鐘的誤差,微震動同步數據采集器和授時服務器均設有同步時鐘信號授時脈沖測試端,該測試端輸出信號類似于GPS的授時脈沖信號,頻率100 Hz,利用安捷倫DSO7052B示波器,同時觀察微震動同步數據采集器與授時服務器的授時脈沖測試端,并測量兩者之間的時間差.被測設備連續工作6h,每隔30 min捕獲測量一次.測量結果如圖8,系統的時鐘同步誤差在±600 ns范圍以內,所設計的微震同步數據采集器的設計要求為誤差±1000 ns.說明在STM32F107VC微處理器的基礎上,實現基于IEEE1588的時鐘同步方案,完全可以滿足設計要求,達到亞微秒級的同步精度.

圖8 時鐘同步誤差測試數據Fig.8 Clock synchronous error

4 結論

文中構建了微震動數據采集系統,并設計了基于FPGA和微控制器的數據同步采集器,測試結果表明其采集系統的時鐘同步精度可達到亞微秒級,可以滿足微震動監測的需求.

References)

[1] 李庶林,尹賢剛,鄭文達,等.凡口鉛鋅礦多通道微震監測系統及其應用研究[J].巖石力學與工程學報,2005,24(12):2048 -2053.Li Shulin,Yin Xiangang,Zheng Wenda,et al.Rsearch of multi-channel micro-seismic monitoring system and its application to Faokou lead-zinc mine[J].Chinese Journal of Rock Mechanics and Engineering,2005,24(12):2048 -2053.(in chinese)

[2] 唐禮忠,潘長良,楊承祥,等.冬瓜山銅礦微震監測系統及其應用研究[J].金屬礦山,2006(10):4l-44,86.Tang Lizhong,Pan Changliang,Yang Chengxiang,et al.Establishment and application of microseismicity monitoring system in Dongguashan coppermine[J].Metal Mine,2006(10):4l-44,86.(in chinese)

[3] 楊承祥,羅周全,唐禮忠.基于微震監測技術的深井開采地壓活動規律研究[J].巖石力學與工程學報,2007,26(4):818 -824.Yang Chengxiang,Luo Zhouquan,Tang Lizhong.Study on rule of geostatic activity base on micro-seismic monitoring technique in deep mining[J].Chinese Journal of Rock Mechanics and Engineering,2007,26(4):818 -824.(in Chinese)

[4] 孔令彬,文赫勝,陳向文.IEEE 1588精密時鐘同步關鍵技術研究[J].計算機測量與控制,2010,18(7):1585 -1586,1598.Kong Lingbin,Wen Hesheng,Chen Xiangwen.Research on key technology of IEEE1588 precision clock synchronization[J].Computer Measurement & Control,2010,18(7):1585 -1586,1598.(in Chinese)

[5] 謝型果.IEEE 1588時鐘同步報文硬件標記研究與實現[D].武漢:華中科技大學,2008:1-41.

[6] 方菁.基于FPGA的電力系統時鐘同步技術設計[J].武漢職業技術學院學報,2010,9(1):75 -78.Fang Jing.Design of power system clock synchronization technology based on FPGA[J].Journal of Wuhan Polytechnic,2010,9(1):75 -78.(in Chinese)

[7] 吳敏涼,石旭剛,張勝,等.基于IEEE 1588的同步以太網實現方式[J].單片機與嵌入式系統應用,2010(1):38-40.Wu Minliang,Shi Xugang,Zhang Sheng,et al.Synchronous ethernet implementation based on IEEE 1588[J].Microcontrollers & Embedded Systems,2010(1):38 -40.(in Chinese)

[8] 周飛,馬強,欒軍英,等.基于 DP83640的 IEEE1588協議實現方案[J].價值工程,2012,23:307-309.Zhou Fei,Ma Qiang,Luan Junying,et al.IEEE1588 protocol implementation based on DP83640[J].Value Enginnering,2012,23:307 -309.(in Chinese)

[9] 尤志堅.IEEE 1588協議分析與實現[D].上海:華東師范大學,2009:9-68.