基于Nios Ⅱ嵌入式處理器的SOPC中精度測頻電路的設計

董建樹,袁曉宇,王 惠,嚴宗瑞

(1.北京自動化控制設備研究所,北京100074;2.北京振興計量測試研究所,北京100074;3.海軍指揮學院,南京210016)

?

基于Nios Ⅱ嵌入式處理器的SOPC中精度測頻電路的設計

董建樹1,袁曉宇1,王 惠2,嚴宗瑞3

(1.北京自動化控制設備研究所,北京100074;2.北京振興計量測試研究所,北京100074;3.海軍指揮學院,南京210016)

中精度頻率測量電路主要用于中精度石英振梁加速度計頻率輸出的二次測量。通過比較并選擇合適的測量方法,詳細地分析了方案的理論誤差,研究基于Nios Ⅱ嵌入式處理器的測頻電路,將數據采樣和運算單元都集成在FPGA芯片中,形成一個片上操作系統SOPC,獲得了較高精度的測量結果。

測頻;FPGA;嵌入式處理;SOPC

0 引言

石英振梁加速度計是一種力敏感梁式諧振器約束的線性加速度計,其產生的諧振頻率表示為慣性系統的輸入加速度的函數。中精度頻率測量電路主要用于中精度石英振梁加速度計頻率信號輸出的二次測量,它將測量結果反饋給導航計算機。

由于石英振梁加速度計的標度因數較小,只能通過專用的測量電路進行精確的測量。在以前的設計方案中,一般通過數字邏輯電路與微處理芯片共同組合,實現要求的功能,很顯然,系統的集成程度不高,甚至無法滿足高速電路設計的要求。

這里提出一套新的基于Nios Ⅱ嵌入式處理器的SOPC中精度測頻電路方案,可以將設計中幾乎所有的邏輯模塊、運算模塊、控制模塊都高度集成在一片FPGA中,最大限度地減少了外圍電路的使用,同時片上可編程系統(SOPC)還具有設計周期短、開發成本低、設計靈活的優點。

1 測頻方案的選擇

頻率測試有很多種方法,目前常用的有四種方法:測頻法、測周期法、等精度法和相檢法。傳統的測頻法和測周期法在實際應用中具有較大的局限性,并且對被測信號的計數始終存在±1個字的誤差,測試精度與計數器中記錄的數值量相關,記錄數據越少,精度越低。所以,這兩種測試方法不能滿足較高精度的要求。

相檢法通過檢測信號的相位重合點,不僅實現了對被測信號的同步,也實現了對標頻信號的同步,大大消除了一般測頻系統中的±1個字的計數誤差。但是,當待測信號和標準信號的頻率值相等或成整數倍或分數倍的關系時,一旦兩信號有相位差,就不會有相位重合的時刻,則測量進程陷入死胡同。

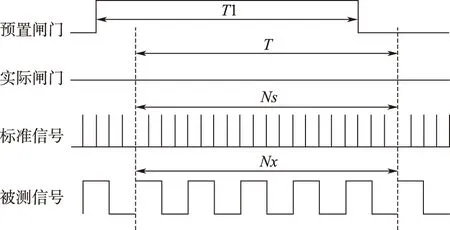

等精度測頻法中,由實際閘門控制兩個計數器分別對標準信號和被測信號同時計數,通過兩個計數器計數值之間的比較,計算得到被測頻率。實際閘門由根據測試需要設置的預置閘門經被測信號同步后形成,測量過程中,由于實際閘門與被測信號完全同步,消除了被測信號的±1個字的誤差,誤差的來源只有標準信號本身以及其計數誤差。

其基本原理如圖1所示。

圖1 等精度測頻原理時序圖Fig.1 The timing scheme of equallyaccurate frequency measurement

綜合考慮采用等精度頻率測量法,它能夠消除對被測頻率信號計數所產生的誤差,實現了寬頻率范圍內的中精度測量[1]。在設計中充分考慮引起誤差的各種因素,盡量將其降低到適當范圍,以滿足中精度的要求。

2 等精度測頻法的誤差分析

如果在一次實際閘門時間T中,計數器對被測信號的計數值為Nx,對標準信號的計數值為Ns。標準信號的頻率為fs,則被測信號的頻率為

(1)

由式(1)可知,若忽略標頻fs的誤差,則等精度測頻可能產生的相對誤差為

(2)

其中,fxe為被測信號頻率的準確值。

(3)

將式(1)和式(3)代入式(2),并整理得

(4)

由式(4)可知,測量頻率的相對誤差與被測信號頻率的大小無關,僅與閘門時間和標準信號頻率有關,這樣就實現了整個測試頻段的等精度測量。

閘門時間越長,標準頻率越高,測頻的相對誤差就越小。標準頻率可由穩定度好、精度高、頻率高的晶體振蕩器產生,在保證測量精度不變的前提下,提高標準信號頻率,可使閘門時間縮短,即提高測試速度。

前面將標頻信號作為一個穩定的常數,忽略了標頻fs的誤差,這里將它考慮進去綜合推導。

對式(1)進行微分得到被測頻率的誤差為

(5)

(6)

由式(6)可知,測量頻率的相對誤差與標準頻率的數值、準確度以及閘門時間相關。在硬件電路中,實際閘門時間T的準確度是與晶振頻率的準確度息息相關的,標準頻率信號也是直接或間接地來自晶振頻率。

3 片上系統的Nios Ⅱ軟核設計

當前嵌入式系統發展朝著小體積、低功耗、高性能的趨勢發展。MCU、DSP、FPGA三種處理器的結合是未來嵌入式系統發展的趨勢,可編程片上系統SOPC可以將三者完美結合起來。一般采用大容量FPGA作為載體,在片上定制MCU處理器和DSP功能模塊,同時設計其他邏輯功能模塊。NiosⅡ系統為用戶提供了最基本的IP核,設計師可以用它裁減合適的嵌入式系統。

NiosⅡ處理器是指在一個芯片上包含一個或多個可配置的CPU軟核、與CPU相連接的片內外設和存儲器以及與外設相連的接口等,所有的組件在一個FPGA上實現。NiosⅡ處理器具有定制指令、靈活的外設配置與地址映射、自動創建系統等特點,極大地提高了系統性能。

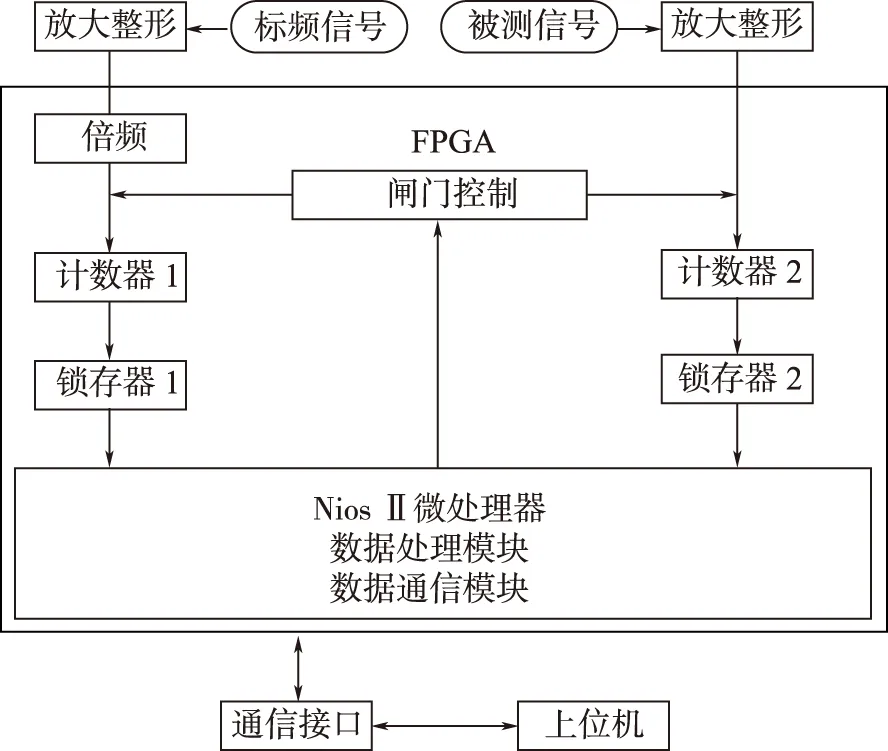

測頻電路的核心設計是SOPC片上可編程系統的設計,NiosⅡ軟核是片上系統的核心內容[2],測頻電路的原理如圖2所示。通過對FPGA芯片進行編程,能夠實現九路信號的計數、運算處理、串口通信三大復雜的功能。

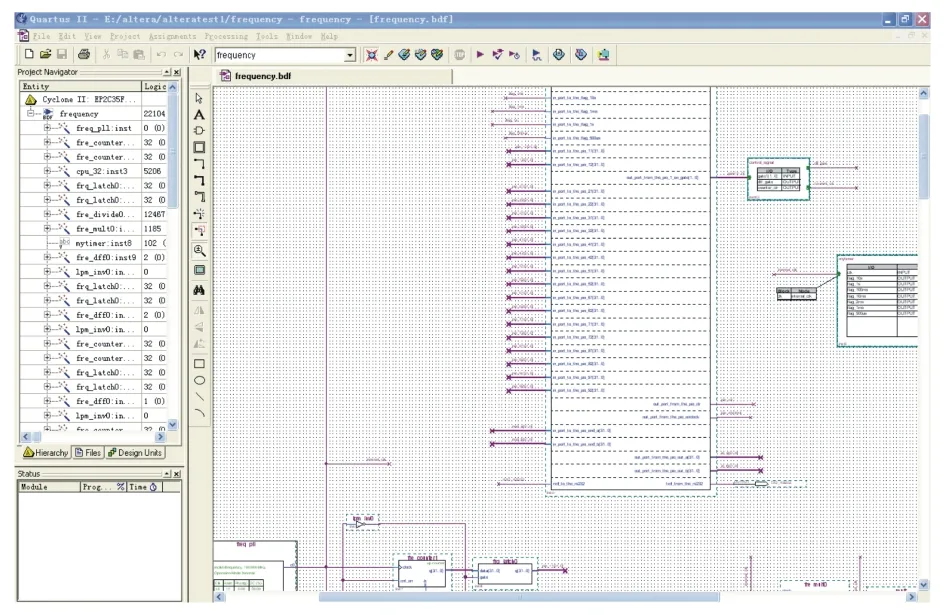

采用QuartusII軟件進行FPGA的硬件設計如圖3所示。標準頻率信號從外部的時鐘輸入端倍頻后獲得,經過整形后的被測信號輸入到觸發器中。NiosⅡ軟核控制預置門信號為高電平時,被測信號的上升沿通過觸發器的輸出端,啟動計數器計數;當預置門信號為低電平時,計數器關閉。隨后將數據送入乘除法器中進行運算,結果通過UART外設輸出。通過對實際數據容量的理論分析,設計采用了宏功能模塊來實現32位硬件乘法器和96位的硬件除法器。

圖2 測頻電路原理框圖Fig.2 The functional block diagram of frequency measurement circuit

圖3 FPGA的硬件設計圖Fig.3 The hardware design scheme of FPGA

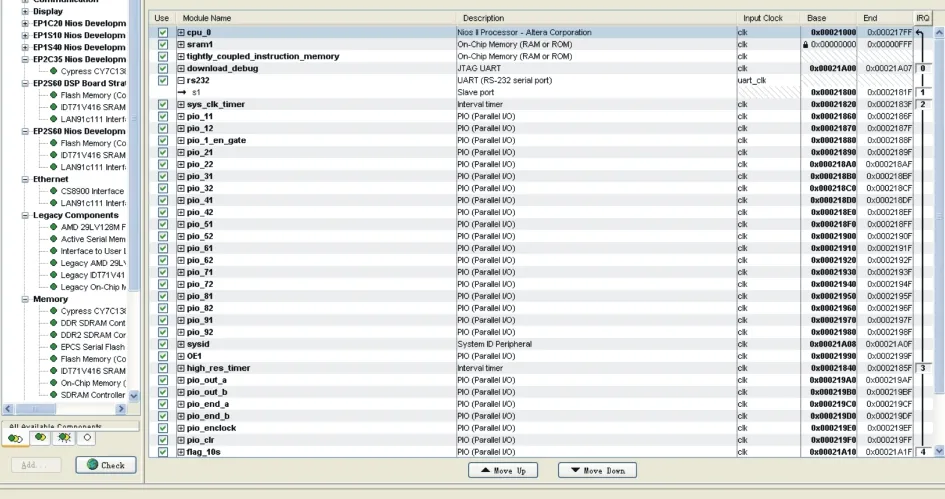

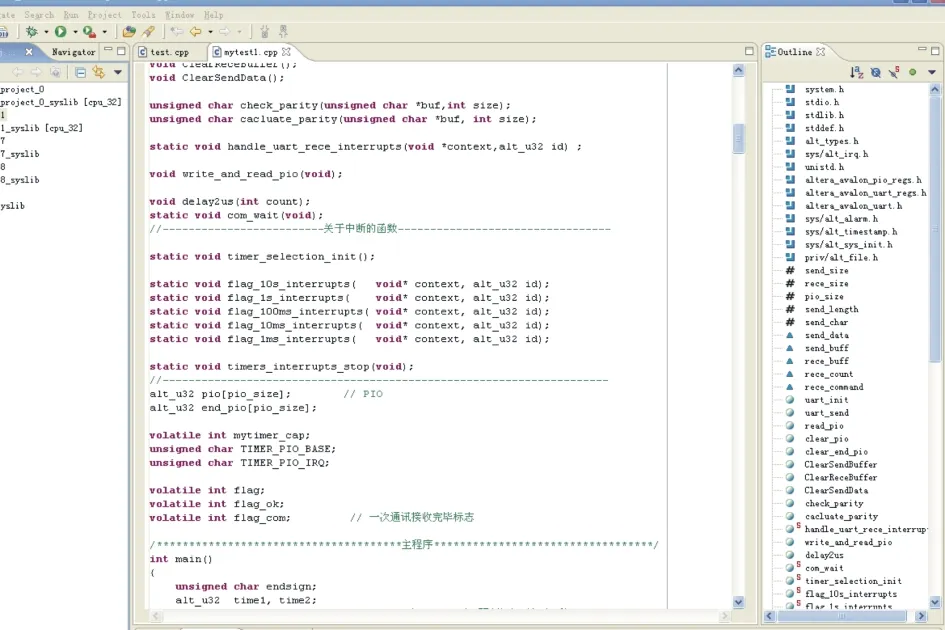

NiosⅡ作為一個可靈活定制的32位CPU,它的外設是可選的IP核或自定制邏輯[3],我們根據系統設計要求,通過SOPCBuilder向導式的界面定制裁減得當的SOPC系統。完整的基于NiosⅡ的SOPC系統作為一個軟硬件復合的系統,在開發時可以分為硬件、軟件兩部分,如圖4和圖5所示。

圖4 Nios Ⅱ硬件設計圖Fig.4 The hardware design scheme of Nios Ⅱ

圖5 Nios Ⅱ軟件設計圖Fig.5 The software design scheme of Nios Ⅱ

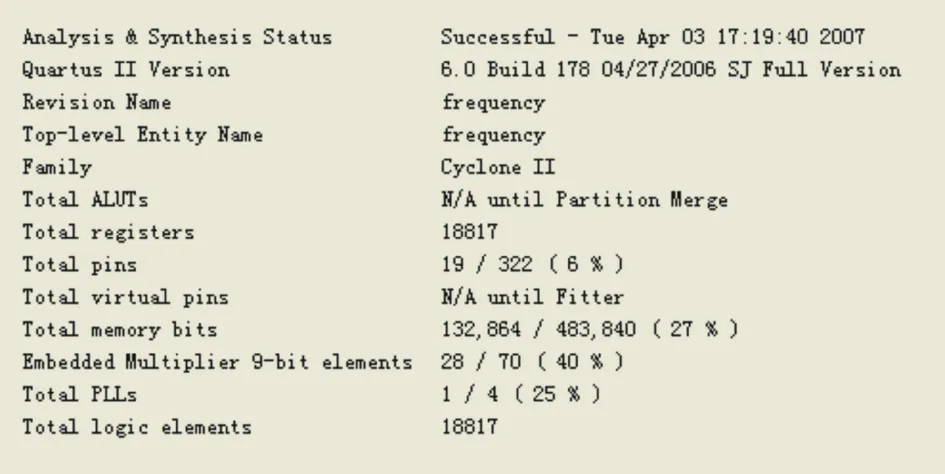

在NiosⅡ的開發流程中,我們首先使用SOPCBuilder系統綜合軟件來選取合適的CPU、存儲器以及外圍器件,并且定制相應的功能;然后使用QuartusⅡ軟件選取可編程器件,對生成的HDL設計文件進行布局布線,并對NiosⅡ系統上的I/O口分配管腳、編譯,綜合生成一個適合目標器件的網表作為配置文件;最后,使用編程器和下載電纜將配置文件下載到開發板上。FPGA工程的編譯報告如圖6所示。

圖6 FPGA工程的編譯報告Fig.6 The compile report of FPGA project

4 測頻電路的硬件實現

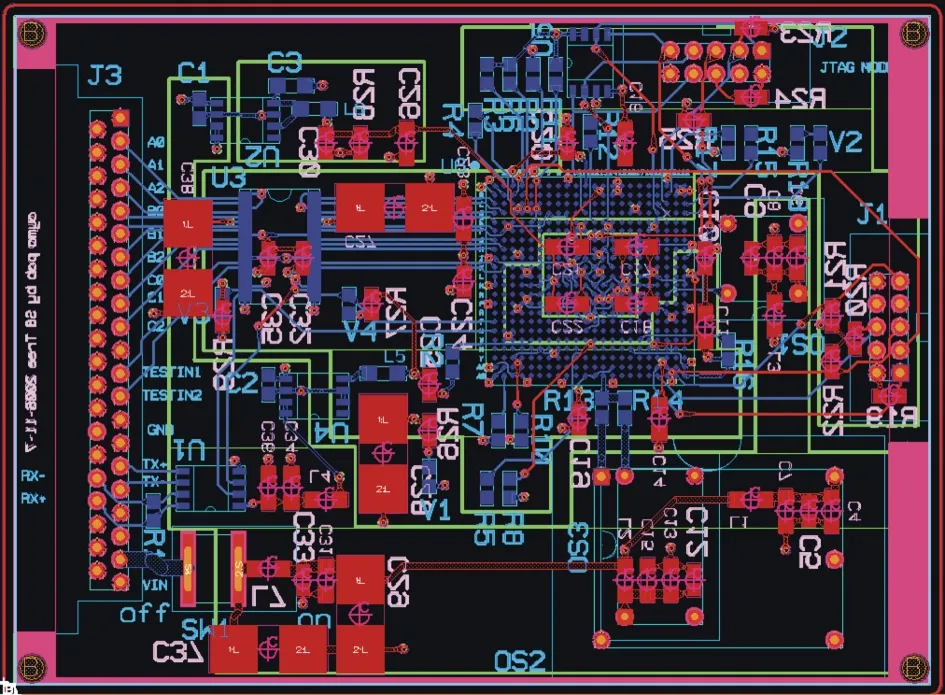

利用高端復雜電路設計軟件ExpeditionPCB設計的電路板,如圖7所示。同時采用信號完整性分析軟件對電路板圖進行了高速信號的串擾、EMC等分析,預先確保了電路板設計質量[4]。

圖7 高端復雜電路設計軟件Expedition PCB設計的電路板圖Fig.7 The circuit PCB scheme designed by advanced circuit design software Expedition PCB

樣機為一塊專用測頻電路板,按照功能可以分為:晶體振蕩器、輸入信號電平轉換器、閘門發生器、計數器、乘法器、除法器、數字信號處理軟核、通信接口以及電源管理系統[5]等模塊。

其中,晶體振蕩器作為標準頻率源和FPGA工作的全局時鐘;電平轉換器起到電平轉換和整形驅動的作用;鎖存器鎖存九路標頻和被測頻率的計數值;閘門發生器用于信號同步;乘法器/除法器用于數字運算;數字信號處理軟核進行數據處理、計數控制及通信處理,依據上位機的命令,將采樣結果通過通信串口傳輸給外部系統。電源管理系統給電路板分別提供5V、3.3V和1.2V三種電壓。

另外,設計不僅采用了新器件,而且大量地采用了新的軟件,包括FPGA設計軟件QuartusII系列(NiosⅡ、SignalTapII)、高端復雜電路設計軟件ExpeditionPCB系列(DxDesigner、ExpeditionPCB、I/ODesigner)、信號完整性分析軟件HyperLynx[6]。其他小軟件如串口調試助手、BorlandC++Builder等,這些先進的開發軟件都為電路設計提供了極大而有效率的幫助[7]。

5 試驗與分析

在試驗中,采用高精度的銣原子鐘WX-10標準頻率源做對比試驗。銣原子鐘準確度為5×10-9。將頻率標準的三路輸出信號隨機接入(并記錄)測頻電路的九路輸入端,分別進行0.1Hz、1Hz、10Hz采樣頻率的測試。在通電2s后開始采數。在0.1Hz、1Hz、10Hz采樣頻率下,現場至少測試15min,并提交調試階段測試的數據。測試完成后,用Excel繪制曲線圖,進行精度和穩定性分析。

在每個采樣頻率下,對每通道數據求均值,該均值與頻率真值的相對誤差作為該通道的測頻準確度。對每通道數據求標準偏差,標準偏差與測頻真值之比作為該通道的測頻穩定性。

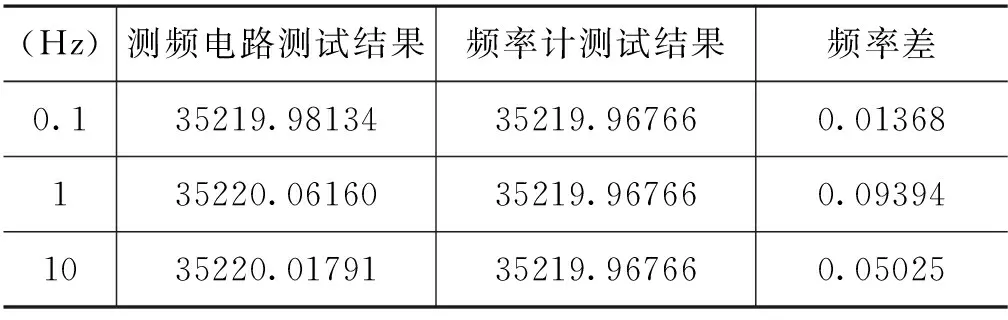

取第一通道的測試均值與安捷倫5312A頻率計測得的結果進行對比,如表1所示。

表1 加速度計測試結果對比Tab.1 The test results contrast of accelerometer

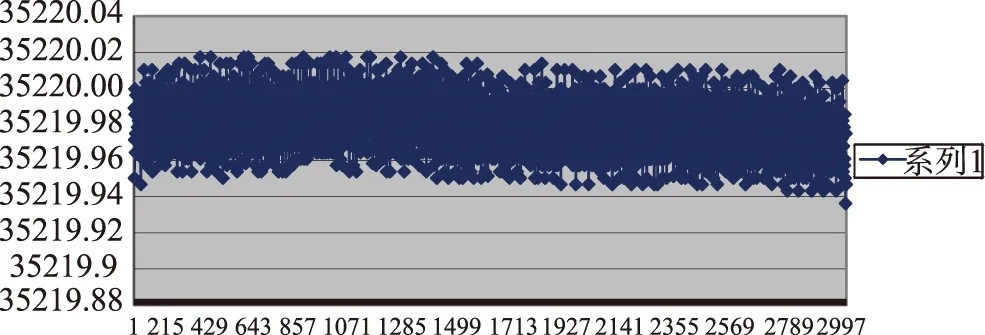

加表的第一通道輸出,10Hz采樣頻率下的測試曲線如圖8所示。

圖8 加表的第一通道輸出的測試曲線Fig.8 The test curve of the firstchannel output for accelerometer

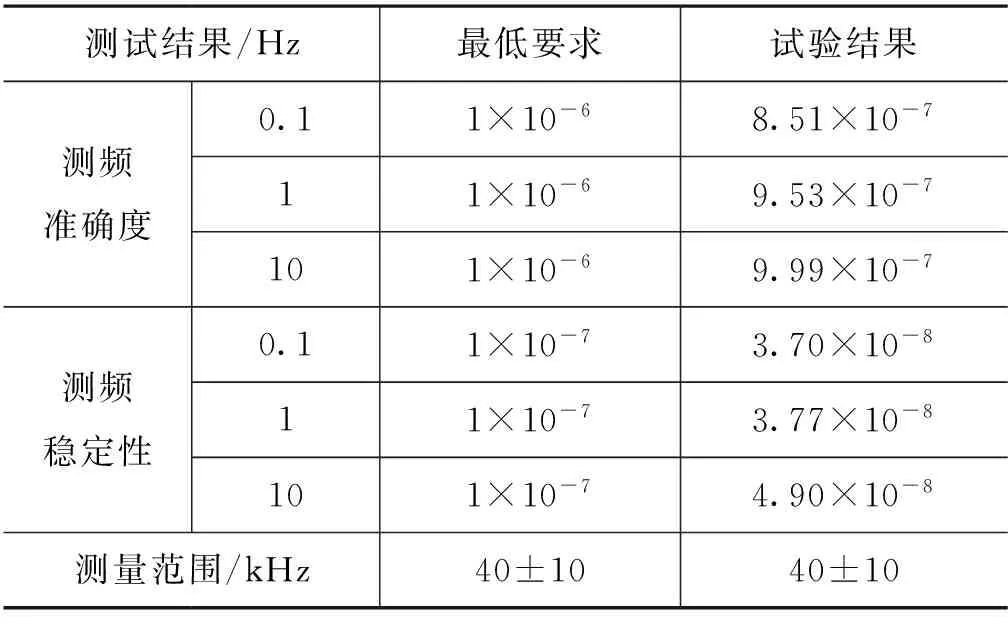

對測量精度進行了分析和計算,獲得以下對比的結果如表2所示。

表2 測試結果Tab.2 The test results

結果表明,該測頻電路實現了九路通道輸入,測頻范圍25~50kHz,輸出接口為RS422方式,測頻精度滿足指標要求,采樣頻率實現了輸出數據的速率有1次/10s、1次/s、10次/s三擋的要求。與振梁表聯調,在1Hz采樣時,不同通道的測試結果一致性好。

6 小結

通過研究與試驗,基于Nios Ⅱ嵌入式處理器的SOPC中精度測頻電路具有以下的特點:

(1)測頻電路系統的高度集成化

方案設計中,在一片FPGA內部集成了所有的邏輯模塊、運算模塊、控制模塊、UART軟核等,幾乎實現了信號采集、數據處理、通信協議等全部功能,最大限度地減少了外圍離散電路的使用,這也是未來嵌入式系統發展的趨勢。

(2)設計軟件的高端復雜化

使用高端復雜電路設計軟件進行BGA封裝設計,采用BGA球柵陣列的封裝形式芯片,進行電路板制板。另外,PCB廠家只能獲得Gerber文件和鉆孔文件,這樣也提高了設計文件的保密性。

(3)較高的頻率測量精度

設計并改進運算模塊,提高測頻精度,高速采樣下的連續、實時采樣,優化設計,盡量降低FPGA的資源利用率和功耗。實際測試時,被測信號為(40±10)kHz時,輸出數據的速率有1次/10s、1次/s、10次/s三擋(主要是受RS422/RS232轉換接頭的實時性和穩定性的影響)。該樣機在1Hz采樣頻率下靜態測試每一路的實際精度為:相對誤差小于9.99×10-7,穩定度小于4.90×10-8。

(4)FPGA的嵌入式軟核的應用

鑒于FPGA的飛速發展,在可編程邏輯器件中不僅采用硬件的IP核,以節約資源提高設計效率,而且采用了Nios Ⅱ軟核這款32位高性能處理器在FPGA內部進行配置,實現了可編程片上系統,提高了系統的可靠性。

基于Nios Ⅱ嵌入式處理器的SOPC中精度測頻電路的設計,采用以上關鍵技術將數據采樣和運算單元都集成在FPGA芯片中,形成一個片上操作系統SOPC,獲得了較高精度的測量結果。

[1] 章軍,張平,于剛.多周期同步測頻測量精度的提高[J].電測與儀表,2003,40(6):16-17.

[2] 李蘭英.Nios Ⅱ嵌入式軟核SOPC設計原理及應用[M].北京:北京航空航天大學出版社,2008.

[3] 周立功.SOPC嵌入式系統基礎教程[M].北京:北京航空航天大學出版社,2008.

[4] 張海風.HyperLynx仿真與PCB設計[M].北京:機械工業出版社,2006.

[5] 徐海軍,葉衛東.FPGA在高性能數據采集系統中的應用[J].計算機技術與應用,2005,25(1):40-43.

[6] 周潤景,景曉松.Mentor高速電路設計與仿真[M].北京:電子工業出版社,2008.

[7] 王誠,吳繼華,范麗珍,等.Altera FPGA/CPLD設計[M].北京:人民郵電出版社,2011.

SOPC Medium Precision Design for Frequency Measurement Circuit Based on Nios Ⅱ

DONG Jian-shu1,YUAN Xiao-yu1,WANG Hui2,YAN Zong-rui3

(1.Beijing Institute of Automatic Control Equipment,Beijing 100074,China;2.Beijing Revitalization Institute of Measurement and Test,Beijing 100074,China;3.Nanjing Naval Command Academy,Nanjing 210016,China)

The medium precision frequency measurement circuit is presented for the second measurement of quartz flap accelerator’s frequency output.Firstly,the scheme’s theoretical error is analyzed in detail by comparing and selecting proper measurements.Secondly,the frequency measurement circuit based on Nios Ⅱ embedded processor is discussed:both the data sampling and operation unit are integrated in FPGA chip,which forms SOPC,and a higher precision measurement result is achieved.

Frequency measurement;FPGA;Embedded processing;SOPC

2015 - 03 - 20;

2015 - 04 - 15。

董建樹(1979 - ),男,主要從事工業測控技術,信息化技術等方面的研究。

E-mail:treeplanter@163.com

TL822

A

2098-8110(2015)05-0070-06