定時同步中減小定時抖動的方法的研究與實現

Research and Implementation of the Method for Reducing Timing Jitter in Timing Synchronization

劉國建1,2 姚遠程1,2 秦明偉1,2

(西南科技大學信息工程學院1,四川 綿陽 621010;特殊環境機器人技術四川省重點實驗室2, 四川 綿陽 621010)

定時同步中減小定時抖動的方法的研究與實現

Research and Implementation of the Method for Reducing Timing Jitter in Timing Synchronization

劉國建1,2姚遠程1,2秦明偉1,2

(西南科技大學信息工程學院1,四川 綿陽621010;特殊環境機器人技術四川省重點實驗室2, 四川 綿陽621010)

摘要:在Gardner定時同步方法中,當達到同步時,小數插值間隔uspan應該是一個固定值;但由于高斯噪聲的影響,uspan會產生定時抖動,這會延長同步建立時間,進而提高誤碼率。基于此,提出了一種簡單可實現的減小定時抖動的方法。具體是在定時同步檢測前后分別增加預濾波器模塊和系數值為1的環路系數模塊。使用Simulink軟件搭建仿真模型并對上述改進進行仿真驗證,仿真結果表明,該方法能夠減小定時抖動,降低誤碼率。

關鍵詞:Gardner高斯噪聲定時抖動誤碼率預濾波器環路系數

Abstract:In the method of Gardner timing synchronization, when the system reaches synchronization, the fractional interpolation interval shall be a fixed value, however, because of the influence of Gaussian noise, uspanmay generate timing jitter, this will prolong the building period for synchronization and increase bit error rate. Thus the simple method for reducing timing jitter is proposed, that is: adding a pre-filtering module and a loop coefficient module with coefficient value 1, before and after the timing synchronization detection respectively. The simulation model is built by using Simulink software, and simulation verification for the improvement is conducted. The results of simulation show that this method can reduce timing jitter and bit error rate.

Keywords:GardnerGaussian noiseTiming jitterBit error ratePre-filterLoop coefficient

0引言

Gardner定時同步環路由內插濾波器、誤差檢測器、環路濾波器和數控振蕩器四部分組成[1-2],其中,環路濾波器能夠濾除誤差信號中的高頻成分和噪聲,減小定時抖動[3]。僅靠環路濾波器來減小定時抖動,則環路噪聲帶寬會減小,這會大大增加同步建立時間,并且會提高誤碼率[4]。

如何在不影響環路濾波器等效噪聲帶寬的情況下減小定時抖動,是本文研究的重點。定時環路輸入信號中疊加的高斯噪聲會引起定時抖動,為降低定時抖動,則應降低高斯噪聲影響。基于此,做出了兩個考慮:其一,在不改變環路其他參數的同時,在環路濾波器后增加環路系數模塊,從而降低噪聲系數;其二,在誤差檢測器前增加預濾波器模塊,在誤差檢測前濾除部分高斯噪聲。

1減小定時抖動方法

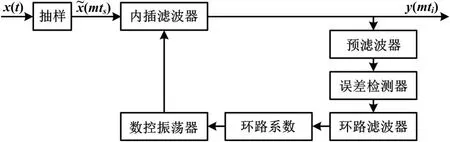

本文是在Gardner定時同步方法基礎上進行了兩點改進:一是在誤差檢測器前增加預濾波器模塊;二是在環路濾波器后增加環路系數模塊,其實現框圖如圖1所示。

圖1 Gardner定時同步改進方法實現框圖

1.1 預濾波器分析

在滾降系數為α的升余弦函數條件下,濾波器的幅頻響應如下[5-7]:

由前面分析可知:

g(mts+1/2ts)=0

(1)

在一些采樣時刻,g(t)不為零,則有:

(2)

式中:G(f)為g(t)的傅里葉變換,為帶寬限于[0,1/ts]的帶限信號。

(3)

那么,滿足上式的預濾波器的幅頻響應為:

(4)

上式表示的是理想情況下的濾波器幅頻特性函數。基于此,本文設計出一種實際應用的優化預濾波器,其幅頻特性函數與g(f)無限接近,表達式如下:

式中:m1、m2、m3為幅頻函數的權重系數;g′(f)為g(f)的幅度值。使用搜索算法得到使得Y(f)值最小,且Y(f)與g(f)最接近時的一組沖擊響應系數[8-9]。根據這些系數設計出所需要的預濾波器。

1.2 環路系數原理分析

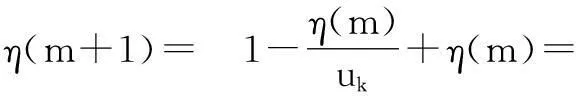

在Gardner定時恢復算法中,小數插值間隔uk由數控振蕩器計算所得[3]。設數控振蕩器頻率控制字為W(m),寄存器值為η(m),則小數插值點值為:

(5)

式中:ζ分量包括頻率控制字分量ζ0和噪聲分量N。

當環路達到同步時,有:

ζ=ζ0+N

(6)

將上式代入式(5)可得:

uk=(ζ0+N)η(m)=ζ0η(m)+Nη(m)

(7)

式中:ζ0η(m)為沒有噪聲的情況下uk的值;Nη(m)為噪聲分量。

因此,在保證ζ0η(m)不變的情況下,降低Nη(m)分量,就能達到降低噪聲影響、減小定時抖動的目的。由于環路確定后,η(m)就為固定值[4,10],因此只能通過減小N的值來減小定時抖動。

數控振蕩器中寄存器值η(m)與小數插值間隔uk的幾何關系如下:

(8)

式中:ts為采樣間隔。

綜合式(5)和式(8)可得:

(9)

上式為計算η(m)的迭代算法,根據迭代算法相關知識可推得下式:

(10)

將上式代入式(7)可得:

(11)

式中:ζ0=ti/ts,即重采樣時鐘和本地采樣時鐘的比值,為定值;η(0)為數控振蕩器初始值,也為定值。

因此,在沒有噪聲的情況下,達到同步時,uk為上式中的第一項ζ0η(0),是一固定的值;存在噪聲時,由于上式中N′的作用,使得uk的值在固定值上下波動。N′即為噪聲的幅度值,如果能在數控振蕩器前增加一個小于1的環路系數,則就能大大降低N′的值,從而降低uk的波動。試驗所得,環路系數取0.1~0.3時,達到定時同步需要的恢復點數較少(即同步建立時間較短),uk的波動也較小。但是,環路系數的選擇也不是越小越好,由于在定時恢復階段,環路濾波器輸出的誤差信號也與之相乘,將會影響數控振蕩器中mk的調整速度,影響整個定時恢復的速度,綜合考慮以上因素,本文中環路系數取0.1。

2仿真結果

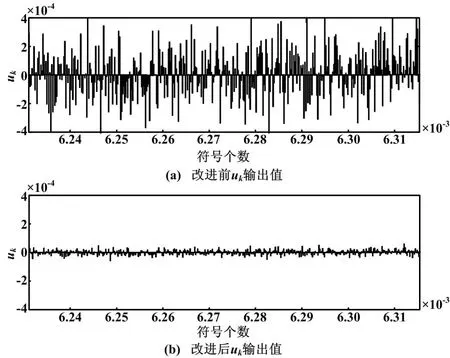

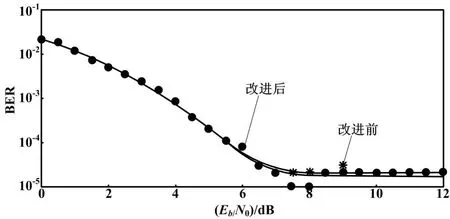

根據以上分析,在Gardner定時環路的仿真中添加了一個預濾波器模塊和系數值為0.1的環路系數模塊,比較了沒有添加環路系數模塊與濾波器模塊和添加系數值為0.1的環路系數及預濾波器模塊后mk的輸出波形的收斂情況。具體如圖2、圖3所示。

圖2 改進前后uk輸出值比較

圖3 改進前后誤碼率變化

3結束語

仿真結果表明,改進后,uk輸出幅度值的波動范圍降低了約87%,定時抖動明顯減小。同時,在信噪比大于6 dB時,改進后的誤碼率有明顯的降低,而且總體上,改進后的系統隨著信噪比的增加,誤碼率的降低速度更快。本文針對Gardner定時同步算法中存在定時抖動的問題,提出了一種在不影響環路濾波器等效噪聲帶寬的情況下能夠減小定時抖動的方法。利用Simulink工具對改進方法進行了仿真,結果表明,改進后定時抖動更小并且誤碼率更低。

參考文獻

[1] Gardner F M.A BPSK/QPSK timing detector for sampled receivers[J].IEEE Transactions on Communications,1986,34(9):423-429.

[2] Gardner F M.Interpolation in digital modems-part I:fundamentals[J].IEEE Transactions on Communications,1993,41(2):501-507.

[3] Lars E,Gardner F M.Interpolation in digital modems-part II:implementation and Performance[J].IEEE Transactions on Communications,1993,41(7):998-1008.

[4] 張錦鈺.高速數字解調中符號同步技術的研究[D].北京:中國科學院研究生院,2009.

[5] 孔明東,邱昆.用于減小定時抖動的數字預濾波器設計[J].電子科技大學學報,2002,31(6):557-561.

[6] 嚴剛峰,方紅,楊維,等.采用FPGA實現同步穿行數據的并行采集[J].自動化儀表,2014,35(9):84-86.

[7] 付永明,朱江,琚瑛玨.Gardner定時同步環路參數設計及性能分析[J].通信學報,2012(6):22-24.

[8] 朱輝.數字接收機并行定時同步的研究與實現[D].武漢:華中科技大學,2013.

[9] 劉磊.Matlab在“數字電路”課程教學中的應用[J].電氣電子教學學報,2008,30(5):9-11.

[10]張猛,王曉峰.Matlab環境下的數字電路仿真[J].長春大學學報,2005,15(2):22-25.

中圖分類號:TH29;TN919

文獻標志碼:A

DOI:10.16086/j.cnki.issn1000-0380.201507005

國防基礎科研計劃項目(編號:B3120133002);

西南科技大學研究生創新基金資助項目(編號:14ycxjj0117)。

修改稿收到日期:2014-01-10。

第一作者劉國建(1988-),男,現為西南科技大學信息與通信工程專業在讀碩士研究生;主要從事無線通信中同步技術的研究。