一種分布式納秒級精度時頻同步系統(tǒng)設計

包 健,王小青

(總參謀部第六十研究所 江蘇 南京 210016)

在大量的時頻設備中存在同步的要求,特別是一些分布式設備對時基同步有著更高的要求,如GPS系統(tǒng)對每顆在軌衛(wèi)星的同步;某些科研試驗及測量測試過程中同樣需要同步,如在頻率測量時為了消除測量誤差我們會對信號源和頻率計進行同步。同步的方法和方式各有不同,可以通過無線介質(zhì)傳輸同步信號,也可以通過有線介質(zhì)傳輸同步信號;可以通過主站分發(fā)同步信號,也可以在分布設備中分別使用更高穩(wěn)定度的時基。文中設計的是一種基于有線介質(zhì)的主從站[1]分布式高精度同步系統(tǒng)。

1 系統(tǒng)概述

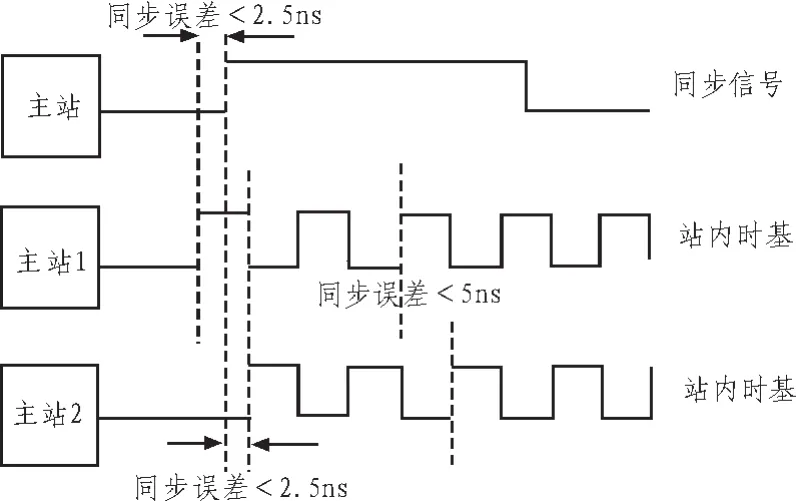

該系統(tǒng)采取了一種主從站分布式射頻發(fā)射的方案實現(xiàn)高精度的同步,這種方式的自主性和穩(wěn)定性相對較高,不像GPS授時同步方式會受GPS衛(wèi)星限制和無線鏈路相位脈沖模糊特性的影響。系統(tǒng)中各從站發(fā)射信號的上升沿相位差控制在5 ns以內(nèi),發(fā)射設備采用5MHz的信號作為從站時基。同步誤差控制原理如圖1所示。

圖1 誤差控制精度示意圖Fig.1 diagram of the error control accuracy

從站間5 ns的同步精度的實現(xiàn)需要從站同主站間的同步誤差必須控制在2.5 ns內(nèi),為了達到這一要求,主站穩(wěn)定度最低要求為2.5×10-9/s。同時考慮所采取的數(shù)字測頻技術對時間的要求,大約每10 s進行一次主從站間的頻率同步和上升沿相位誤差測量。這樣穩(wěn)定度就要提高一個數(shù)量等級,即-10次方量級[2]。

2 系統(tǒng)硬件設計

2.1 主從站同步方式與時基選擇

主站通過有線屏蔽介質(zhì)分發(fā)同步信號到各個從站的同步方式,這種方式可以有效避免無線通信方式中可能存在的強電磁干擾。

主站選擇短期穩(wěn)定度、飄移等指標控制在1×10-11/s量級的銣原子鐘[3]作為時基信號;從站選擇短穩(wěn)指標每10 s漂移[4]小于2.5 ns的高穩(wěn)晶體振蕩器[5]作為同步前的時基信號。這種主站采用高精度時基,從站采用低精度時基的方式,可以有效地降低整個系統(tǒng)的成本。

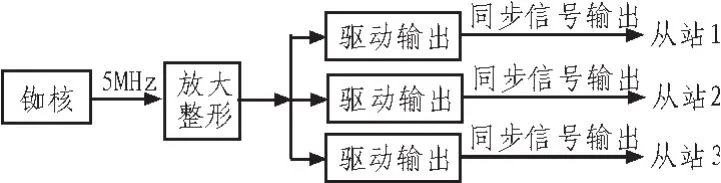

2.2 主站工作原理

主站的功能是生成同步信號。主站的銣原子鐘輸出信號經(jīng)過放大整形、增加驅(qū)動能力后作為同步信號輸出到各個從站,其工作原理框圖如圖2所示。

圖2 主站工作原理結構圖Fig.2 Structure diagram of themaster station’swork principle

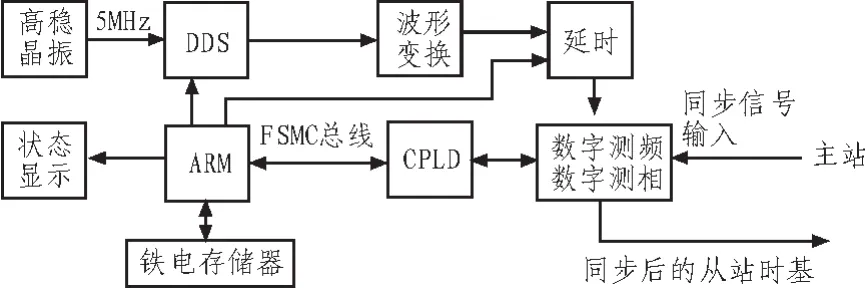

2.3 從站工作原理

從站接收主站的同步信號,并將從站的高穩(wěn)晶體振蕩器輸出信號作為DDS芯片的參考信號。CPU采用ST公司的STM32F407芯片ARM處理器,利用FSMC總線從CPLD周期性的讀取相頻差計數(shù)數(shù)據(jù)并計算,然后通過改變相位增量的方式修改DDS輸出信號的頻率,實現(xiàn)和主站的頻率同步,并通過控制延時元件進行相位調(diào)節(jié),其實現(xiàn)原理框圖如圖3所示。

圖3 從站工作原理結構圖Fig.3 Structure diagram of the slave station’swork principle

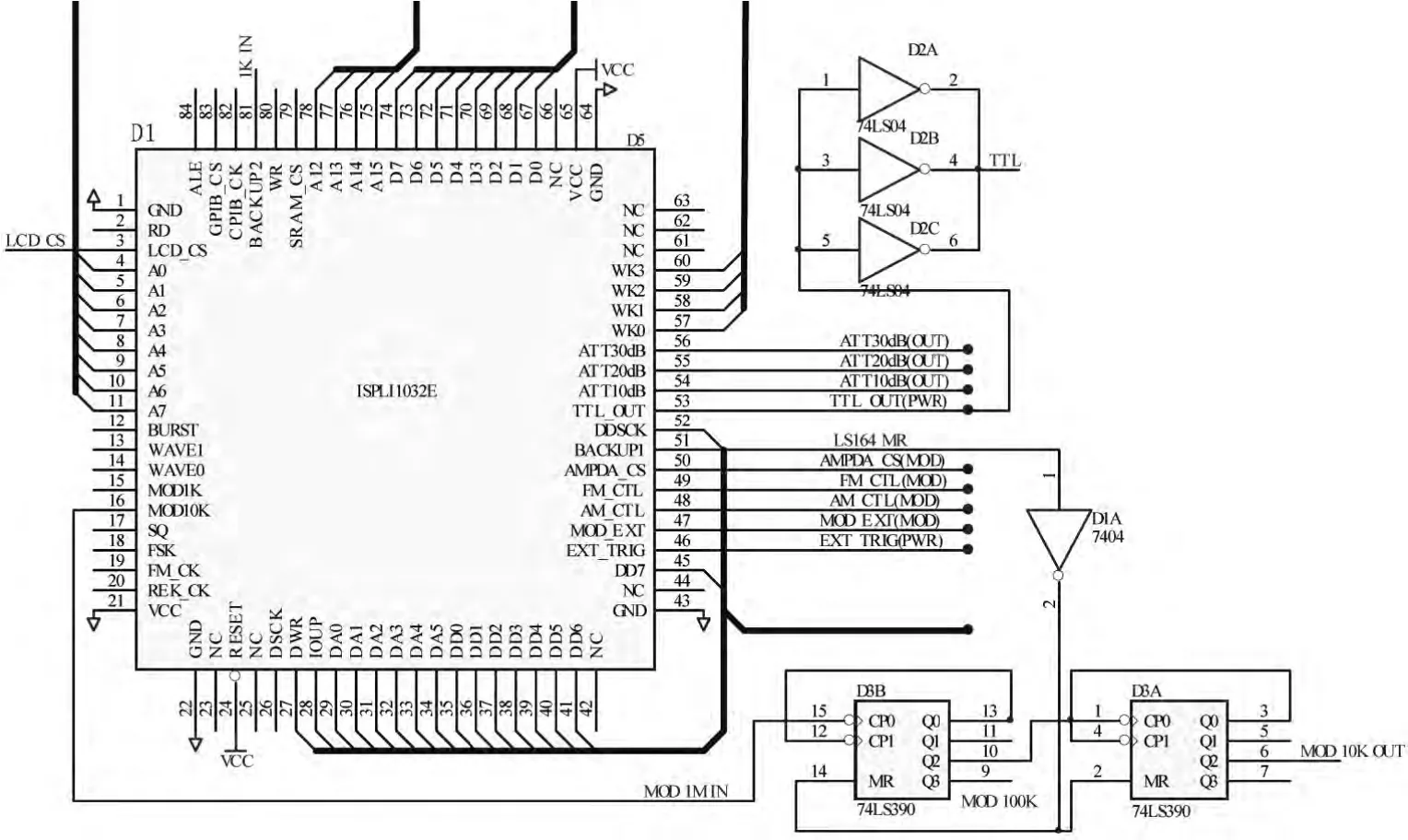

CPLD采用Lattice公司的ispli1032E芯片實現(xiàn),用于測量同步信號和本從站信號之間的頻差和相差;此芯片共有84腳,具體芯片腳定義如圖4所示。

圖4 CPLD引腳定義圖Fig.4 diagram of CPLD pin definitions

2.3.1 模擬內(nèi)插法等精度頻率測量實現(xiàn)

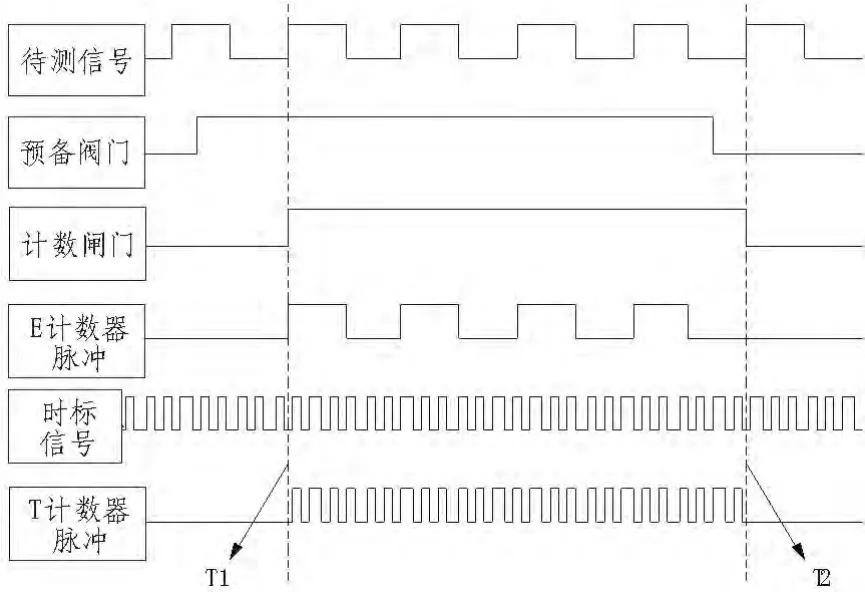

該系統(tǒng)設計中的關鍵點在于是否能將主從站之間的頻率誤差測量和調(diào)節(jié)的范圍控制在100μHz以內(nèi)。系統(tǒng)中使用的等精度頻率測量時序原理如圖5所示。

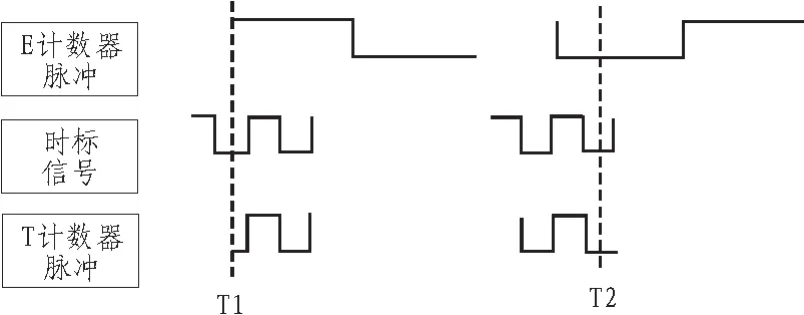

等精度測量方法通過計數(shù)閘門[7]的設計實現(xiàn)了時基(T)計數(shù)器同步于事件(E)計數(shù)器,保證了測量精度。但傳統(tǒng)的等精度測量誤差引入的一個途徑就在圖5的T1和T2處。我們發(fā)現(xiàn)T計數(shù)器并沒有完全同步于事件,從而產(chǎn)生了不完整的計數(shù)脈沖,局部放大后如圖6所示。

圖5 等精度測量的時序Fig.5 Sequence in time of the same accuracy frequencymeasurement

圖6 測量誤差引入點Fig.6 Entry points of themesurement error

在引入內(nèi)插法前提高等精度頻率測量的精度一般有兩個途徑:1)提高計數(shù)時鐘頻率;2)延長閘門時間。以100 MHz時鐘,1s閘門為例,理論測量精度只有1×10-8。模擬內(nèi)插法的引入就是為了對T1和T2誤差時間進行測量,在T計數(shù)器的時間中去除,從而提高測量精度。這種方法的原理是對誤差時間進行放大,然后對放大后的誤差計數(shù),完成計數(shù)后再縮小相應的倍數(shù),從而計算出誤差時間。

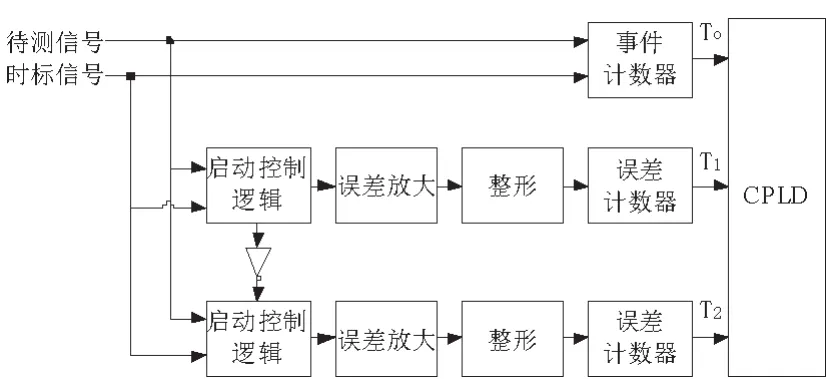

系統(tǒng)中采用電容充放電方法實現(xiàn)模擬內(nèi)插。CPLD計數(shù)模塊采用計數(shù)法測得時間間隔T0,并對展寬1 000倍并整形后的擴展信號時間間隔的T1和T2脈沖進行采樣計數(shù),再由CPU對計數(shù)進行計算,就可以得到實際信號的時間間隔,如式(1)所示。

模擬內(nèi)插電路實現(xiàn)原理框圖如圖7所示。

圖7 模擬內(nèi)插實現(xiàn)原理圖Fig.7 diagram of the simulate interpolationmethod

將輸入同步信號經(jīng)整形處理后作為圖5中的閘門控制信號,用來測量主站同步信號和從站時基信號的上升沿誤差,然后通過延時元件進行調(diào)整,從而提高測量精度。在引入內(nèi)插模塊后能在同等時鐘和閘門條件下提高3個數(shù)量級別的測量精度。

2.3.2 DDS調(diào)頻電路實現(xiàn)

隨著器件技術的發(fā)展,DDS[8]的相位累加器位數(shù)已經(jīng)很高,相位累加器的位數(shù)越高合成信號的頻率分辨率越高。在本系統(tǒng)中我們選擇一款48位相位累加器的AD9852芯片,可以提供1μHz的頻率分辨率。當我們測量出主站同步信號和從站時基信號的頻率差后,通過修改DDS的輸出信號頻率來消除主站和從站之間的頻差。在本系統(tǒng)中我們可以把主站和從站間的頻率誤差縮小到100μHz以內(nèi)。

DDS的正弦波輸出信號需經(jīng)過內(nèi)部的超高速比較器轉換成數(shù)字方波信號才能供CPLD芯片測量。本系統(tǒng)中方波是以正弦波為源,接入AD9852內(nèi)部比較器的負端(VINN),而正端(VINP)參考電壓為零電位,這樣就可輸出標準的方波,其關鍵原理圖如圖8所示。

3 軟件設計

在頻率測量的過程中需要不斷進行動態(tài)修正,這是由于:1)頻率測量不可能零誤差,主從站之間的信號還是存在一個微小的頻差;2)同時無論是銣原子鐘還是高穩(wěn)晶體振蕩器都存在頻率漂移現(xiàn)象。因此從站軟件運行過程中也需要不斷的測量修正頻差,調(diào)節(jié)信號的相位差,才能實現(xiàn)長期同步。從站軟件循環(huán)工作流程為初始化→預設閘門1S→脈沖計數(shù)→取數(shù)計算→相頻設置→鐵電存儲→送顯→脈沖計數(shù)……。

圖8 DDS調(diào)頻原理圖Fig.8 diagram of the DDS frequencymodulation

同步運行期間,若主站同步信號丟失,從站則調(diào)用正常同步周期內(nèi)測得的相頻差參數(shù)進行動態(tài)修正;若主站同步信號丟失且從站死機重啟,從站初始化時將讀入重啟前保存于鐵電內(nèi)的相頻差參數(shù)進行動態(tài)修正。這使得系統(tǒng)能在同步中斷的一定時間內(nèi)還能保持在系統(tǒng)要求的同步誤差范圍內(nèi)。

4 結論

這種主從站工作方式的分布式時頻同步系統(tǒng)能有效避免強電磁干擾,從站成本低,不受GPS衛(wèi)星限制和無線鏈路相位脈沖模糊的影響,從站間同步精度在5ns以內(nèi),是一種有效的高精度時頻同步的方法,達到了設計要求,具備良好的工程應用價值。

[1]謝春勝.系統(tǒng)間實時同步問題的研究 [J].電子對抗技術,2002,17(6):32-33.

[2]Barnes JA.Characterization of frequency stability[J].IEEE transaction on instrumentation and measurement,1971,20(2):146-160.

[3]李孝輝,吳海濤,高海軍,等.用Kalman濾波器對原子鐘進行控制[J].控制理論與應用,2003,20(4):551-552.

[4]王志田.頻率穩(wěn)定度測量系統(tǒng)的參考頻率源[J].宇航計測技術,1987(5):25-31.

[5]Sullivan D B,Allan DW,Howe D A,etal,ed.Chara cteriza-t ion of Clocksand Oscillator[M].NISTTechnology Note,1990.

[6]黃盛霖,沈聰輝,趙曉娟,等.利用最佳分頻實現(xiàn)高精度頻率測量[J].兵工自動化,2011,30(9):68-69.

[7]陳芳紅,張志文.基于NiosII改進的多周期同步頻率測量系統(tǒng)設計[J].儀表技術與傳感器,2014(12):56-58.

[8]劉昱,史玉玲,柳瑩,等.基于AD9851的正弦信號發(fā)生器設計[J].電子設計工程,2009,17(7):14-16.