淺議頻率合成器在現(xiàn)代無(wú)線通信收發(fā)機(jī)中的實(shí)現(xiàn)形式

胡習(xí)霜 玄甲輝

【摘要】 隨著科技的不斷進(jìn)步,無(wú)線通信技術(shù)在人類生活中的作用越來(lái)越大。本文對(duì)現(xiàn)代無(wú)線通信收發(fā)機(jī)中的關(guān)鍵部件之一——頻率合成器的實(shí)現(xiàn)形式做了一般性的討論。首先簡(jiǎn)要介紹了下無(wú)線通信系統(tǒng)中的重要組成部分——射頻收發(fā)機(jī),對(duì)頻率合成器在無(wú)線通信收發(fā)機(jī)中的作用做了簡(jiǎn)單說(shuō)明。然后詳細(xì)介紹了頻率合成器的幾種實(shí)現(xiàn)方法,并分別展開(kāi)描述具體實(shí)現(xiàn)形式。文章最后對(duì)頻率合成器的實(shí)現(xiàn)形式做了總結(jié),并指出在目前的無(wú)線通信領(lǐng)域中應(yīng)用最為廣泛的是鎖相環(huán)式頻率合成器體系結(jié)構(gòu)。

【關(guān)鍵字】 無(wú)線通信 頻率合成器 射頻收發(fā)機(jī) 實(shí)現(xiàn)形式

一、無(wú)線通信系統(tǒng)的射頻收發(fā)終端概述

無(wú)線通信系統(tǒng)是用于發(fā)送從信源發(fā)出的信息或消息到一個(gè)或多個(gè)目的地的系統(tǒng),信源產(chǎn)生的信息可以包括多種形式,比如圖像、語(yǔ)音、數(shù)據(jù)信號(hào)等。典型的無(wú)線通信系統(tǒng)包括信源信宿、輸入輸出換能器、發(fā)射機(jī)和接收機(jī)。

通常,接收機(jī)和發(fā)射機(jī)可以被集成設(shè)計(jì)為無(wú)線收發(fā)機(jī)。集成之后,接收單元和發(fā)射單元可以復(fù)用部分模塊,可進(jìn)一步減小芯片面積。隨著市場(chǎng)需求的不斷提高,對(duì)收發(fā)機(jī)的指標(biāo)要求也越來(lái)越高,在保持高性能的基本要求之下,還要求無(wú)線收發(fā)機(jī)具有低成本、低尺寸、低功耗等特點(diǎn)。

二、頻率合成器在無(wú)線通信收發(fā)機(jī)中的作用

在無(wú)線通信領(lǐng)域中,頻率合成器起著越來(lái)越重要的角色。在無(wú)線收發(fā)機(jī)結(jié)構(gòu)中,頻率合成器作為混頻器中本振的產(chǎn)生源,是不可或缺的一部分。頻率合成器是將一個(gè)高穩(wěn)定度和高精確度的標(biāo)準(zhǔn)參考頻率(一般是晶體振蕩器),經(jīng)過(guò)倍頻或分頻等操作對(duì)它進(jìn)行四則運(yùn)算,最終產(chǎn)生一個(gè)或多個(gè)具有同樣精確度和穩(wěn)定度的頻率源的電路模塊或設(shè)備[1],它是影響電子系統(tǒng)穩(wěn)定性和精確性的最關(guān)鍵因素之一。

在現(xiàn)代無(wú)線通信收發(fā)機(jī)中,頻率合成器獲得的頻率精確度和穩(wěn)定度的好壞,將直接決定整個(gè)射頻收發(fā)機(jī)系統(tǒng)性能的好壞。

三、頻率合成器的實(shí)現(xiàn)形式

有關(guān)頻率合成器的研究,最早提出是在20世紀(jì)30年代,在近代電子技術(shù)發(fā)展的過(guò)程中,頻率合成器體系得到不斷發(fā)展,結(jié)構(gòu)得到不斷擴(kuò)充。

從這項(xiàng)技術(shù)提出以來(lái),先后經(jīng)歷了直接模擬式頻率合成器、直接數(shù)字式頻率合成器和間接鎖相式頻率合成器等三個(gè)階段的發(fā)展。

隨著各種現(xiàn)代產(chǎn)品中電子系統(tǒng)地位的與日俱升,在應(yīng)用以及市場(chǎng)的牽引下,頻率合成器技術(shù)得到不斷快速發(fā)展,如高指標(biāo)、小體積的合式頻率合成器[2]以及將鎖相和DDS相結(jié)合的混合式頻率合成器。

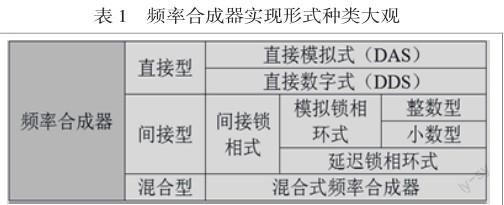

如表 1所示,頻率合成器大致上可分為三大類:直 接型、間接性和混合型。

3.1直接模擬式頻率合成器

直接模擬式頻率合成器是最早出現(xiàn)的一種頻率合成類型,它的工作原理很簡(jiǎn)單,就是用諧波發(fā)生器、混頻器、倍頻器、分頻器和帶通濾波器電路對(duì)一個(gè)或幾個(gè)基準(zhǔn)頻率進(jìn)行四則運(yùn)算,從而產(chǎn)生所需求的頻率信號(hào)。根據(jù)合成方式不同可分為相關(guān)合成與非相干合成兩種[3]。

直接頻率合成器可以實(shí)現(xiàn)快速頻率變換、低相位噪聲、幾乎任意高的頻率分辨率以及很高的頻率輸出。但是直接頻率合成要使用很多的硬設(shè)備,因而具有體積大、造價(jià)高的特點(diǎn)。除此,它還有另一個(gè)缺點(diǎn):在輸出端會(huì)出現(xiàn)大量無(wú)用的寄生頻率——雜波。

在大部分應(yīng)用場(chǎng)合,直接頻率合成方法已被采用鎖相技術(shù)的間接頻率合成方法所取代[1]。

3.2直接數(shù)字式頻率合成器

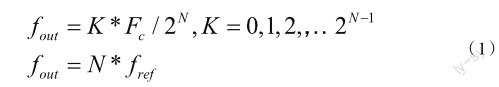

直接數(shù)字式頻率合成技術(shù)是1971年由美國(guó)學(xué)者J.T、C.M.R和B.G首次提出的,采用全數(shù)字化方式實(shí)現(xiàn)。一個(gè)典型的DDS系統(tǒng)主要由相位累加器、正弦波查找表、D/A轉(zhuǎn)換器和低通濾波器組成。DDS的輸出頻率為:

其中,K為頻率控制字,N為相位累加器的比特位長(zhǎng)度,F(xiàn)C為時(shí)鐘頻率。由于受奈奎斯特定律的約束,最高輸出頻率不能高過(guò)系統(tǒng)時(shí)鐘的一半,一般取時(shí)鐘的40%作為上限,其頻率分辨率為FC / 2N。

DDS是一個(gè)完全數(shù)字化的系統(tǒng),具有易于集成、頻率合成速度快、極快的跳頻速度、頻率切換時(shí)相位連續(xù)和極高的頻率分辨率等優(yōu)點(diǎn),缺點(diǎn)是雜散比較大、輸出頻率低、功耗較大。

3.3間接鎖相式頻率合成器

鎖相式頻率合成技術(shù)又稱為間接式頻率合成技術(shù),是基于PLL的一種頻率合成技術(shù)。廣義的講,鎖相環(huán)電路使一個(gè)特殊系統(tǒng)跟蹤另一個(gè)系統(tǒng)。在同步狀態(tài),振蕩器輸出信號(hào)和參考信號(hào)之間的相位差為0,或者保持常數(shù)[4]。鎖相環(huán)是一種相位誤差控制系統(tǒng),它通過(guò)比較輸入信號(hào)和壓控振蕩器輸出(或分頻器后的輸出)信號(hào)之間的相位差,從而產(chǎn)生一個(gè)反饋電壓來(lái)控制VCO的輸出頻率,以達(dá)到與輸入信號(hào)成倍頻關(guān)系的目的。

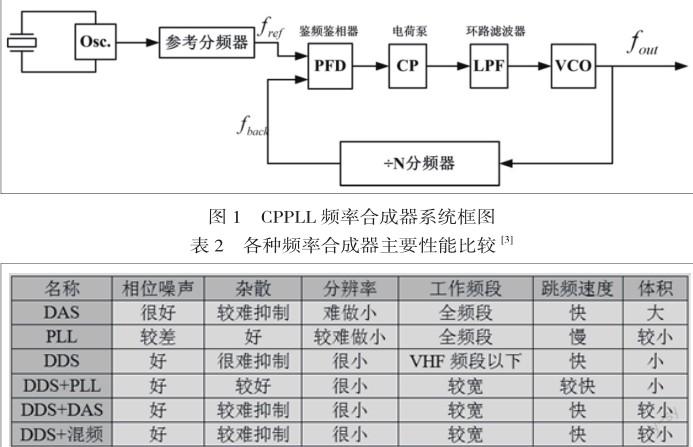

在現(xiàn)代通信用收發(fā)終端機(jī)中,基于PLL的頻率合成器廣泛采用電荷泵鎖相環(huán)(CPPLL)式頻率合成器。CPP LL頻率合成器的一般系統(tǒng)框圖如圖 1所示。

電荷泵鎖相環(huán)式頻率合成器由鑒頻鑒相器、電荷泵、壓控振蕩器以及÷N分頻器組成。頻率合成器的輸出頻率為:

其中N為分頻器分頻比(可為整數(shù)或小數(shù)),fref為PFD的輸入?yún)⒖碱l率。

3.4混合型頻率合成器

混合式頻率合成技術(shù)是近幾年非常流行的頻率合成技術(shù),主要形式有DDS激勵(lì)PLL、DDS內(nèi)插PLL、DDS+倍頻、DDS+混頻等幾種合成方式[3]。

這種方案利用了DDS的高分辨率來(lái)提高PLL輸出的頻率分辨率,又能得到較高的頻率輸出,同時(shí)PLL內(nèi)的環(huán)路濾波器對(duì)帶外的DDS雜散也能夠起到很好的抑制作用。但是該種混合型頻率合成器的頻率轉(zhuǎn)換時(shí)間取決于PLL。

四、頻率合成器不同實(shí)現(xiàn)形式總結(jié)

本文中大致介紹了目前所存在的幾種不同形式的頻率合成技術(shù),其中,無(wú)線通信領(lǐng)域中應(yīng)用最為廣泛的是鎖相環(huán)式頻率合成器體系結(jié)構(gòu)。

這種結(jié)構(gòu)的最大優(yōu)點(diǎn)是容易在CMOS工藝上集成。在性能可滿足大多數(shù)無(wú)線通信系統(tǒng)指標(biāo)要求的前提下,可大大節(jié)省功耗。基于ADPLL的頻率合成器一般用于數(shù)字電路,能夠糾正時(shí)鐘,實(shí)現(xiàn)很低的時(shí)鐘傾斜,缺點(diǎn)是不能夠編程。

在需要本振頻率很高的情況下,一般可采用直接模擬頻率合成器結(jié)構(gòu),缺點(diǎn)是功耗和體積比較大,而且成本會(huì) 比較高。綜上,可對(duì)各種頻合成器主要性能比較如表 2所示。

參 考 文 獻(xiàn)

[1]李智群. 射頻集成電路與系統(tǒng)[M]. 北京:科學(xué)出版社. 2008.8.

[2]Longiun Zhai,Yonghua Jiang,Xiang Ling,et a1.DDS-Driven PLL Frequency synthesizer for X-band Radar signal simulation[C]. IEEE Conference on Systems and control in aerospace and astronautics.IEEE,2006:344-346.

[3]楊檍,鮑景富. 現(xiàn)代頻率合成技術(shù)的研究進(jìn)展. 電訊技術(shù) Telecommunication Engineering. 2007, 47(2).

[4]Roland E.Best 著 李永明 [等] 譯. 鎖相環(huán)設(shè)計(jì)、仿真與應(yīng)用. 北京:清華大學(xué)出版社,2007.4