基于FPGA的曼徹斯特編解碼研究及IP核設(shè)計(jì)

章潔

(成都信息工程學(xué)院,四川成都 610225)

基于FPGA的曼徹斯特編解碼研究及IP核設(shè)計(jì)

章潔

(成都信息工程學(xué)院,四川成都 610225)

曼徹斯特碼在通信中有廣泛的應(yīng)用,其編解碼器的設(shè)計(jì)是影響整個(gè)總線系統(tǒng)的關(guān)鍵因素,但是曼徹斯特碼的時(shí)序很復(fù)雜。本文采用FPGA技術(shù),深入研究曼徹斯特編解碼原理,完成了曼徹斯特編解碼的IP核設(shè)計(jì),經(jīng)過(guò)仿真驗(yàn)證了設(shè)計(jì)方法的正確性和工程應(yīng)用性。

曼徹斯特編碼 FPGA 解碼器

1 引言

曼徹斯特碼是一種雙向碼或分相碼,是常用二元碼的一種,曼徹斯特編碼是一種自動(dòng)同步的編碼方式,常用于通信中對(duì)串行數(shù)據(jù)進(jìn)行編碼,其特點(diǎn)是利用碼元中2種不同的電平跳變來(lái)對(duì)傳輸數(shù)據(jù)進(jìn)行編碼的,此外編碼后每對(duì)碼元都存在著電平跳變,這種特性和時(shí)鐘信號(hào)的特性相同,可以在曼徹斯特碼中提取出時(shí)鐘信號(hào);曼徹斯特碼的每對(duì)碼元都含有跳變,編碼不會(huì)出現(xiàn)3個(gè)或者3個(gè)以上的“1”或者“0”,所以采用曼徹斯特碼進(jìn)行通信,可以確保數(shù)據(jù)在傳輸過(guò)程中沒(méi)有直流成分,而且編碼中暗含有時(shí)鐘信號(hào),數(shù)據(jù)的接收端能提取出數(shù)據(jù)發(fā)送端的時(shí)鐘,因此,采用曼徹斯特碼可以實(shí)現(xiàn)數(shù)據(jù)在接收和發(fā)送的同步。曼徹斯特碼以其高穩(wěn)定性和同步性而被廣泛的應(yīng)用于通信中,且更適合用于傳輸條件較差的環(huán)境中進(jìn)行信息傳輸。

本文對(duì)曼徹斯特碼的原理進(jìn)行深入研究,選用VHDL或Verilog語(yǔ)言,編寫曼徹斯特碼的功能模塊,將各模塊組成一個(gè)通用的IP核,并用EDA設(shè)計(jì)工具進(jìn)行仿真、綜合和驗(yàn)證。不同于其他曼徹斯特編碼器設(shè)計(jì),本文設(shè)計(jì)中引入了儲(chǔ)存器模塊,最后把各模塊組成一個(gè)通用的IP核。

2 編解碼模塊設(shè)計(jì)

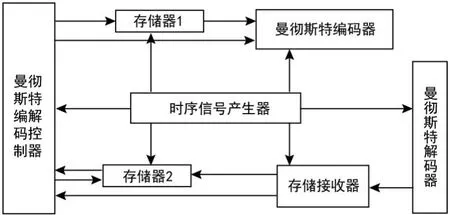

曼徹斯特編解碼系統(tǒng)設(shè)計(jì)要完成的任務(wù)是實(shí)現(xiàn)數(shù)據(jù)的編碼發(fā)送,同時(shí)還能解碼接收,并進(jìn)行整個(gè)通信過(guò)程的驗(yàn)證,因此,必須有一個(gè)模塊化的整體設(shè)計(jì)。曼徹斯特編解碼IP內(nèi)核包括6個(gè)模塊,即時(shí)序信號(hào)產(chǎn)生模塊、存儲(chǔ)器模塊、曼徹斯特編解碼控制模塊、曼徹斯特編碼模塊、曼徹斯特解碼模塊、存儲(chǔ)器接收模塊,系統(tǒng)的結(jié)構(gòu)框圖如圖1所示。

圖1 曼徹斯特編解碼系統(tǒng)結(jié)構(gòu)圖

其中時(shí)序信號(hào)產(chǎn)生器主要是為整個(gè)系統(tǒng)提供所需的各種時(shí)鐘信號(hào)和復(fù)位信號(hào);曼徹斯特編解碼控制器是系統(tǒng)的核心,為系統(tǒng)提供輸入數(shù)據(jù)和各個(gè)部分的控制信號(hào);編碼器是對(duì)傳輸?shù)臄?shù)據(jù)進(jìn)行編碼輸出;解碼器是對(duì)接收到的曼徹斯特碼進(jìn)行解碼和串并轉(zhuǎn)換;存儲(chǔ)接收器為接收的數(shù)據(jù)分配相應(yīng)的存儲(chǔ)空間;存儲(chǔ)器是在FPGA中開(kāi)辟專門的存儲(chǔ)空間對(duì)數(shù)據(jù)進(jìn)行暫時(shí)的存儲(chǔ)。

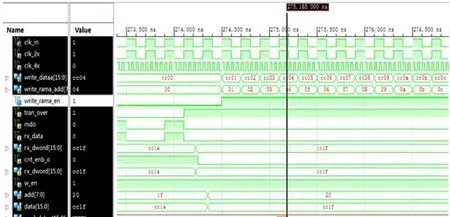

圖3 數(shù)據(jù)編碼和解碼的波形仿真

如圖4所示,當(dāng)存儲(chǔ)接收器開(kāi)始向存儲(chǔ)器2發(fā)送數(shù)據(jù)后,會(huì)通w_en反饋給控制器,控制器開(kāi)始接收數(shù)據(jù),控制器通過(guò)信號(hào)read_rama_en控制存儲(chǔ)器2發(fā)送數(shù)據(jù),存儲(chǔ)器2根據(jù)控制器發(fā)送的地址信號(hào),把對(duì)應(yīng)存儲(chǔ)空間的數(shù)據(jù)發(fā)送給控制器。

3 FPGA實(shí)現(xiàn)及測(cè)試

圖4 控制器接收數(shù)據(jù)的波形仿真

至此系統(tǒng)的整個(gè)工作過(guò)程驗(yàn)證完畢,仿真中沒(méi)有出現(xiàn)任何掉幀的問(wèn)題,仿真和理論設(shè)計(jì)相符合。

本文對(duì)曼徹斯特碼的數(shù)據(jù)通信過(guò)程進(jìn)行驗(yàn)證。設(shè)計(jì)主要是完成數(shù)據(jù)從編碼—發(fā)送—接收—解碼的整個(gè)通信過(guò)程的驗(yàn)證,整個(gè)系統(tǒng)的驗(yàn)證如圖2所示。

4 結(jié)束語(yǔ)

本文設(shè)計(jì)了基于FPGA的曼徹斯特編解碼IP核,以通信功能為主,完成了系統(tǒng)各個(gè)模塊的設(shè)計(jì),并對(duì)各個(gè)模塊進(jìn)行了仿真和驗(yàn)證。從中可以看出曼徹斯特碼的穩(wěn)定性是很高的,作為IP軟核,具有可兼容性及可擴(kuò)展性,從仿真結(jié)果看,該曼徹斯特編解碼IP核能完全達(dá)到光纖通信的要求,有一定的工程意義。

系統(tǒng)的工作開(kāi)始是從控制器向存儲(chǔ)器1發(fā)送數(shù)據(jù)開(kāi)始的,存儲(chǔ)器1起到一個(gè)對(duì)數(shù)據(jù)暫時(shí)存儲(chǔ)的作用,控制器向存儲(chǔ)器1發(fā)送數(shù)據(jù)的同時(shí)也向編碼器發(fā)出控制信號(hào),命令編碼器開(kāi)始工作。

圖3是系統(tǒng)編碼發(fā)送和解碼輸出的仿真,圖中mdo是數(shù)據(jù)的曼徹斯特碼傳輸,在控制器發(fā)送數(shù)據(jù)給存儲(chǔ)器1時(shí),也控制編碼器工作,編碼器一幀一幀的接收數(shù)據(jù)并對(duì)數(shù)據(jù)編碼輸出,當(dāng)解碼檢測(cè)到編碼中的同步字后,解碼器開(kāi)始對(duì)編碼進(jìn)行解碼輸出,rx_dword是解碼器解碼并進(jìn)行串并轉(zhuǎn)換后輸出給存儲(chǔ)器接收器的數(shù)據(jù),存儲(chǔ)器接收模塊接收數(shù)據(jù)后,按照規(guī)定為數(shù)據(jù)分配相應(yīng)的地址信息,并把地址信號(hào)和數(shù)據(jù)發(fā)送給存儲(chǔ)器2。

[1]劉福奇.FPGA嵌入式項(xiàng)目開(kāi)發(fā)實(shí)戰(zhàn)[M].北京:電子工業(yè)出版社,2009.

[2]張劍,郭莉.基于Xilinx ISE的FPGA/CPLD設(shè)計(jì)與應(yīng)用[M].北京:電子工業(yè)出版社,2009.

[3]何建新,高勝.數(shù)字邏輯設(shè)計(jì)基礎(chǔ)[M].北京:高等教育出版社, 2012.

[4]何道君,譚明.FPGA的設(shè)計(jì)與應(yīng)用[M].北京:清華大學(xué)出版社,2006.

[5]張偉.基于FPGA的通信接口模塊設(shè)計(jì)與實(shí)現(xiàn)[J].電子科技, 2012,25(7):95-98.

Research on Manchester Encoding and Decoding Based on FPGA and Design on Its IP Core

ZHANG Jie

(Chengdu University of Information Technology,Chengdu Sichuan 610225,China)

Manchester code is used widely in field of communication.The design on codec is a key factor which affects the whole bus-system,and the time sequence of Manchester code is very complex.In this paper,the principle of Manchester code is studied in depth by using the FPGA technology,and the IP core design is completed for Manchester coding and decoding.The simulation results show that this design method is correct and has some engineering application value.

Manchester coding;FPGA;decoder

F224-39

A

1008-1739(2015)12-67-2

定稿日期:2015-05-26

四川省教育廳2013年自然科學(xué)基金課題(13ZB0082)