基于FPGA的信號燈沖突檢測電路的設計與實現

楊福來,孫旭飛,李 碩

(福州大學 物理與信息工程學院,福建 福州 350108)

基于FPGA的信號燈沖突檢測電路的設計與實現

楊福來,孫旭飛,李 碩

(福州大學 物理與信息工程學院,福建 福州 350108)

采用軟件控制方式的道路交通信號機在死機時往往失去其綠沖突保護功能。根據“綠沖突矩陣”的檢測原理,本文提出一種道路交通信號控制機的信號沖突檢測方案,采用自頂向下的設計方法,通過FPGA實現系統的各個功能模塊。該系統可以獨立地檢測綠燈信號沖突這種道路交通的異常情況,并能立即做出處理。仿真及實際測試結果表明,該系統時序分配與程序設計合理,工作穩定可靠,并能夠提高信號機嵌入式系統的實時性。

綠沖突;FPGA;綠沖突矩陣;校驗

0 引言

隨著各國城市化進程的不斷發展,智能交通系統在城市道路交通控制中得到了廣泛的應用。智能道路交通信號機是智能交通系統的重要組成部分,也是解決城市交通問題的關鍵設備。信號機中的綠沖突檢測可以提高智能交通系統的安全性和可靠性。由于過去的綠沖突保護控制方式相對簡單,通常是用簡單的繼電器互鎖或者信號燈的接線實現[1],隨著多相位、多時段控制方式和線控、面控方式的發展,目前的綠沖突檢測多通過信號機的控制軟件實現。然而,當這類信號機出現死機導致信號沖突時,其保護功能就失效。因此研究一種新的綠沖突檢測電路在智能交通控制中具有十分重要的現實意義。

本文研究的綠沖突檢測電路采用FPGA實現。FPGA適合于組合邏輯和時序邏輯電路設計,并且具有并發執行的功能,相對于微控制器的程序設計更加穩定可靠[2]。同時,基于FPGA的綠沖突檢測電路實現信號機的綠沖突檢測功能,可以減輕信號機 CPU的負擔,提高系統的實時性。

1 綠沖突

綠沖突是指規定不允許同時放行的信號燈組中的綠色信號燈同時點亮[3]。就目前的交通信號控制機來說,產生綠沖突的原因大概有以下幾類:

(1)系統軟故障

此類綠沖突通常是由于交通信號機里面的控制系統出現死機或者是一些數據處理錯誤等軟故障造成的。不僅如此,如果交通信號機在較為惡劣的電磁環境下工作,也會受到電磁干擾而出現短暫的綠沖突現象。

(2)硬件故障

由于信號機的硬件變質、損壞或者溫度變化、受潮等原因造成的綠沖突。這種情況如果發生,就可能長時間持續下去,只能對信號機進行維修或者更換里面的部件[4-5]。

2 基于綠沖突矩陣的校驗原理

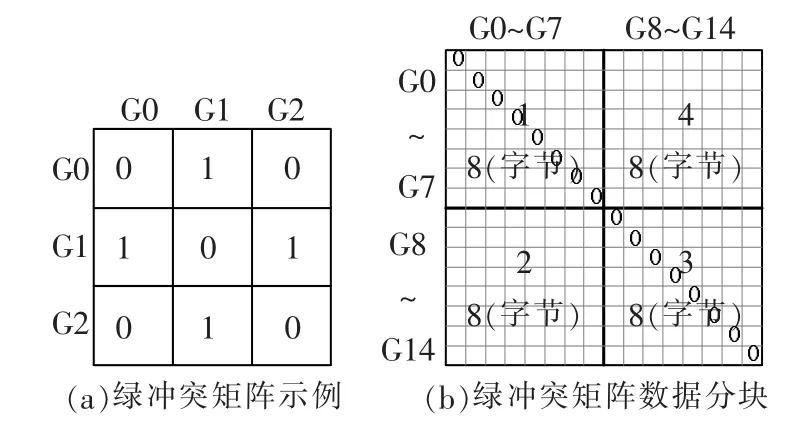

本文設計的綠沖突檢測是基于綠沖突矩陣的檢測原理,沖突矩陣的行和列分別對應一個信號燈組,為一對稱矩陣,如圖1所示。

在圖1(a)中假設有 G0、G1、G2三個綠燈信號,設G0和G1同時點亮視為沖突,G1和G2同時點亮視為沖突,則圖中對應沖突的位置填入 1,G0和 G2同時點亮不視為沖突的位置填 0,如圖所示,本文稱之為綠沖突矩陣數據,因此,綠沖突矩陣數據中的位信息 1就是某綠燈對子不允許同時點亮的定義。校驗過程如下:

當輸入的信號為G0G1G2=010時 (1表示綠燈亮,0表示綠燈滅):

(1)G0為 0,不與 G0所在的行校驗,轉下一行;

(2)G1為 1,進行校驗,將輸入信號“010”與 G1所在的行“101”相與,即 010&101=0,數據正確;

(3)G2為 0,同理不需要校驗。

當G0G1G2=110,即G0和G1同時亮時,與G0所在行相與后結果非 0,說明G0和 G1信號沖突,此時,信號機應立即切斷所有綠燈信號,轉而執行黃閃信號。

本文設計的綠沖突檢測電路對應 15路綠燈信號G0~G14,如東西方向的直行綠燈、左轉綠燈、右轉綠燈、掉頭綠燈、行人綠燈等。在本文中綠沖突矩陣數據是以字節為單位的,所以 15路信號對應的綠沖突矩陣數據分成 4塊,每一塊有 8字節,按照圖1(b)的編號順序通過FPGA串口寫進FPGA的ROM中。其中第一塊數據用于校驗 G0~G7綠信號之間的沖突,第二塊數據用于校驗G8~G14與G0~G7綠信號之間的沖突,第三塊數據用于校驗G8~G14綠信號之間的沖突。第四塊數據也是用于校驗G8~G14與G0~G7綠信號之間的沖突,因此不需要寫進 ROM。在校驗的過程中還應排除 Gx與 Gx自身的比對,如圖1(b)中斜方向所示。

圖1 綠沖突矩陣數據分布圖

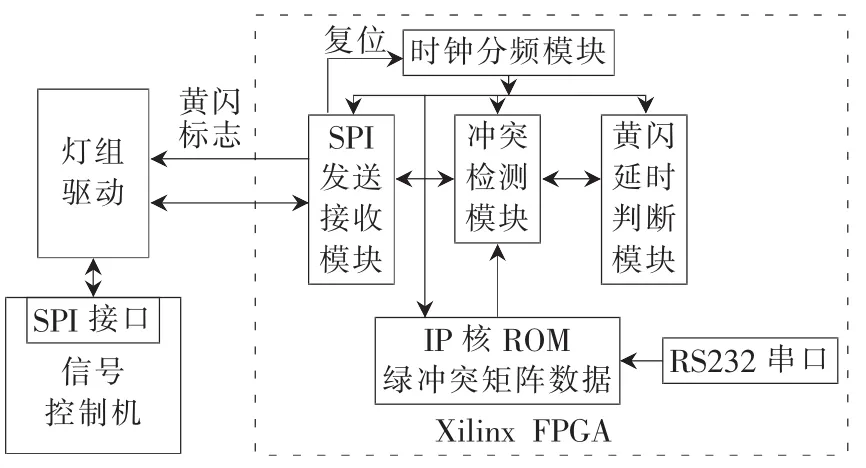

3 總體方案

根據綠沖突矩陣的檢測原理,采用自頂向下的設計方法將檢測電路分為以下幾個模塊:(1)信號燈的燈組驅動電路,通過SPI方式在正常狀態下接收信號控制機的燈組數據,在黃閃狀態下接收沖突檢測電路發送的信號燈黃閃數據。(2)沖突檢測電路采用 Xilinx的 FPGA芯片 XC3S50,通過 SPI模塊接收信號燈的狀態數據。(3)數據接收結束后復位時鐘分頻模塊,時鐘分頻模塊產生其他模塊所需時鐘,所有模塊都是在統一的時鐘線上運行,以免發生時序混亂。(4)沖突檢測模塊,在檢測時序期間對 SPI接收的數據即信號燈的狀態數據進行綠沖突校驗,校驗是根據上文所說的綠沖突矩陣比對各綠燈信號狀態,該綠沖突矩陣數據存放在FPGA的IP核所生成的ROM里面。(5)黃閃延時判斷模塊,沖突檢測模塊的檢測結果經過黃閃延時判斷模塊進行延時檢測并確認是否有沖突。如果沒有沖突,則燈組驅動繼續接收信號控制機的燈組數據;如果有沖突,則黃閃標志置位,切斷MCU的SPI通道,沖突檢測電路通過 SPI開始發送黃閃數據至燈組驅動,從而讓燈組驅動切換至黃閃狀態。總體方案如圖2所示。

圖2 總體方案

4 各模塊設計

4.1 SPI模塊

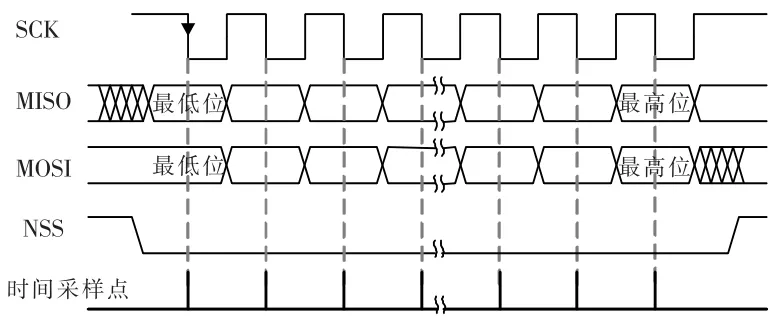

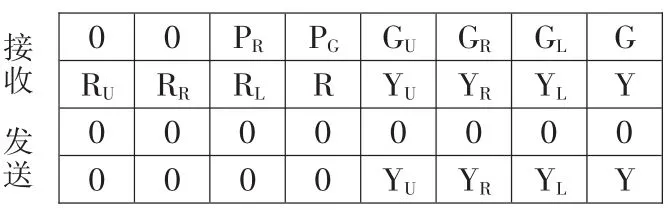

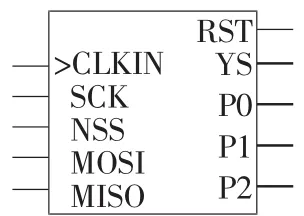

SPI協議(Serial Peripheral Interface),即串行外圍設備接口,是一種高速全雙工的通信總線。SPI總線包含 4條總線,分別為 NSS、SCK、MOSI、MISO,FPGA SPI時序如圖3所示。從圖中可以看出,FPGA在時鐘的下降沿采集燈組的數據,在上升沿發送數據。數據的傳輸是從低位開始,接收的燈組信號存到三組 16位寄存器 P0、P1、P2。P0、P1、P2的數據格式一樣,如圖4所示,分別表示不同的道路方向。G是綠燈信號,Y是黃燈信號,R是紅燈信號,下標表示不同的形式,如左轉、右轉等。另有一組4位的寄存器YS用于存放黃閃數據,當處于黃閃狀態時,YS寄存器的值以時鐘分頻模塊控制的時鐘頻率進行 0/1交替改變,并通過 SPI發送至燈組驅動,從而控制燈組驅動進入黃閃狀態,SPI模塊如圖5所示。

4.2 時鐘分頻模塊

圖3 FPGA SPI時序圖

圖4 SPI發送和接收的數據格式

圖5 SPI模塊

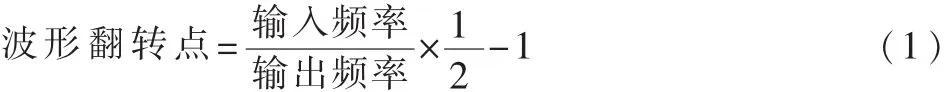

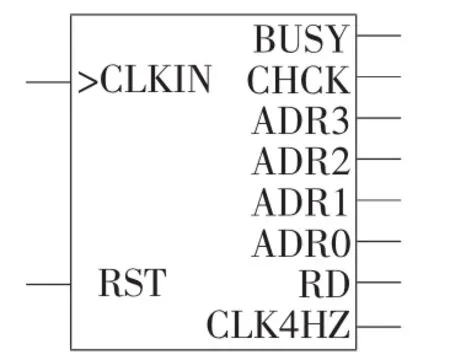

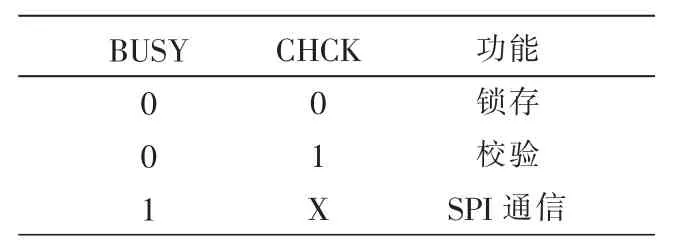

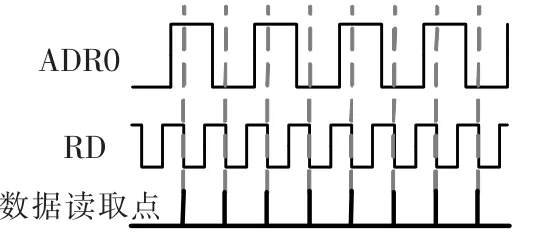

時鐘分頻模塊相當于整個電路的驅動模塊,所有沖突檢測模塊都是在時鐘分頻模塊提供的時鐘下工作。如圖6所示,輸入的系統時鐘 CLKIN被分頻為 BUSY、CHCK、ADR3、ADR2、ADR1、ADR0,頻率為62.5 Hz~2 kHz。分頻器是通過計數器實現的,計數的方式如式(1)所示[6],當計數到波形翻轉時間點時將波形輸出取反。BUSY和CHCK的功能如表1所示,當BUSY為 1時,沖突檢測電路通過 SPI開始接收燈組狀態數據,如果處于黃閃狀態,則同時發送黃閃數據。ADR3~ADR0是ROM校驗表的地址,可以尋址16個16位綠沖突矩陣數據。CLK4HZ是黃燈閃爍的頻率,RD信號是ROM的讀數據信號,頻率是4 kHz。由于RD讀信號和ADR地址信號不能同時跳變,否則數據將會不穩定,從而讀不到正確的數據,因此需要將RD信號與ADR0的地址錯開,如圖7所示,程序設計是通過16 kHz時鐘分頻得到4 kHz,但是在復位時計數器從1開始計數,最后將4 kHz取反后輸出到RD信號。

圖6 時鐘分頻模塊

表1 BUSY和CHCK功能表

圖7 RD時序圖

4.3 沖突檢測模塊

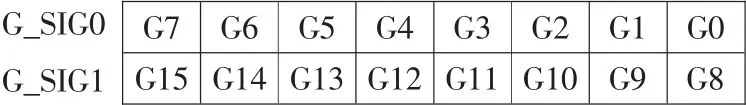

綠沖突檢測模塊是本文設計的核心模塊,其檢測周期定為 4 ms。在檢測周期開始時,先將 P0、P1、P2三燈組中的15路綠燈信號讀入8位寄存器G_SIG0、G_SIG1,其位置排列如圖8所示。綠沖突檢測就是尋找綠沖突矩陣數據中定義的同時點亮的綠燈對子,如果找到一個或一個以上的對子就判定發生了綠沖突。因此,尋找過程就是一個循環處理過程。首先判斷G_SIG0或G_SIG1中的 i位是否為 1(i為 0~14),如果 i為 1,說明 i位的綠燈亮;其次,把 G_SIG0或 G_SIG1中的 i位值清零。i位清零后,如果 G_SIG0或 G_SIG1中的值不為零,說明有與 Gi成對的綠燈對子存在。把這個數值與綠沖突矩陣數據中Gi對應的數據相與,若結果不為零,說明有與 Gi成對但不允許同時點亮的綠燈對子存在,即存在綠沖突,循環處理結束,準備輸出黃閃。如果結果為零,i加1,進行下一輪比對處理。

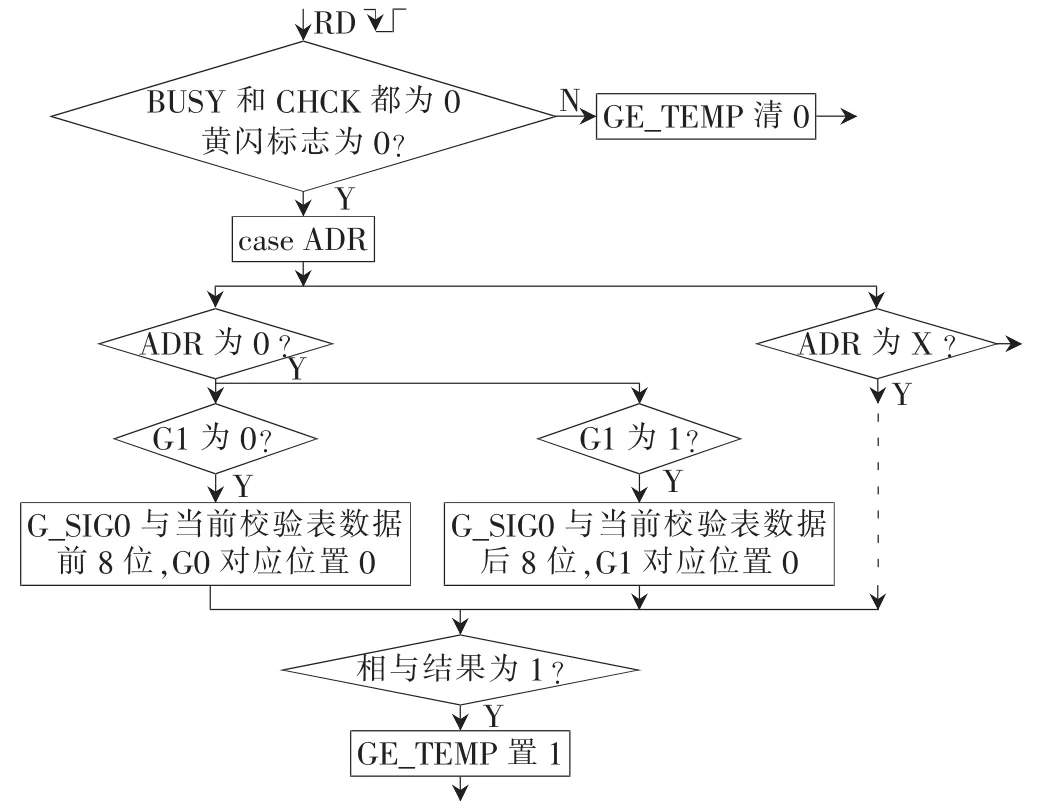

按照沖突矩陣的數據格式,需將 G0~G15分別與第2節中描述的綠沖突矩陣數據的三塊數據進行校驗,FPGA程序設計如圖9所示。在每次讀信號到來時,FPGA讀入2字節數據,隨后地址信號ADR加1計數,地址 ADR 0~3的區域為第一塊數據,4~7的區域為第二塊數據,8~11的區域為第三塊數據。 在滿足時序(BUSY為 0,CHCK為 1)與不黃閃的條件下,讀入的第一塊數據用于綠燈狀態 G0~G7與自身的比對,第二塊數據用于綠燈狀態G0~G7與綠燈狀態G8~G14的比對,第三塊數據用于綠燈狀態G8~G14與自身的比對。如果比對處理結果判定為綠沖突,則將綠沖突臨時標志置1,否則將臨時標志清 0。

圖8 綠燈信號狀態圖

圖9 綠沖突檢測流程圖

4.4 黃閃延時判斷模塊

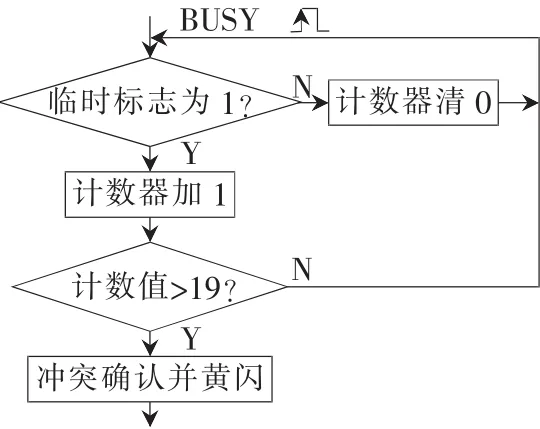

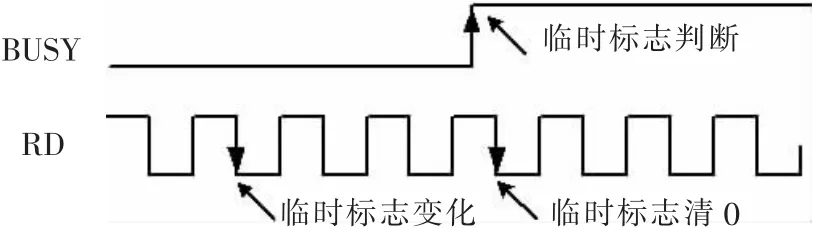

當信號燈閃爍時,每隔 250 ms就要改變一次狀態,即0和 1的交替變化,這樣沖突臨時標志必然也會變化, 從而導致錯誤判斷。 因此需要加入延時判斷,在BUSY上跳變的時候對臨時標志進行判斷,若是1則計數器累積加1,否則清 0計數器。當累計到 19時(BUSY周期 16 ms,即計數時間超過 300 ms),才可確認為沖突信號,觸發黃閃信號,程序如圖10所示。

延時判斷必須在臨時標志被清 0之前,從圖11的時序圖中可以看出,臨時標志位變化是在 BUSY上升沿之前,清 0在 BUSY上升沿之后,因此延時判斷的觸發信號為BUSY的上升沿。

圖10 黃閃延時判斷流程圖

圖11 黃閃延時判斷時序圖

4.5 其他模塊

實際上,信號沖突檢測電路還包括紅綠沖突檢測、紅燈滅與綠燈滅檢測電路,這些電路在邏輯上相對簡單,本文不做描述。另外,利用 Xilinx FPGA的 IP核生成的ROM模塊以及RS232串口模塊在本文所列出的相關參考文獻中有詳細的介紹,這里也不再描述[7-8]。

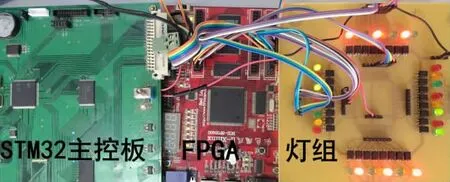

5 仿真與測試

通過 Xilinx的 ISE開發軟件編寫Test Fixture測試文件對各個模塊進行仿真測試,查看各個模塊的波形時序正確后,對頂層模塊進行整體仿真。仿真結果表明,本設計時序邏輯正確,當 2個燈組的綠燈狀態違反綠沖突矩陣數據定義時能正確檢測出沖突,進而進入黃閃。最后利用 STM32主控板和 FPGA開發板以及自己焊接的LED信號燈電路對程序進行實際驗證測試,如圖12所示。測試表明,信號燈在沒有沖突的時候能正常運行,沖突時則進入黃閃狀態。

圖12 硬件測試圖

6 結論

本文詳細介紹了基于FPGA的綠沖突檢測電路各個模塊的原理與設計,經過嚴密的時序分析以及 Verilog語言編程,實現了各個模塊的基本功能,并通過了功能仿真與實際的硬件測試。結果表明該系統可以正確檢測出各種綠信號沖突并立即做出處理,使得智能交通系統更加安全可靠。利用FPGA設計的功能模塊經過編譯后生成實際的時序邏輯電路,更加穩定可靠,而且后期還可以進行功能更改與完善,方便維護。

[1]尹征琦,朱勁,劉智勇.綠沖突的智能保護及其實現[J].公路交通科技,1998,15(3):26-29.

[2]梁赫西,謝虎城,王建,等.基于 FPGA的智能車牌定位識別系統設計[J].電子技術應用,2014,40(11):32-35.

[3]高雨,葉煒,沈國江.多相位智能交通控制器的設計[J].江南大學學報(自然科學版),2006,5(5):556-560.

[4]史忠科,黃輝先.交通控制系統導論[M].北京:科學出版社,2003.

[5]王錕,張衛華,衛立陽.基于綠間隔矩陣的信號配時計算方法研究及應用[J].交通科技,2014(2):132-134.

[6]王水魚,馮曉靖.一種新型 delta-sigma小數分頻器的FPGA實現[J].微型機與應用,2013,32(5):25-27,31.

[7]徐文波,田耕.Xilinx FPGA開發實用教程(第二版)[M].北京:清華大學出版社,2012.

[8]劉東華.Xilinx系列 FPGA芯片 IP核詳解[M].北京:電子工業出版社,2013.

Design and implementation of signal conflict detection circuit based on FPGA

Yang Fulai,Sun Xufei,Li Shuo

(College of Physics and Information Engineering,Fuzhou University,Fuzhou 350108,China)

Road traffic signal controller with software control tends to lose its green conflict protection when it crashes.This paper presents a traffic signal conflict detection scheme of traffic signal controller according to the principles of green conflict matrix. Finally the system′s various functional modules were achieved in top-down design approach using FPGA.This system can independently detect green signal conflict,and handles it immediately.Simulation and practical test results show that the system runs stably and reliably and its timing assignments and program design are reasonable,which also improves the real-time performance of embedded systems.

green conflict;FPGA;green conflict matrix;check

TP277

A

1674-7720(2015)23-0023-04

楊福來,孫旭飛,李碩.基于 FPGA的信號燈沖突檢測電路的設計與實現[J].微型機與應用,2015,34(23):23-26.

2015-08-09)

楊福來(1990-),通信作者,男,在讀碩士研究生,主要研究方向:智能交通、嵌入式系統。E-mail:fulaiyang@163.com。

孫旭飛(1961-),男,碩士,副教授,主要研究方向:嵌入式系統、智能交通技術、電力線擴頻載波技術。

李碩(1990-),男,在讀碩士研究生,主要研究方向:嵌入式系統與應用。