DDS工作原理的教學探究

徐太龍,王洪海,黃 慧,李 瑤,倪敏生,徐 雷,胡學友(.合肥學院電子信息與電氣工程系,安徽合肥3060;.安徽三聯學院 電子電氣工程學院,安徽 合肥3060;3.亳州師范高等專科學校理化系,安徽 亳州36800)

DDS工作原理的教學探究

徐太龍1,王洪海2,黃慧1,李瑤1,倪敏生1,徐雷3*,胡學友1

(1.合肥學院電子信息與電氣工程系,安徽合肥230601;2.安徽三聯學院 電子電氣工程學院,安徽 合肥230601;3.亳州師范高等專科學校理化系,安徽 亳州236800)

摘要:基于直接數字合成技術的信號產生電路的設計和實現是《片上可編程系統技術課程》的重要教學內容.針對許多教材中關于直接數字合成技術工作原理講解不清晰造成學生理解困難的問題,采用圖形法、相位圓法和公式推導法由淺入深、循序漸進地闡述了直接數字合成技術的工作原理,以幫助學生更好地掌握該知識點,培養學生運用理論知識分析和設計復雜電子電路系統的能力,取得了良好的教學效果.

關鍵詞:直接數字合成技術;現場可編程門陣列;片上可編程系統

隨著微電子技術和計算機技術的發展,可編程邏輯器件(Programmab1e Logic Device,PLD)、電子設計自動化技術(E1ectronic Design Automation,EDA)、嵌入式系統、系統芯片(System on ChiP,SoC)、可編程片上系統(System on a Programmab1e ChiP,SoPC)和知識產權(Inte11ectua1 ProPerty,IP)核等新概念和新技術層出不窮,新技術的應用有力地提高了社會信息化程度[1].嵌入式領域的迅速發展,使得現場可編程門陣列(Fie1d Programmab1e Gate Array,FPGA)作為主芯片的嵌入式應用方向成為高校教學和研究的熱點[1].基于FPGA的電子系統技術是21世紀電子應用工程師必備的基本技能之一,而基于FPGA 的SoPC設計技術是當前電子系統設計領域最前沿的技術之一[2].因此,眾多高校電子信息和電氣類專業開設了《SoPC技術》課程.

基于直接數字合成技術(Direct Digita1 Synthesis,DDS)的信號產生電路的設計與實現是《SoPC技術》課程的重要內容[3-7].較多教材中偏重于DDS的FPGA實現步驟和方法,對DDS原理的講解不夠清晰和透徹,造成學生按照實驗講義做完實驗后仍不能自行設計和實現更復雜的信號發生電路,詳細闡述了DDS的工作原理對培養學生將理論用于實踐和根據基本理論進行創新的能力具有重要意義.

1 DDS的相關概念

1971年,Tierney J、Rader C M和Go1d B等人在期刊 《IEEE Transaction on Audio and E1ectroacoustics》上發表的論文《A digita1 frequency synthesizer》中首次提出DDS的概念.但是,受制于當時電子電路技術的水平,沒有引起人們足夠的重視.直到21世紀,隨著微電子技術的快速發展和數字集成電路工藝水平的成熟,使DDS的理論和實現技術成為研究熱點[8-10].

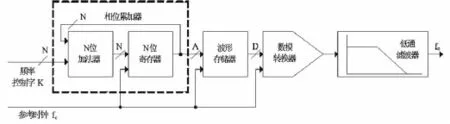

DDS技術具有頻率精度高、高相位分辨率、頻率切換速度快、相位噪聲低和結構簡單且易于集成的優點[11].其基本結構框圖見圖1,由參考時鐘、相位累加器、波形存儲器、數模轉換器(Digita1 to Ana1og Converter,DAC)和低通濾波器(Low Pass Fi1ter,LPF)組成.其中為參考時鐘頻率、Tc為參考時鐘周期、K為頻率控制字、N為相位累加器位數、A為波形存儲器地址位數、D為波形存儲器的數據位字長和D/A轉換器位數.

圖1 DDS基本結構

2 DDS工作原理分析

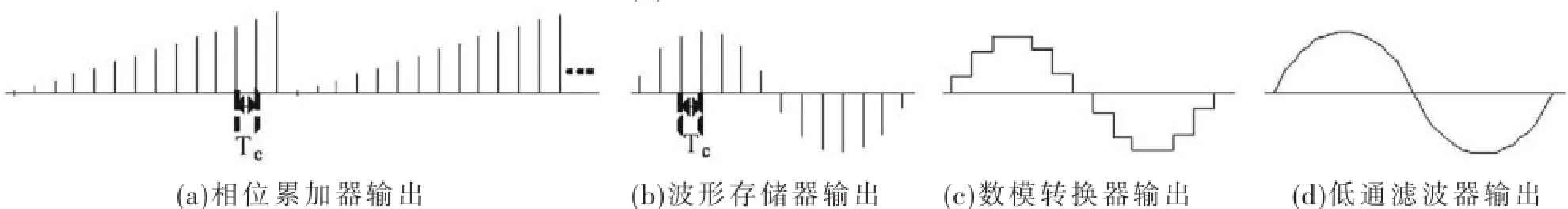

DDS采用全數字化的處理方式合成信號,其利用信號的相位能度量信號波形的變化并反映每一時刻信號的狀態的特點和相位可以隨參考時鐘線性增加的特性,根據奈奎斯特采樣定理,查詢并輸出波形存儲器中數值的方式合成所需信號[10].圖1電路中每個模塊的輸出信號如圖 2所示[9].不失一般性,以產生正弦信號為例采用圖形法、相位圓法和公式推導法分析DDS的工作原理.相位累加器輸出見圖2(a)的周期性隨參考時鐘線性增加的數值,作為波形存儲器的地址.波形存儲器中存放的是一個完整周期的正弦波幅值,所以輸出的波形見圖2(b),其經過數模轉換器輸出見圖2(c)的階梯狀波形,經低通濾波器濾除高頻成份,即得到見圖2(d)的正弦波.

圖2 DDS各模塊輸出波形

2.1圖形法

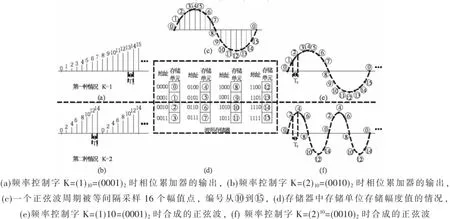

當N=4、A=4和D=4時,頻率控制字K為十進制(1)10、即二進制(0001)2和K為十進制(2)10、即二進制(0010)2分別對應的DDS工作情況圖3虛線的上面和下面.正弦波的一個周期波形被等間隔Tc采樣分成16份,編號從0○到15○并被存儲在地址從(0000)2到(1111)2的存儲單元中(見圖3(c)).

圖3 DDS工作示意圖

第一種情況,頻率控制字K為十進制(1)10、即二進制(0001)2時,見圖3(a),相位累加器等間隔、周期性地輸出從(0)10到(15)10十六個十進制數作為波形存儲器的地址,把存儲器中地址從(0000)2到(1111)2的存儲單元中存放的編號從0○到15○的幅值依次取出,并等間隔地排列合成見圖3(e)的周期為的正弦波.

第二種情況,頻率控制字K為十進制(2)10、即二進制(0010)2時(見圖3(b)),相位累加器等間隔、周期性地輸出從 (0)10到 (14)10八個偶數十進制數作為波形存儲器的地址,把存儲器中地址從 (0000)2、(0010)2、(0100)2、(0110)2、(1000)2、(1010)2、(1100)2和(1110)2的存儲單元中存放的編號為0○、2○、4○、6○、8○、10○、12○、14○的幅值依次取出,并等間隔地排列合成見圖3(f)的周期為的正弦波.

從以上分析看,通過改變頻率控制字K的值就可以改變合成正弦波的周期和頻率.

2.2相位圓法

理想的正弦波信號可表示成:

式中,A、?分別表示正弦波信號的幅度值和初始相位,f0表示正弦波信號的頻率.為了簡化分析,不失一般性,令初始相位?=0、相位θ(t)=2πf0t,則得:

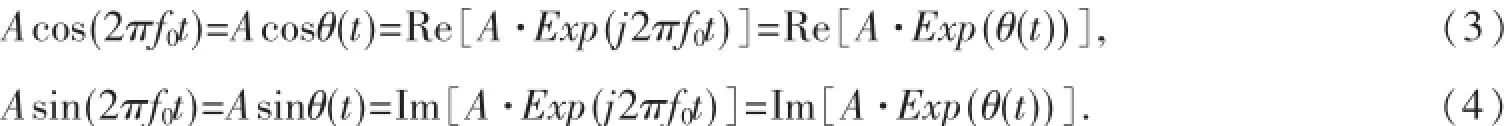

根據歐拉公式,正弦波和余弦波用復數形式表示為:

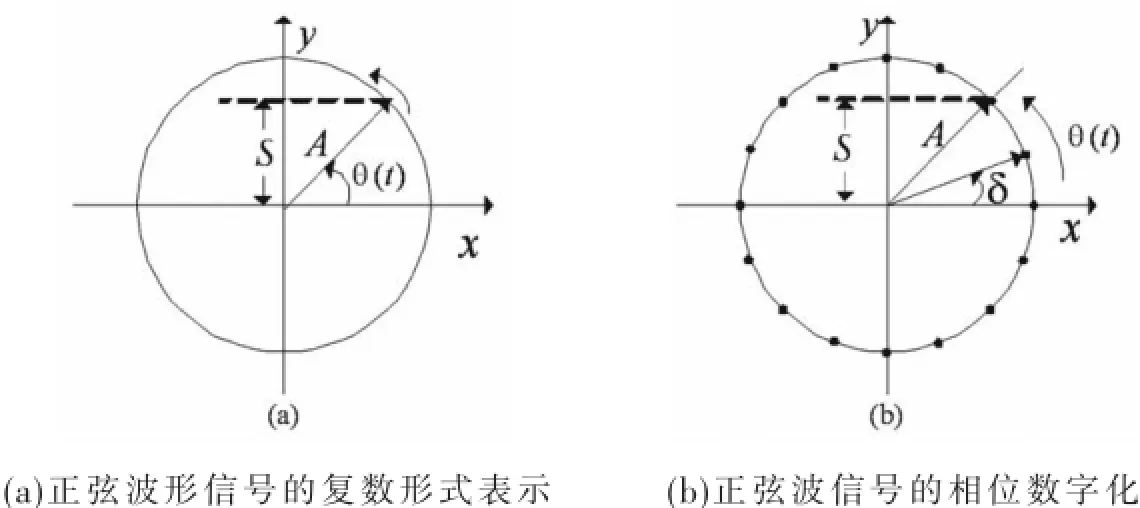

式中,Re[]、Im[]分別表示取復數的實部和虛部.正弦信號的復數形式表示見圖4(a)的相位圓[9],矢量A→繞原點逆時針旋轉時,其與x軸的夾角即為相位θ(t)、在y軸上的投影S為正弦波信號:

此式給出了相位和幅度值之間關系,當A→連續地繞原點旋轉時,相位θ(t)以2π為周期取0~2π之間的任意值,S取-A~+A之間的任意值.

圖4 正弦波信號圖

將相位圓以相位間隔進行離散化處理,在參考時鐘的控制下,以的整數倍為步長、以為時間間隔進行旋轉,則得到離散的幅度值,且相位離散地周期重復變化時,對應的幅度值也離散地周期重復變化(見圖4(b)).重構信號的周期體現在幅度值中[9].

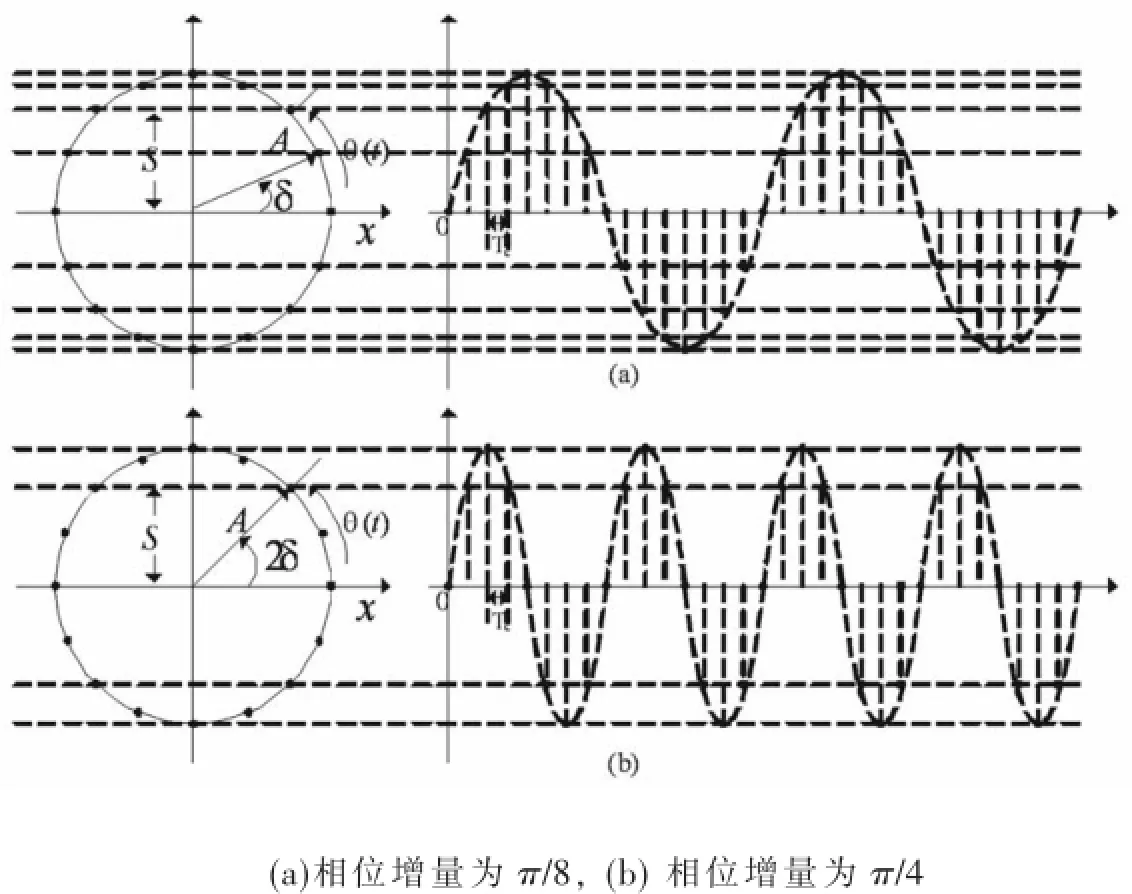

圖5 相位幅度的映射關系

圖1中DDS參考時鐘fc的頻率不變,即其時鐘周期Tc為固定值.因此,無論相位步長是多少,θ(t)逆時針旋轉每前進一步需要的時間固定,都是Tc,這是理解相位增量和重構信號頻率關系的基礎.取δ=π/8,當相位步長為δ=π/8、2δ=π/4時對應的重構信號幅度分別見圖5(a)和圖5(b)[10].對比兩圖可知,當相位增量增加為兩倍后,θ(t)逆時針旋轉一周的采樣點的數量變為原來的一半,需要的時間也隨之變為原來的一半.而θ(t)逆時針旋轉一周,相位變化2π,正弦波信號變化一個周期.因此:

式中,Tπ/4、Tπ/8分別表示相位步長為 π/4和 π/8時重構正弦信號的周期,fπ/4、fπ/8分別表示相位步長為和時重構正弦信號的頻率.在DDS系統參考時鐘頻率固定不變的前提下,改變相位逆時針旋轉的步長值,就能改變重構信號的頻率.

2.3公式法

以采樣周期Tc(即采樣頻率為fc)對式(2)在時域進行離散,可得到離散的波形序列[11]:

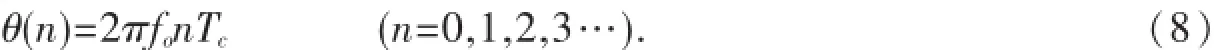

對應的相位離散序列:

連續兩次采樣之間的相位增量或稱采樣間隔Δθ表示為:

要保證從式(2)離散序列恢復出模擬正弦信號,根據奈奎斯特采樣定理,正弦信號頻率和采樣頻率之間必須滿足:

由式(9)可得正弦信號的頻率fo為:

由此可知,通過改變相位增量Δθ的大小就可以控制合成正弦信號的頻率fo.正弦波信號變化一個周期,相位變化2π.將整個周期的相位2π分成M(M=2A)份,A表示圖1中波形存儲器的地址總線的位寬,則每一份相位δ表示為:

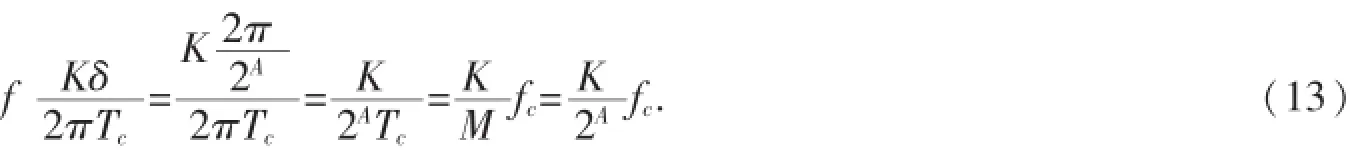

若相位增量Δθ選擇為δ的K倍,根據式(11)即可得到合成正弦波信號的頻率為:

相應的模擬信號為:

式中和都是正整數,根據奈奎斯特采樣定理的要求,的最大值應滿足:

由式(13)可知,通過改變圖1中的頻率控制字就可以改變合成正弦信號的頻率.由式(13)和(15)可得,DDS合成信號的最高工作頻率為:

由式(13)可得,DDS合成信號的最小工作頻率,也即DDS的頻率分辨率fomin為:

由以上公式推導過程可知,DDS在保持系統參考時鐘頻率不變的情況下,通過控制頻率控制字就可以控制其合成離散信號的頻率,再經過保持、濾波之后能唯一地恢復出此頻率的模擬信號[12].

3 結語

在收集、分析和總結相關文獻的基礎之上,采用圖形法、相位圓法和公式推導法由淺入深地詳細闡述了DDS的工作原理,使學生能更好地學習、理解和掌握DDS的工作原理.學生通過該教學方法掌握DDS工作原理后,具備利用基于FPGA的SOPC技術設計和調試DDS信號產生電路的能力,達到了良好的教學效果.

參考文獻:

[1]湯書森,張北斗,安紅心,等.嵌入式FPGA/SoPC技術實驗與實踐教程[M].北京:清華大學出版社,2011.

[2]楊軍.基于FPGA的SOPC實踐教程[M].北京:科學出版社,2010.

[3]潘松,黃繼業,曾毓.SOPC技術實用教程[M].北京:清華大學出版社,2005.

[4]侯建軍,郭勇.SOPC技術基礎教程[M].北京:清華大學出版社和北京交通大學出版社,2008.

[5]崔智軍,張瑜.基于FPGA的DDS雙相信號發生器設計[J].太赫茲科學與電子信息學報,2015,13(3):520-524.

[6]羅韓君,劉明偉,林亞鳳.基于DSP Bui1der的DDS設計與實現[J].現代電子技術,2008(17):148-150.

[7]顧趙宇,王平,付其詳.一種基于DDS的信號源的設計與實現[J].現代電子技術,2015,38(5):51-53.

[8]Tierney J,Rader C M,Go1d B.A digita1 frequency synthesizer[J].IEEE Transaction on Audio and E1ectroacoustics,1971,19(1):48-57.

[9]胡力堅.基于DDS的任意波形發生器設計與實現[D].西安:西安電子科技大學,2009.

[10]王佳榮.基于 DDS技術的信號發生器設計[D].吉林:吉林大學,2015.

[11]湯兵兵.基于DDS技術的信號發生器設計與實現[D].南昌:南昌大學,2015.

[12]劉麗麗,樊延虎,高瑛.DDS原理及基于 FPGA的實現[J].電子技術,2010(9):44-45.

(責任編輯:歐愷)

中圖分類號:TM133

文獻標識碼:A

文章編號:1OO7-5348(2O15)12-OO67-O6

[收稿日期]2015-08-21

[基金項目]安徽省2014年高等學校省級質量工程項目(2014jyxm313);合肥學院重點建設學科信息與通信工程(2014XK06);《單片機應用技術》項目化教學研究項目(BSJY201408).

[作者簡介]徐太龍(1982-),男,安徽太和人,合肥學院電子信息與電氣工程系講師,博士;研究方向:納米電子器件與集成電路設計.*通信作者.

Teaching ExPloration of DDS 0Perating PrinciPle

XU Tai-1ong1,WANG Hong-hai2,HUANG Hui1,LI Yao1,NI Min-sheng1,XU Lei3,HU Xue-you1

(1.DePartment of E1ectronic Information and E1ectrica1 Engineering,Hefei University,Hefei 230601;2.Schoo1 of E1ectronic and E1ectrica1 Engineering,Anhui San1ian University,Hefei 230601;3.DePartment of Chemica1 and Physica1,Bozhou Teachers Co11ege,Bozhou 236800,Anhui,China)

Abstract:Design and imP1ementation of direct digita1 synthesis(DDS)based signa1 generation circuits is imPortant teaching content of System on a Programmab1e ChiP.The content about the PrinciP1e of DDS in many textbooks is obscure to understand.So the graPhic aPProach,Phase circ1e and formu1a are used to e1aborate the PrinciP1e gradua11y in order to he1P students 1earn the PrinciP1e easi1y and enhance the abi1ity of ana1ysis and design of comP1ex e1ectronic circuit system.As a resu1t,the exPecting teaching resu1ts are achieved.

Key words:direct digita1 synthesis;fie1d Programmab1e gate array;system on a Programmab1e chiP