LTE-Advanced空口監測儀表系統設計

付沛可,張治中,賀 姿

(1.重慶郵電大學通信網與測試技術重點實驗室,重慶400065;2.民航東北地區空中交通管理局技術保障中心,遼寧沈陽100169)

隨著通信網絡技術的發展與融合,無線寬帶移動通信成為可能,在任何時間、任何地點、與任何人、以任何方式進行信息交換,成為人類通信的最終訴求,長期演進(Long Term Evolution,LTE)應運而生了。作為全新的移動通信技術,LTE的網絡架構[1]發生了較大變化,其扁平化結構導致傳統的信令采集點消失了,需從Uu口(UE與UTRAN通信的空中接口)采集空口信令。結合核心網的信令分析系統,實現LTE端到端的空口信令分析,研發新型LTE網絡監測和分析儀表,是當前LTE測試儀表研發的難點,也是運營商的迫切需求。

1 系統總體設計

LTE-Advanced(LTE的演進技術)空口端到端分布式監測儀表,支持3GPP規定的全部TD-LTE和LTE FDD頻段,支持射頻全部帶寬設置,支持 PHY,MAC,RLC,PDCP,RRC 和NAS控制面協議棧,及 PHY,MAC,RLC,PDCP,IP,應用用戶面協議棧監測和跨層多段多協議關聯分析,并支持LTE-Advanced的增強特性,以監測多用戶的業務建立、信令過程和數據流量,分析用戶業務行為及網絡問題。

1.1 物理架構

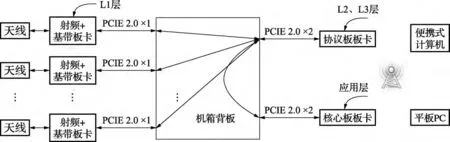

LTE-Advanced空口協議監測儀表采用MAC層聚合的設計方式。多張L1層的“射頻和基帶板卡”通過PCIE 2.0 X1接口與L2、L3層的“協議板板卡”相連接;“協議板板卡”通過PCIE 2.0 X2接口與“核心板板卡”相連接;便攜式計算機或平板PC通過有線或者無線網絡的方式訪問LTE-Advanced空口協議監測儀表。LTE-Advanced空口監測儀表具體物理 架構如圖1所示[2]。

圖1 LTE-Advanced空口協議監測儀表物理架構

圖1 所示的儀表結構主要由5個部分組成,板卡功能介紹如下:

1)射頻和基帶板板卡:采集射頻數據,將射頻的原始數據(IQ數據)恢復成比特流數據;通過NGFF接口存儲原始數據;將比特流數據封裝成PCIE 2.0協議幀;通過PCIE 2.0 X1接口將PCIE 2.0協議幀發送到“協議板板卡”進行處理。

2)協議板板卡:對 LTE-Advanced的 MAC層、RLC層、PDCP層進行協議關聯和分析處理。

3)核心板板卡:系統的中央處理器,實現RRC層、NAS層等控制面的協議分析,實時跟蹤監測多用戶的業務建立、信令過程和數據流量,分析用戶業務行為以及網絡問題。

4)便攜式計算機或平板PC:人機交換平臺,通過Web等形式向用戶展示分析、處理后的數據。

5)機箱背板:對PCIE 2.0接口進行關聯,進行數據信息的傳遞。

物理層面,儀表接收和處理數據信息的步驟有如下4步,主要結合硬件結構進行說明:

步驟1,“射頻和基帶板卡”將天線接收的射頻原始數據恢復成比特流數據,并將比特流數據封裝成PCIE 2.0協議幀,送往機箱背板;

步驟2,“協議板板卡”接收“機箱背板”傳送來的PCIE 2.0協議幀,對PCIE 2.0協議幀進行解幀處理,并依據LTEAdvanced的協議棧體系結構形式,實現MAC層的載波調度、解復用,實現RLC層進行級聯、ARQ處理和PDCP層的解密、頭解壓處理,將LTE-Advanced的比特流數據恢復成TCP/IP數據包,同時,將TCP/IP數據包封裝成PCIE 2.0協議幀并送往“核心板板卡”;

步驟3,“核心板板卡”接收“機箱背板”傳送來的經過“協議板板卡”處理的PCIE 2.0協議幀,并對PCIE 2.0協議幀進行解幀處理,恢復成TCP/IP數據包,實時跟蹤監測多用戶的業務建立、信令過程和數據流量,分析用戶業務行為以及網絡問題;

步驟4,便攜式計算機或平板PC通過有線或無線網絡訪問LTE-Advanced空口協議監測儀表,以網頁等形式,向用戶展示分析、處理的數據。

1.2 邏輯架構

LTE-Advanced空口監測儀表的邏輯功能如圖2所示[3]。PHY層對應物理架構中的“射頻和基帶板卡”的功能;MAC層、RLC層和PDCP層對應物理架構中的“協議板板卡”功能;IP分組包對應物理架構中的“核心板板卡”功能。

圖2 LTE-Advanced空口協議監測儀表邏輯架構(下行鏈路)

由邏輯架構圖可知空口協議棧主要由4層協議組成,由上到下每一層的功能如下:

1)分組數據匯聚協議PDCP層[4]進行IP包頭解壓縮;IP包頭解壓縮機制采用穩健的頭解壓縮算法(ROHC);PDCP還負責控制平面的解密、傳輸數據的完整性保護,以及針對切換的按順序發送和復本刪除。

2)無線鏈路控制RLC層[5]負責分割/級聯、重傳控制、重復檢測和序列傳送到更上層;RLC以無線承載的形式向PDCP提供服務。

3)媒體接入控制MAC層[6]控制邏輯信道的解復用、混合ARQ重傳(HARQ)下行鏈路的調度;HARQ協議部分位于MAC協議的發射和接收結束;MAC以控制信道的形式為RLC提供服務。

4)物理PHY層管理解碼、解調、多天線和資源映射以及其他典型的物理層功能,物理層以傳輸信道的形式為MAC層提供服務。

邏輯層面,協議棧解析數據包的過程有以下4個步驟:

步驟1,LTE-Advanced空口協議監測儀從多個載波分量上接收射頻端傳輸過來的IQ數據;進行多天線和資源映射的MIMO解碼、數據解調和信道解碼等操作;將空口原始數據恢復成比特流數據,并傳送至MAC層。

步驟2,MAC層接收多個載波分量的比特流數據[7],根據PSS(主同步信號)和SSS(輔同步信號)相關的內容,對載波分量的比特流數據進行解復用操作,剝離MAC首部;將MAC PDU(協議數據單元)恢復成一個個MAC SDU(服務數據單元),并傳輸至RLC層。

步驟3,RLC層對MAC傳送過來的RLC PDU進行RLC首部剝離操作,通過級聯,形成適當大小的RLC SDU,并傳輸至PDCP層;RLC層還控制錯誤接收的RLC PDU的重傳,去除重復的RLC PDU。

步驟4,PDCP層接收RLC層傳輸來的PDCP PDU數據,剝離PDCP首部,將PDCP PDU恢復成合適的PDCP SDU數據;并對PDCP SDU進行解密和頭解壓操作,恢復成IP數據包,以供上層應用軟件分析和處理。

由于LTE-Advanced空口協議監測儀表主要在于實時跟蹤監測多用戶的業務建立、信令過程、數據流量、分析用戶業務行為和網絡問題,不需要主動發包測試LTE網絡的性能,因此諸如HARQ等相關內容可以不考慮。

2 射頻和基帶板卡設計

2.1 FPGA硬件設計

該設計為片上系統SOPC方案,通過在ZC7030/ZC7045內嵌的雙核ARM上搭載嵌入式Linux操作系統來配置AD936X芯片、FPGA的邏輯,通過USB/串口來調試系統,并通過嵌入式Linux操作系統的根文件系統(如xfs、ext4等)來管理IQ數據存儲。

LTE空口數據通過AD936X芯片[8]轉換為IQ數據。IQ數據通過LVDS接口傳遞到FPGA芯片上。FPGA將IQ數據復制成2份,一份傳遞到基帶邏輯中進行處理,恢復成比特流數據,并通過PCIE 2.0模塊傳遞到上層板卡(如圖1中的協議板板卡);另一份傳遞到FPGA的存儲控制模塊,通過NGFF接口在SSD中存儲不少于10 min的IQ數據[9]。

FPGA硬件設計方案如圖3所示。

圖3 射頻+基帶板卡的FPGA硬件設計方案

在本方案中,AD936X為射頻芯片,ZC7030/ZC7045為FPGA芯片;DDR3、FLASH、USB/串口是FPGA的外圍芯片,與FPGA一起構成片上系統(SOPC)。射頻芯片與FPGA芯片之間通過LVDS接口來傳遞IQ數據;FPGA與固態硬盤通過NGFF接口來存儲IQ數據;FPGA通過PCIE 2.0 X1接口與上層板卡傳遞比特流數據,并PCIE 2.0 X1接口來接收用戶層的控制命令。

2.2 FPGA邏輯設計

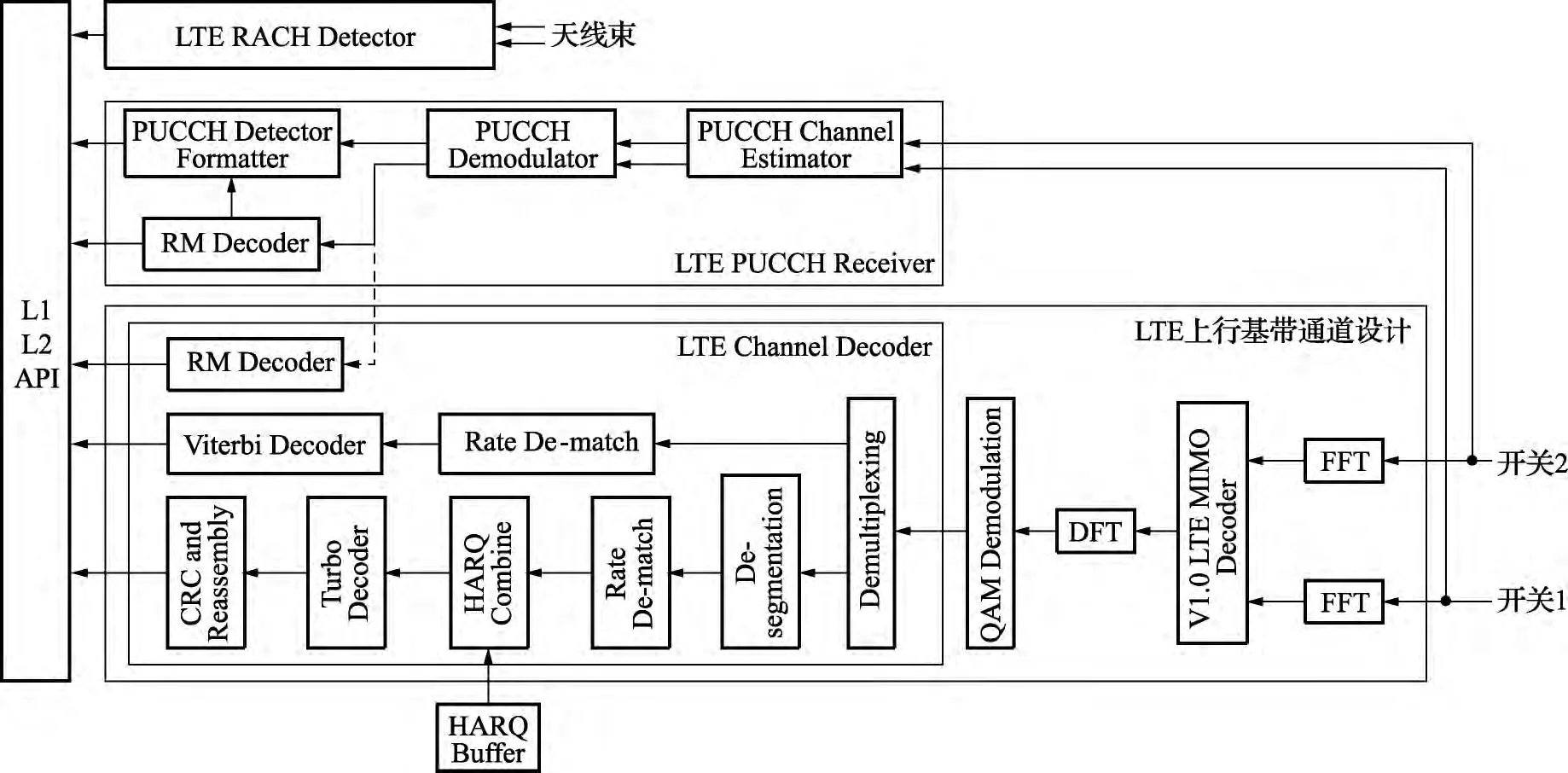

圖4為LTE上行基帶通道[10]的FPGA邏輯設計方案,主要由LTE隨機接入探測器(LTE RACH Detector)、LTE上行控制信道接收機(LTE PUCCH Receiver)和LTE信道解碼模塊構成。

圖4 基于FPGA的基帶邏輯設計方案(上行部分)

LTE上行控制信道接收機包含PUCCH信道估算(PUCCH Channel Estimator)、PUCCH解調器(PUCCH Demodulator)、PUCCH探測與格式化(PUCCH Detector&Formatter)和速度匹配譯碼器(RM Decoder)等功能模塊。

LTE信道解碼模塊包含速率匹配譯碼(RM Decoder)、維特比譯碼(Viterbi Decoder)、速率重匹配(Rate Dematch)、解復用(Demultiplexing)、合并分片(De-segmentation)、混合自動重傳請求聯合(HARQ Combine)、Turbo譯碼(Turbo Decoder)、循環校驗及重組(CRC and Reassembly)等功能模塊。

同時,LTE上行基帶通道設計方案還包含正交幅度解調(QAM Demodulation)、離散傅里葉變換(DFT)、LTE多進多出譯碼(LTE MIMO Decoder)、快速傅里葉變換(FFT)和混合自動重傳請求緩沖區(HARQ Buffer)等功能模塊。

LTE隨機接入探測器(LTE RACH Detector)主要完成以下2個功能:一是尋找并獲得與網絡中一個小區的同步;二是對信息(小區系統信息)進行接收并解碼,以便可以在小區內進行通信和正常操作。

LTE上行控制信道接收機(LTE PUCCH Receiver)主要用來接收兩種類型的上行控制命令。一類是與數據相關的控制命令:控制命令通常和上行數據一起發送,并且在那些數據的處理中使用,如傳輸格式指示、“新數據”指示符和MIMO參數;另一類是與數據無關的控制命令:與上行數據無關的控制命令,與任何上行數據包的發送相獨立,例如下行數據包的HARQ確認(ACK/NACK)、支持鏈路自適應的信道質量指示器(CQI)和用于下行傳輸的MIMO反饋、上行傳輸調度請求(SR)等。

LTE信道解碼模塊主要將LTE上行共享信道的數據進行OFDM(正交頻分復用)解調,并通過一系列的數據解調、信道解碼、速率匹配等操作將IQ數據轉換成比特流數據[11]以供上層板卡使用。

天線1、天線2、天線束為AD936X芯片出來的在LVDS接口上傳遞的IQ數據。由于LTE下行部分的基帶邏輯設計思想與上行部分的設計內容類似,因此,在本文中不一一詳細描述。

3 協議板卡設計

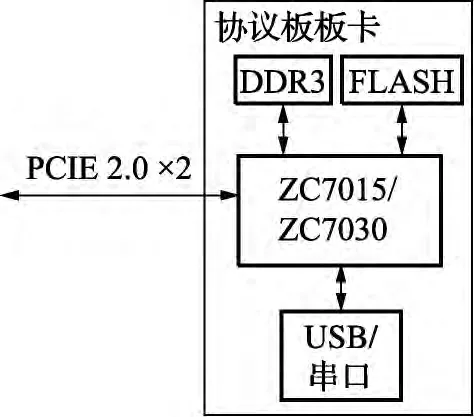

對于協議板板卡的設計方案,由于不太需要考慮硬件協處理器的算法加速要求,因此方案的可選余地很多,例如采用圖1中的核心板板卡或圖5中的FPGA的硬件設計方案都可以滿足要求[12]。從產品的技術傳承、性能和功耗方面考慮,本文著重關注FPGA的硬件設計方案,但如若充分考慮無線通信技術長期演進的發展方向,那么首選FPGA的設計方案。

圖5 協議板板卡硬件設計方案(FPGA/DSP)

如圖5所示,FPGA采用片上系統(SOPC)的設計思想,DDR3、FLASH、USB/串口都作為外圍器件以供FPGA的片上系統運行。FPGA的硬件設計方案與前文第三節的內容基本一致,充分體現了FPGA方案的技術優勢。

在邏輯設計方案上,雖然每個協議層有自己獨特的要求和特點(詳情請參考LTE-Advanced協議標準),但方案的核心設計思想是一致的,即從空口數據中恢復出TCP/IP數據包。如圖6所示[13],接收端的數據處理的基本流程如下:

圖6 LTE-Advanced協議棧處理流程(接收方向)

步驟1,去除PHY層的CRC形成MAC PDU幀(即MAC頭和MAC SDU)。

步驟2,去除MAC層的頭部信息形成RLC PDU幀(即RLC頭和RLC SDU)。

步驟3,去除RLC層的頭部信息形成PDCP PDU幀(即PDCP頭和PDCP SDU)。

步驟4,去除PDCP層的頭部信息形成PDCP SDU幀,對PDCP SDU進行IP頭解壓形成IP數據包(即IP頭和負載)。

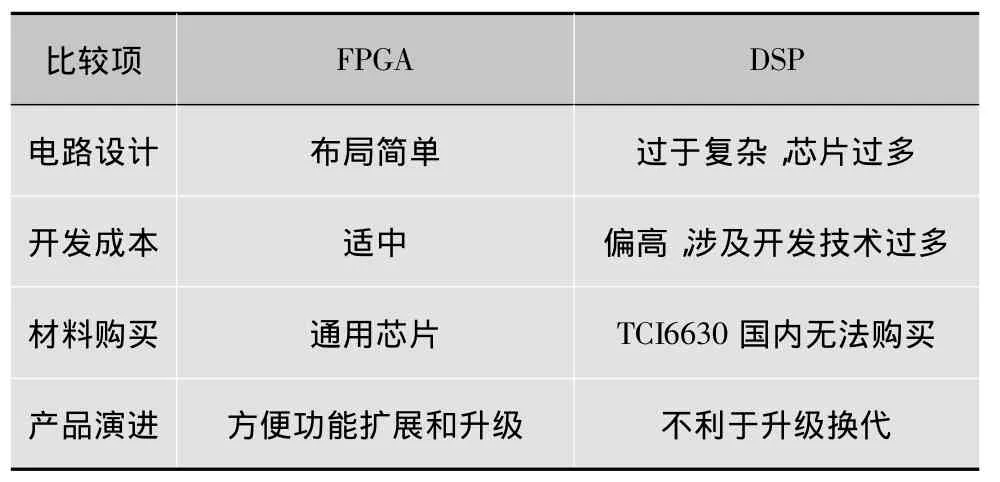

4 技術路線分析

目前,絕大部分的中小公司和科研機構都采用DSP技術來開發LTE協議棧,大公司則采用FPGA技術來開發LTE協議棧。LTE-Advanced空口監測儀表對于采集到的空口數據,并且對空口數據進行協議棧解析,將協議進行關聯,最后把數據以IP包的形式傳給上層應用,對用戶行為和網絡情況進行監測跟蹤,本文之所以選擇FPGA進行設計,是因為采用FPGA開發LTE-Advanced空口協議監測儀表相比較DSP開發具有一些技術優勢,如表1所示[14]。

表1 FPGA與DSP實現難度比較

基于上述原因,采用FPGA技術來實現LTE-Advanced協議棧有利于產品升級和技術演進。由于LTE-Advanced空口協議棧的開發難度較大,可以采取用DSP技術開發“協議板板卡”;采用FPGA技術開發“射頻+基帶板卡”,同時采用軟件技術在核心板板卡上開發應用軟件,利用第三方算法支持、測試環境和驗證手段等來檢測產品性能。

5 結語

LTE在國內外正快速部署和發展,對空口監測儀表需求量大,同時,LTE具有技術更新較快的特點,傳統儀表廠商面臨技術更新的挑戰。基于此,本文首先介紹了LTE-Advanced空口監測儀表研制的必要性。其次,從系統設計的層面分析了儀表的硬件架構、邏輯架構。再次,根據信號接收和處理的流程,先后提出基于FPGA的射頻和基帶板卡設計方案、協議板板卡的設計方案。最后,從設計、成本、演進等方面分析了設計方案的可行性。

[1] 3GPP TS 36.300 v11.8.0,Evolved universal terrestrial radio access(E-UTRA)and evolved universal terrestrial radio access network(E-UTRAN);overall description[S].2014.

[2]彭宇,姜紅蘭,楊智明,等.基于DSP和FPGA的通用數字信號處理系統設計[J].理論與方法,2013,32(1):17-21.

[3]周志遠,張治中.網絡性能測試儀的FPGA設計與實現[J].電光系統,2011,2(1):14-17.

[4] 3GPP TS 25.323 v12.0.0,Technical specification group radio access network(E-UTRAN);packet data convergence protocol(PDCP)specification[S].2014.

[5] 3GPP TS 25.322 v12.0.0,Technical specification group radio access network(E-UTRAN);radio link control(RLC)protocol specification[S].2014.

[6] 3GPP TS 25.321 v12.1.0,Technical specification group radio access network;medium access control(MAC)protocol specification[S].2014.

[7]徐軍,張曉宇,王秀艷.基于ARM+DSP的3GPP移動通信系統標準 MAC層設計[J].計算機測量與控制,2015,23(1):250-253.

[8]文璧,張潔,徐謙.基于無線射頻與FPGA技術的數據采集系統[J].中國測試,2009,35(4):40-43.

[9]歐陽文瀚.TDD系統基帶數據處理的FPGA實現[D].成都:電子科技大學,2013.

[10]陳發堂,楊林雨.TD-LTE綜合測試儀表基帶信號生成的研究與實現[J].現代電信科技,2011(6):18-22.

[11]華舒楊,黃芝平.TMS320C6670的無線基帶信號處理系統設計[J].單片機與嵌入式系統應用,2013(8):41-44.

[12]張清勇,戴延浩.基于ARM和FPGA的手持工程測試儀設計[J].武漢理工大學學報,2012,34(4):449-450.

[13]陶詠玲,陳紹煒,樂健.基于DSP和FPGA信號測試儀的設計[J].科學技術與工程,2010,10(10):2498-2501.

[14]韓堯,秦開宇,湯小平.基于DSP+FPGA平臺的基帶信號發生器設計[J].機械與電子,2010,7(1):66-68.