基于FPGA的超清戶外LED屏數(shù)據(jù)流控制系統(tǒng)*

李志堅(jiān) 吳朝暉 李斌

(華南理工大學(xué)電子與信息學(xué)院)

基于FPGA的超清戶外LED屏數(shù)據(jù)流控制系統(tǒng)*

李志堅(jiān)吳朝暉李斌

(華南理工大學(xué)電子與信息學(xué)院)

針對(duì)現(xiàn)有LED控制系統(tǒng)視頻數(shù)據(jù)采集卡與視頻數(shù)據(jù)接收卡分離的問題,設(shè)計(jì)基于FPGA的超清戶外LED屏數(shù)據(jù)流控制系統(tǒng)。該系統(tǒng)把高清視頻數(shù)據(jù)采集、高速視頻數(shù)據(jù)控制模塊、高速數(shù)據(jù)緩存模塊、非易失性存儲(chǔ)模塊、多路串行視頻數(shù)據(jù)輸出模塊和通信控制模塊集成在一塊電路板,具有高度集成、超大帶寬、超低延遲的特點(diǎn),可實(shí)現(xiàn)1080P全彩色,120幀/秒的視頻播放,系統(tǒng)延遲在2幀以內(nèi)。

FPGA;LED顯示;高速數(shù)據(jù)流控制

0 引言

目前,大型LED顯示屏在戶外廣告、舞臺(tái)布置等領(lǐng)域應(yīng)用廣泛[1-2]。不斷出現(xiàn)的應(yīng)用需求,推動(dòng)了LED顯示屏控制技術(shù)的發(fā)展。大帶寬、高實(shí)時(shí)性是LED高清顯示屏控制技術(shù)的發(fā)展趨勢(shì)。

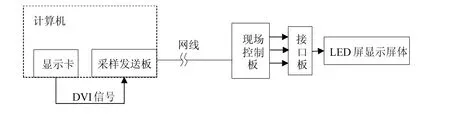

現(xiàn)有的LED顯示屏同步控制系統(tǒng)如圖1[3]所示,一般包括采樣發(fā)送板和多個(gè)級(jí)聯(lián)的現(xiàn)場(chǎng)控制板。采樣發(fā)送板接收視頻源數(shù)據(jù),并在完成數(shù)據(jù)格式轉(zhuǎn)換之后,通過網(wǎng)線或者同軸電纜傳送給現(xiàn)場(chǎng)控制板[4-5]。在分辨率和實(shí)時(shí)性要求不高的應(yīng)用中,該方案具有很好的性能。但要實(shí)現(xiàn)高分辨率和高保真性顯示,現(xiàn)有的方案只有在視頻源與發(fā)送卡之間增加圖像分割設(shè)備,并通過多通道并行的方式才可能實(shí)現(xiàn)。

圖1 典型LED屏控制系統(tǒng)框圖

本文基于FPGA設(shè)計(jì)超清戶外LED屏數(shù)據(jù)流控制系統(tǒng),把高清視頻數(shù)據(jù)采集、高速視頻數(shù)據(jù)控制模塊、數(shù)據(jù)緩存模塊、非易失性存儲(chǔ)模塊、多路串行視頻數(shù)據(jù)輸出模塊和通信控制模塊集成在一塊電路板上,省去了專門的圖像分割和數(shù)據(jù)分發(fā)設(shè)備。

1 系統(tǒng)性能設(shè)計(jì)

1.1系統(tǒng)輸出帶寬設(shè)計(jì)

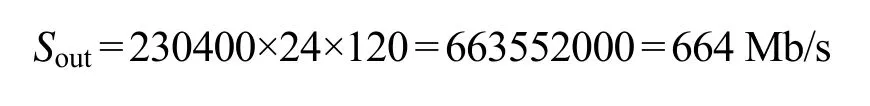

LED屏視頻數(shù)據(jù)流控制系統(tǒng)的核心任務(wù)是根據(jù)所控制的LED顯示屏的拓?fù)浣Y(jié)構(gòu),把來(lái)自于視頻源的高速串行視頻數(shù)據(jù)并行化,以實(shí)現(xiàn)高清LED屏的高刷新頻率。本系統(tǒng)的目標(biāo)高清LED顯示屏包括并行的9個(gè)LED陣列。每個(gè)LED陣列的像素?cái)?shù)目為230400個(gè)。因此,本系統(tǒng)設(shè)計(jì)9個(gè)并行視頻數(shù)據(jù)輸出端口。若播放24位真彩圖像,為保證120 Hz的幀頻,每個(gè)視頻輸出端口最小帶寬為

系統(tǒng)中,控制器除了分配視頻數(shù)據(jù)外,還需要對(duì)顯示控制單元進(jìn)行參數(shù)配置和狀態(tài)回讀,因此實(shí)際數(shù)據(jù)量將略高于Sout。

基于上述通信數(shù)據(jù)量分析,并考慮協(xié)議開銷,系統(tǒng)視頻輸出端口帶寬應(yīng)不低于700 Mb/s,可采用CAT5、CAT5E或者CAT6網(wǎng)線連接。考慮成本等因素,本模塊輸出端口采用CAT5類網(wǎng)線接口。

1.2系統(tǒng)輸入帶寬設(shè)計(jì)

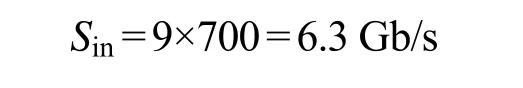

如上所述,每個(gè)顯示控制單元的輸入帶寬為700 Mb/s,數(shù)字收發(fā)模塊的視頻輸入口帶寬最小為

在此基礎(chǔ)上,考慮10%的通信裕量,數(shù)據(jù)收發(fā)模塊視頻輸入端口帶寬應(yīng)不低于7 Gb/s。

在接口設(shè)計(jì)方面,HDMI接口能滿足上述的視頻傳輸帶寬要求。

1.3系統(tǒng)存儲(chǔ)容量設(shè)計(jì)

LED顯示屏是逐點(diǎn)順序顯示的,它利用人眼視覺延遲的特點(diǎn),通過一次快速發(fā)送全屏所有點(diǎn)的圖像實(shí)現(xiàn)全屏圖像顯示更新。因此,為確保圖像正常顯示,在發(fā)送之前,必須先確定顯示屏的走線方式或走點(diǎn)順序。確定走點(diǎn)順序的過程稱為L(zhǎng)ED屏描點(diǎn),它通過間隔一段時(shí)間(如1 s)發(fā)送一個(gè)點(diǎn),然后記錄其位置即可確定。

控制系統(tǒng)在向LED顯示屏發(fā)送數(shù)據(jù)時(shí),嚴(yán)格按照描點(diǎn)文件順序發(fā)送各像素的灰度數(shù)據(jù)。為實(shí)現(xiàn)上述功能,控制系統(tǒng)必須在本地緩存一幀視頻數(shù)據(jù)。此外為了匹配每個(gè)環(huán)節(jié)的輸入輸出速度,也需要對(duì)視頻數(shù)據(jù)進(jìn)行緩存,以實(shí)現(xiàn)諸如乒乓存取等操作。

系統(tǒng)控制的像素總數(shù)為1920×1080=2073600個(gè),若所有像素統(tǒng)一編制,則地址位寬為21位。因此,描點(diǎn)文件緩存空間為

前端數(shù)據(jù)收發(fā)模塊必須在本地緩存一幀視頻數(shù)據(jù),數(shù)據(jù)大小為

此外,為匹配不同速度,要在視頻數(shù)據(jù)處理中間增加乒乓操作,需要消耗一定的存儲(chǔ)資源。FPGA本身的網(wǎng)表文件也需要存儲(chǔ)在收發(fā)模塊本地。因此,收發(fā)模塊中的存儲(chǔ)容量包括上述的所有部分,應(yīng)不低于120 Mb。

2 系統(tǒng)架構(gòu)

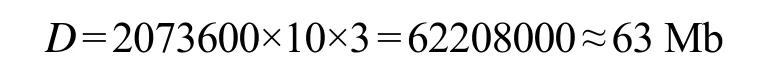

根據(jù)上述性能設(shè)計(jì)要求,系統(tǒng)架構(gòu)如如圖2所示,包括HDMI接口模塊、板上緩存單元,高速串行傳輸模塊、中央控制模塊、USB、LAN和通用IO口。系統(tǒng)還預(yù)留用于移植嵌入式操作系統(tǒng)的系統(tǒng)存儲(chǔ)單元。

圖2 系統(tǒng)架構(gòu)

HDMI接口模塊從視頻源的HDMI接口采集高清視頻數(shù)據(jù)信號(hào)。HDMI主要基于轉(zhuǎn)換最小差分信號(hào)(transition minimized differential signaling,TMDS)技術(shù)傳輸數(shù)字信號(hào)。

板上緩存單元主要用于緩存視頻數(shù)據(jù)處理中間結(jié)果,實(shí)現(xiàn)輸入輸出帶寬匹配。系統(tǒng)采用大容量DDR-3 SDRAM實(shí)現(xiàn)視頻數(shù)據(jù)的高速存取。

根據(jù)系統(tǒng)最終規(guī)模以及前端LED頻的控制接口,本系統(tǒng)的視頻輸出口包括12路CAT-5網(wǎng)線端口,其中9路正常輸出,3路備用。

中央控制模塊是本系統(tǒng)的核心,主要功能包括視頻處理、高速數(shù)據(jù)流控制和通信控制功能。其中,視頻處理包括伽馬矯正等常用處理方法,也包括針對(duì)不同目標(biāo)顯示屏的圖像重構(gòu)。這里圖像重構(gòu)是指中央控制器對(duì)目標(biāo)LED顯示屏進(jìn)行描點(diǎn)操作,建立視頻數(shù)據(jù)與目標(biāo)LED屏像素的映射表,并基于此映射表對(duì)每一幀圖像進(jìn)行圖像重構(gòu)。高速數(shù)據(jù)流控制是指中央控制器接收來(lái)自HDMI接口模塊的視頻數(shù)據(jù),采用乒乓操作的方式把當(dāng)前處理結(jié)果存入SDRAM,同時(shí)從SDRAM中讀取上一幀已處理的視頻數(shù)據(jù),并把這些數(shù)據(jù)通過高速串行傳輸模塊饋送給LED屏。通信控制是指中央控制模塊通過網(wǎng)口、USB口和通用IO接口接收來(lái)自遠(yuǎn)程控制系統(tǒng)的控制命令,并把本機(jī)狀態(tài)信息通過這些接口反饋給遠(yuǎn)程控制系統(tǒng)。

3 系統(tǒng)實(shí)現(xiàn)

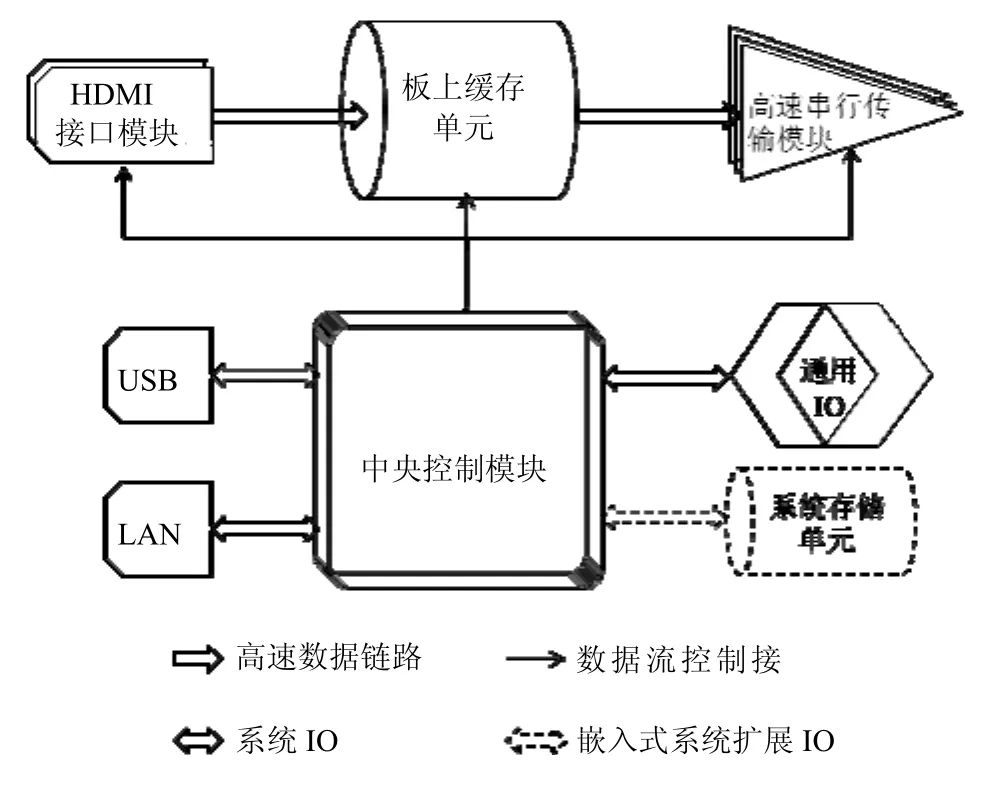

根據(jù)上述分析設(shè)計(jì),系統(tǒng)圍繞超大規(guī)模FPGA構(gòu)件應(yīng)用系統(tǒng),系統(tǒng)內(nèi)部拓?fù)淙鐖D3所示。

圖3 系統(tǒng)內(nèi)部拓?fù)?/p>

3.1HDMI接口

根據(jù)前文分析,視頻接口帶寬應(yīng)不低于7 Gb/s。考慮通信裕量,系統(tǒng)視頻接口帶寬設(shè)置為7.5 Gb/s。本系統(tǒng)采用ADV7619[6]芯片實(shí)現(xiàn)高速視頻數(shù)據(jù)流的接收。該芯片可支持最高達(dá)1080 P 36位深色/2160 P 8位的高清電視格式和最高達(dá)4 k × 2 k(3840 × 2160,30 Hz)的顯示分辨率,能夠滿足系統(tǒng)1 k × 2 k(1080× 1920,120 Hz)顯示分辨率及刷新速率。

3.2FPGA

FPGA選型考慮以下幾點(diǎn):1) 本系統(tǒng)的緩存采用DDR SDRAM,因此所選FPGA應(yīng)支持DDR-III接口開發(fā)能力;2) 由于本系統(tǒng)需高速處理視頻數(shù)據(jù),在LED屏分辨率較高時(shí),要消耗大量的邏輯資源,低成本的Cyclone系列FPGA無(wú)法滿足項(xiàng)目需求,因此本系統(tǒng)采用Arria V GX系列FPGA[7]。

Arria V GX使用28 nm低功耗工藝實(shí)現(xiàn)最低靜態(tài)功耗。在中端應(yīng)用中,總功耗是最低的,還提供速率高達(dá)10.3125 Gb/s的低功耗收發(fā)器,設(shè)計(jì)了具有硬核IP的優(yōu)異架構(gòu),從而降低動(dòng)態(tài)功耗。與前一代中端FPGA相比,Arria V器件的平均功耗降低了40%。

單片F(xiàn)PGA滿足項(xiàng)目IO需求的封裝為F1152和F1517。但在實(shí)際設(shè)計(jì)時(shí),由于不同接口的電平標(biāo)準(zhǔn)不一致,F(xiàn)PGA的IO利用率不能達(dá)到100%,同時(shí)考慮到大封裝扇出困難,本系統(tǒng)采用主從FPGA的方式來(lái)實(shí)現(xiàn)。

主FPGA完成視頻數(shù)據(jù)的接收、顯示屏描點(diǎn)、DDR3存儲(chǔ)器接口等功能,需求的邏輯資源比較高,且要求具有DDR3存儲(chǔ)器接口硬核和PCIE硬核,因此采用5AGXFB7D6F35C6N,該芯片為F1152封裝。從FPGA主要完成視頻數(shù)據(jù)的多路分發(fā),擬采用5AGXBA5D6F27C6N,該芯片為F672封裝。主從FPGA之間從高速串行接口交換數(shù)據(jù)。

3.3SDRAM

本控制模塊的目標(biāo)屏分辨率是1920×1080 P,在無(wú)壓縮情況下,一幀圖像的數(shù)據(jù)量為1920×1080×30 = 62 Mb。為匹配收發(fā)速率,同時(shí)完成描點(diǎn)功能,控制器需采用乒乓操作。因此,控制模塊視頻數(shù)據(jù)緩存容量不低于130 Mb。這個(gè)存儲(chǔ)要求,目前在單片F(xiàn)PGA內(nèi)部尚不能實(shí)現(xiàn),需在片外擴(kuò)展大容量存儲(chǔ)器。

同時(shí),為保證120 Hz幀頻,片外存儲(chǔ)器實(shí)際吞吐率應(yīng)不低于7.5 Gb/s,即240 MDW/s(1 DW = 32 b)。

能達(dá)到上述吞吐率要求的片外存儲(chǔ)技術(shù)包括SRAM和DDR SDRAM。因大容量SRAM價(jià)格昂貴,本系統(tǒng)采用片外擴(kuò)展DDR SDRAM的方案實(shí)現(xiàn)視頻數(shù)據(jù)高速緩存。

為了保證1080 P的LED顯示屏分辨率和120 Hz的幀頻,作為視頻數(shù)據(jù)緩存的DDR SDRAM訪問帶寬應(yīng)不低于7.5 Gb/s,同時(shí)考慮數(shù)據(jù)格式轉(zhuǎn)換和數(shù)據(jù)對(duì)齊,DDR SDRAM訪問帶寬應(yīng)不低于10 Gb/s。

考慮硬件的穩(wěn)定性,系統(tǒng)采用DDR3 SDRAM,工作頻率為800 MHz。在具體選型上,采用H5PS5162GFR-S5C[8]。該芯片是DDR3 SDRAM,工作時(shí)鐘800 MHz,存儲(chǔ)容量512 Mb,數(shù)據(jù)位寬為16 B。設(shè)計(jì)時(shí),采用兩片并聯(lián)形成1個(gè)32 B數(shù)據(jù)總線。

3.4其他電路

系統(tǒng)視頻輸出口采用網(wǎng)口形式,所用的PHY芯片選型主要考慮1000 b/s的傳輸帶寬。從技術(shù)支持的角度,本系統(tǒng)采用RTL8211芯片。

USB接口主要完成系統(tǒng)參數(shù)配置和系統(tǒng)調(diào)試,本系統(tǒng)擬采用CY3014芯片,該芯片具有1個(gè)可進(jìn)行完全配置的并行通用可編程接口GPIF II,它可與任何處理器、ASIC或 FPGA連接。

網(wǎng)絡(luò)控制器采用RTL8111C-GR以太網(wǎng)控制器,該芯片內(nèi)部集成了兼容IEEE 802.3 10/100/1000 Mb/s媒體接口控制器(MAC)、10/100/1000 Mb/s以太網(wǎng)收發(fā)模塊(PHY)、PCIE總線控制器和嵌入式存儲(chǔ)單元。

4 結(jié)語(yǔ)

LED全彩同步控制系統(tǒng)具有高性能、實(shí)時(shí)顯示、節(jié)能、環(huán)保等優(yōu)點(diǎn),是現(xiàn)代信息發(fā)布的重要媒體。本文改變傳統(tǒng)設(shè)計(jì)發(fā)送卡與接收卡分開的結(jié)構(gòu),把視頻數(shù)據(jù)采集、分割、格式轉(zhuǎn)換和發(fā)送集成在一張卡上。系統(tǒng)充分利用可編程邏輯的控制性能強(qiáng),開發(fā)靈活和資源豐富的特點(diǎn),以高性能FPGA為核心,結(jié)合高速緩存DDR3 SDRAM技術(shù),設(shè)計(jì)了高度集成的超清戶外LED屏數(shù)據(jù)流控制卡。設(shè)計(jì)帶寬達(dá)到7.5 Gb/s,能滿足1080 P高清視頻放送,傳輸延遲不超過1楨。系統(tǒng)具有成本低、顯示面積大、顯示穩(wěn)定、刷新率高、規(guī)模可擴(kuò)展等特點(diǎn),是目前市面上具有競(jìng)爭(zhēng)力的顯示控制方案。

[1] 李韜.LED電子顯示屏控制系統(tǒng)設(shè)計(jì)[J].科技與創(chuàng)新,2015(18):73,76.

[2] 趙紅艷.LED 顯示屏控制系統(tǒng)的分析與設(shè)計(jì)[J].電子技術(shù)與軟件工程,2015(4):82.

[3] 劉麗莎 朱樺 韓秀清.基于網(wǎng)口傳輸?shù)腖ED同步屏控制系統(tǒng)及其FPGA實(shí)現(xiàn)[D].電子設(shè)計(jì)工程,2010,18(2):63-66.

[4] 魏洵佳.超高清LED顯示屏單卡網(wǎng)線控制系統(tǒng)設(shè)計(jì)[J].北京信息科技大學(xué)學(xué)報(bào),2012,27(3):68-72.

[5] 王燕.多LED顯示屏協(xié)同控制系統(tǒng)設(shè)計(jì)及應(yīng)用[J].西安工程大學(xué)學(xué)報(bào),2015,29(2):187-194.

[6] www.analog.com,Dual PortXpressview3 GHz DMI Receiver ADV7619 datasheet[Rev.C].

[7] www.altera.com,Arria V GX, GT, SX, and ST Device Datasheet[Rev.3.3].

[8] www.hynix.com, DDR3L Device Operation.

Ultra-HD Outdoor LED Screen Data Flow Control System Based on FPGA

Li ZhiijanWu ZhaohuiLi Bin

(School of Electronic Engineering, South China University of China)

In current LED control systems, the video data acquisition card and video data receiving card are separated from each other. The ultra high definition outdoor LED screen data flow control system is designed based on FPGA. In the proposed system, the video data acquisition, high speed video data controller and buffer, non nonvolatile memory, multi serial video data output module and communication control module are integrated on a single circuit board. The system is characterized by high degree of integration, ultra large bandwidth and ultra low delay. It can achieve 1080 P full color, 120 frames per second video playback, with the system delay in 2 frames or less.

FPGA; LED Display; High Speed Data Flow Control

李志堅(jiān),男,1981年生,講師,主要研究方向:高速數(shù)字信號(hào)處理及系統(tǒng)設(shè)計(jì)、RFID應(yīng)用技術(shù)。E-mail: Lizhjian@scut.edu.cn

廣州市科技計(jì)劃項(xiàng)目產(chǎn)學(xué)研專項(xiàng)(2014Y2-00018);荔灣區(qū)產(chǎn)學(xué)研合作項(xiàng)目(20144815023)。