多路并行FFT算法的FPGA實現(xiàn)技術(shù)

占席春 蔡費楊 王偉

摘 要: 以雷達偵察接收機為應(yīng)用背景,利用FPGA芯片并行工作的特性,設(shè)計一種并行加流水線處理模式的FFT處理器結(jié)構(gòu),實現(xiàn)寬帶數(shù)字測頻。在2.4 GSPS采樣率下,選取基?2頻域抽取(DIF)算法,采用每通道512點流水結(jié)構(gòu)FFT、8通道并行處理的設(shè)計思路,以達到單通道4 096點FFT的處理效果。在保證分辨率的同時,采樣數(shù)據(jù)能夠被實時處理。仿真結(jié)果顯示,在300 MHz時鐘下,F(xiàn)PGA完成4 096個數(shù)據(jù)的緩存和FFT運算只需要2.1 μs,滿足雷達偵察接收機對數(shù)據(jù)處理速度的要求。

關(guān)鍵詞: FFT; 測頻; 流水結(jié)構(gòu); 并行處理模式; FPGA

中圖分類號: TN957.51?34 文獻標(biāo)識碼: A 文章編號: 1004?373X(2015)19?0033?04

Abstract: Based on the application background of radar reconnaissance receiver and the parallel operation behavior of FPGA chip, an FFT processor structure combining the parallel processing mode with pipeline processing mode was designed to realize the digital frequency measurement of broadband. At the sampling rate of 2.4 GSPS, the radix?2?based decimation in frequency (DIF) algorithm is selected, the design thought of 512?point pipeline structure FFT for each channel and 8?channel parallel processing is adopted to achieve the processing effect of 4 096?point FFT in single channel. The sampling data can be processed in real time while the resolution is ensured. The simulation results show that it only takes 2.1 μs for FPGA to finish the 4 096 data caching and FFT operation at 300 MHz, which can meet the requirements of radar reconnaissance receiver to data processing speed.

Keywords: FFT; frequency measurement; pipeline structure; parallel processing mode; FPGA

0 引 言

傳統(tǒng)的數(shù)字測頻方法有直接測頻法,相位推算法、過零檢測法、FFT頻域算法等。直接測頻法精度較低,不適合在硬件上大規(guī)模實現(xiàn),相位推算和過零檢測方法對信噪比要求比較高,而FFT頻域算法信噪比要求低,適合高密度信號及雷達脈內(nèi)有頻率調(diào)制的情況[1],相對于測相,它是一種比較精確的測頻方法[2]。與傳統(tǒng)DSP測頻相比,F(xiàn)PGA數(shù)字測頻具有易于實現(xiàn)并行算法、精度高、開發(fā)周期短、處理速度快等優(yōu)點[3]。因此本文研究在FPGA上實現(xiàn)FFT頻域算法。

1 設(shè)計方案

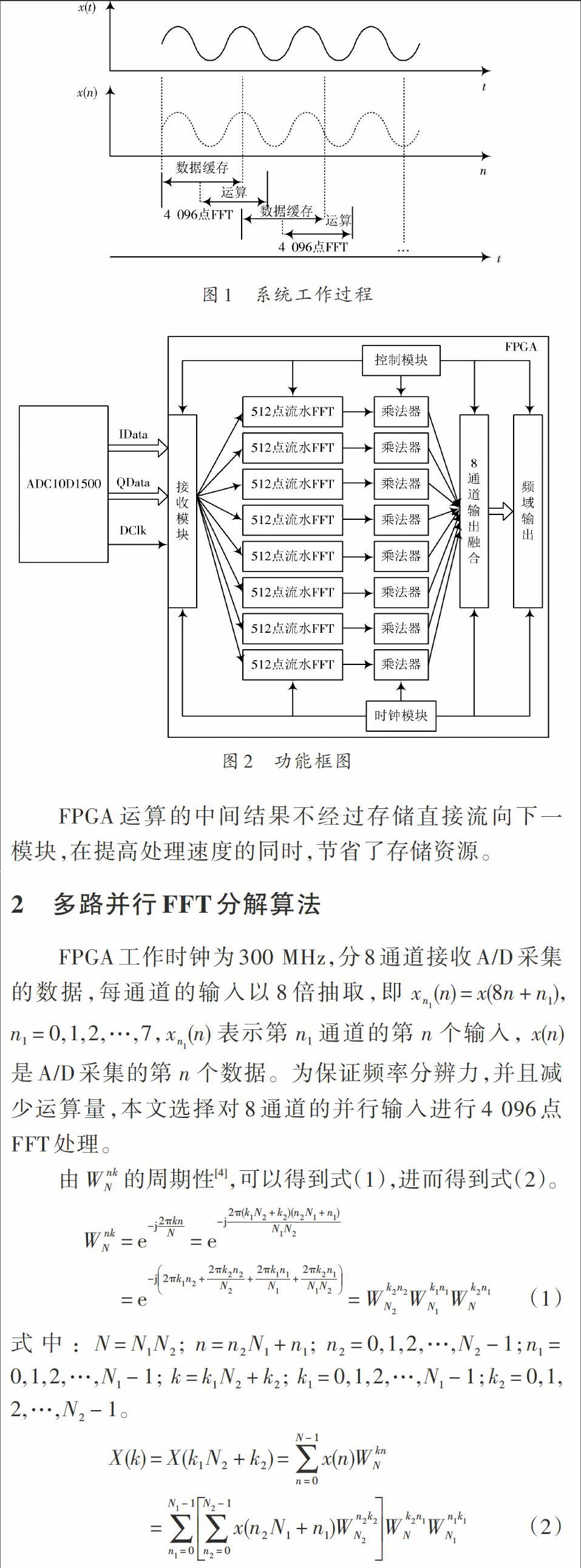

測頻系統(tǒng)主要由采集和處理兩部分組成,其工作過程如圖1所示。系統(tǒng)每緩沖半幀數(shù)據(jù)開始運算,而且在處理該幀數(shù)據(jù)的同時,也在緩存下一幀數(shù)據(jù)。這樣,F(xiàn)PGA能夠?qū)崟r處理A/D采集的全部數(shù)據(jù),避免信號的漏檢,實現(xiàn)對信號的連續(xù)處理。圖2給出系統(tǒng)的功能框圖,圖中ADC10D1500是一款具有高性能、低功耗、10 b精度等特性的芯片。在本文的研究中,配置A/D分I和Q兩個通道輸出數(shù)據(jù),采樣速率為2.4 GSPS。由于FPGA工作時鐘與A/D采樣頻率不匹配,本文采用8通道并行處理方法,實現(xiàn)高性能FFT處理器。

FPGA完成信號時域到頻域的轉(zhuǎn)換如圖2所示,包括接收模塊,控制模塊,時鐘模塊,512點流水結(jié)構(gòu)FFT模塊,乘法模塊,8通道輸出融合模塊,頻域輸出模塊。

接收模塊用于接收和傳遞A/D采集的數(shù)據(jù),控制模塊負責(zé)其他模塊的復(fù)位和使能,時鐘模塊輸出其他模塊的時鐘信號。512點流水結(jié)構(gòu)FFT模塊用于數(shù)據(jù)的運算處理,8通道輸出融合模塊實現(xiàn)最終結(jié)果的綜合處理,頻域輸出模塊獲取信號的功率譜。

FPGA運算的中間結(jié)果不經(jīng)過存儲直接流向下一模塊,在提高處理速度的同時,節(jié)省了存儲資源。

2 多路并行FFT分解算法

FPGA工作時鐘為300 MHz,分8通道接收A/D采集的數(shù)據(jù),每通道的輸入以8倍抽取,即[xn1(n)=x(8n+n1),][n1=0,1,2,…,7,][xn1(n)]表示第[n1]通道的第[n]個輸入,[x(n)]是A/D采集的第[n]個數(shù)據(jù)。為保證頻率分辨力,并且減少運算量,本文選擇對8通道的并行輸入進行4 096點FFT處理。

由式(2)的推導(dǎo)可知:在設(shè)計4 096點FFT時,需要對每通道數(shù)據(jù)進行512點FFT處理,然后將每通道輸出乘以復(fù)數(shù)因子[Wk2n14 096]([k2]是第[n1]通道的輸出系數(shù)),最后進行8通道輸出融合,即8點FFT處理。

3 系統(tǒng)設(shè)計

3.1 單通道流水結(jié)構(gòu)

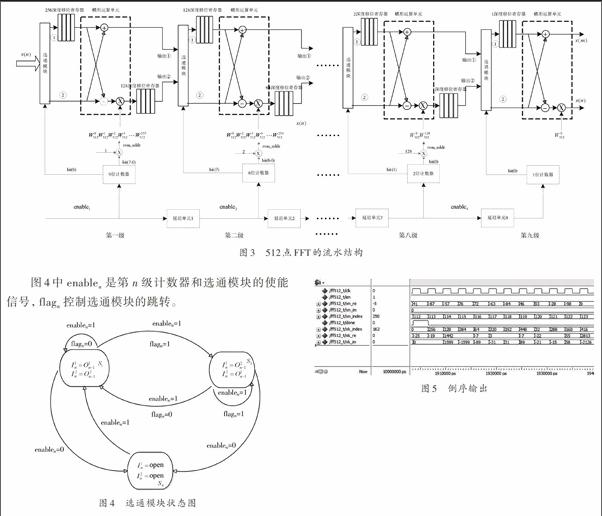

該設(shè)計采用基?2頻域抽取方法,不需要對輸入數(shù)據(jù)倒序處理,簡化了地址的控制。圖3是單通道512點FFT的流水結(jié)構(gòu),總共分為9級,每一級主要包括蝶形運算單元、選通模塊、基于RAM的移位寄存器、計數(shù)器、存儲旋轉(zhuǎn)因子的ROM以及使能信號延時模塊。endprint

蝶形運算模塊是FFT的基本單元,移位寄存器作為每級輸入和輸出的緩沖器,選通模塊控制數(shù)據(jù)的流向。為了方便,圖3中第[n]級的輸入①記為[I1n,]輸入②記為[I2n,]輸入端的寄存器記為[IRn,]輸出端的寄存器記為[ORn,]輸出①記為[O1n,]輸出②記為[O2n]。

第一級開始工作時,[I11]接收數(shù)據(jù)并將其緩存至深度為256的[IR1]中,[I21]斷開。當(dāng)[IR1]被填滿時,即[x(255)]進入[IR1,][I11]斷開,[I21]接收數(shù)據(jù)。這樣[IR1]輸出的[x(0)]和[I21]接收到的[x(256)]同時進入蝶形單元,經(jīng)過運算后,蝶形單元上節(jié)點的輸出流經(jīng)[O11]進入深度為128的[IR2]中,下節(jié)點的輸出則放入深度為128的[OR1]中。當(dāng)[IR2]被填充滿時,[OR1]也被填充滿,此時流經(jīng)[O11]的前128個數(shù)據(jù)全部輸出,第二級選通模塊發(fā)生跳轉(zhuǎn)。

此后通過[O11]的后128個數(shù)據(jù)將依次到達[I22],與[IR2]的輸出一同進入蝶形單元。 同時[OR1]的輸出將會流經(jīng)[O21]到達[I12,]并填充[IR2]的空白位置。當(dāng)流經(jīng)[O21]的前128個數(shù)據(jù)全部輸出,[IR2]被新的數(shù)據(jù)填充滿,第二級選通模塊再次發(fā)生跳轉(zhuǎn),經(jīng)過[O21]的后128個數(shù)據(jù)將依次到達[I22],與[IR2]的輸出一起進入蝶形單元。而第一級選通模塊在[IR1]為空時就發(fā)生跳轉(zhuǎn),繼續(xù)緩存下一幀的數(shù)據(jù)。經(jīng)過128個周期,該幀數(shù)據(jù)在第一級中的處理結(jié)束,后幾級的運算流程與之類似。

選通模塊對數(shù)據(jù)流向的控制較為關(guān)鍵,其狀態(tài)轉(zhuǎn)移圖如圖4所示。

(1) 初始狀態(tài)[S0,]使能信號[enablen]為低,[I1n]斷開,[I2n]斷開。

(2) 使能信號變高,進入狀態(tài)[S1,][I1n]連通[O1n-1,][I2n]連通[O2n-1]。

(3) 標(biāo)志位[flagn]變高,進入狀態(tài)[S2],[I1n]連通[O2n-1,][I2n]連通[O1n-1]。

(4) 標(biāo)志位[flagn]變低,進入狀態(tài)[S1]。

(5) 重復(fù)過程(3)。

計數(shù)器輸出的最高位(MSB)作為選通模塊跳轉(zhuǎn)的標(biāo)志位[flagn]。第一幀數(shù)據(jù)到達各級的時間不同,因此每級計數(shù)器的使能時刻也不同。使能信號[enable1]變高時,數(shù)據(jù)[x(n)]開始進入第一級。經(jīng)過256個周期,進入蝶形單元,之后進入下一級。因此延遲單元1需延遲256個周期加上蝶形單元消耗的時間,依次類推,單元[n]需延遲[2562n]個周期加上蝶形單元消耗的周期。

旋轉(zhuǎn)因子按照[W0512]~[W511512]順序存入ROM中。分析每級旋轉(zhuǎn)因子出現(xiàn)的規(guī)律,得到其在ROM中的地址表達式(rom_addr)為[2n-1?c(w-2 ∶ 0),]其中[n]表示級數(shù),[c]是第[n]級計數(shù)器的輸出,[w]是計數(shù)器的位寬。

第九級的兩路輸出分別按地址遞增順序存入兩個深度為256的RAM中,然后輪流讀取兩個RAM,得到倒序的FFT結(jié)果,其對應(yīng)的系數(shù)由倒序計數(shù)模塊產(chǎn)生。圖5給出 FFT的倒序輸出,圖中xk_index是倒序輸出的系數(shù)。

由于只有一路數(shù)據(jù)[x(n),][IR1]在緩沖前半幀數(shù)據(jù)時,第一級和第二級之間沒有數(shù)據(jù)傳遞。因此在輸出模塊中,對兩個RAM進行256個周期的寫操作之后,會有256個周期的等待,然后繼續(xù)下一幀數(shù)據(jù)的寫操作,而讀操作是連續(xù)的。

3.2 八通道輸出融合處理

每通道的輸出需要乘以復(fù)數(shù)因子[Wk2n1N,]其中[k2=0,1,2,…,511,]是FFT輸出對應(yīng)的系數(shù);[n1]表示通道數(shù);[N=4 096;][k2?n1]是復(fù)數(shù)因子在ROM中的地址。模塊選取xilinx提供的復(fù)數(shù)乘法ipcore。

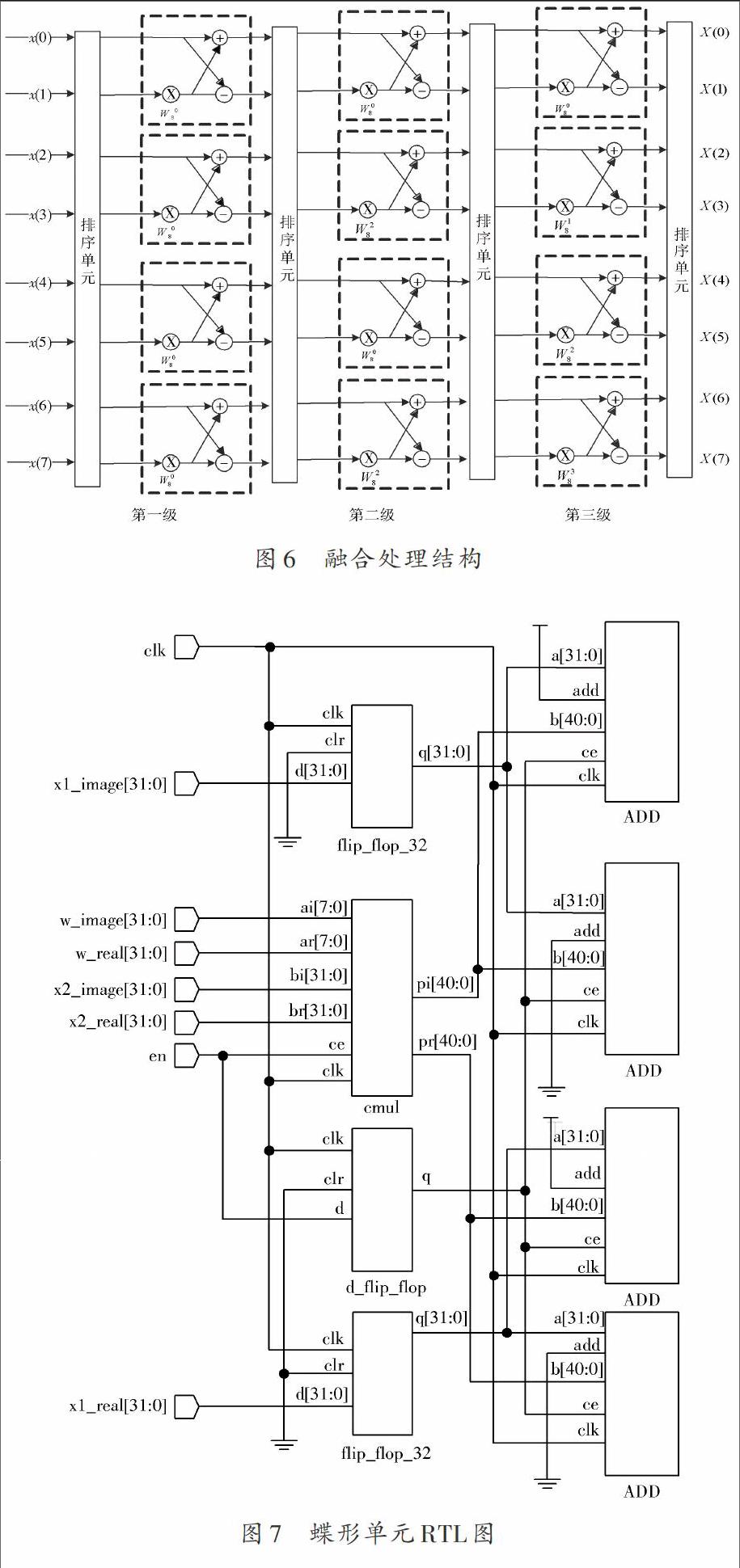

為達到4 096點FFT的效果,在乘以復(fù)數(shù)因子后,需對8個通道的輸出進行融合。圖6是融合處理的結(jié)構(gòu)圖,其本質(zhì)是8點全并行結(jié)構(gòu)的FFT。該結(jié)構(gòu)分為3級,包括12個蝶形單元和4個排序單元,節(jié)省了存儲資源。圖7是蝶形單元的RTL圖,包括4個加(減)法器,1個復(fù)數(shù)乘法器,3個觸發(fā)器。

工作時,12個蝶形單元同時運算,每個時鐘周期都會有8路輸入和8路倒序輸出,每級的8路輸出在經(jīng)過一次排序后送入下一級,避免數(shù)據(jù)的反復(fù)讀寫。排序過程會消耗一個時鐘周期,由于點數(shù)較小,在設(shè)計排序模塊時,可以直接確定上級輸出和下級輸出的對應(yīng)關(guān)系。一幀數(shù)據(jù)經(jīng)過融合模塊后就完成了4 096點FFT變換。

3.3 頻域輸出

為了得到信號的功率譜,方便后續(xù)的頻率檢測,頻域輸出模塊按倒序方式將融合后的8路輸出同時寫入RAM,然后按照自然順序從RAM中讀出,再經(jīng)過平方律檢波,即取實部和虛部的平方和并依次輸出。

4 仿真結(jié)果

設(shè)定采樣頻率[fs=2.4]GHz,借助Matlab工具產(chǎn)生中心頻率[f0=235]MHz,時長[t=1.707]μs,帶寬[B=20]MHz的線性調(diào)頻信號。

圖8是將調(diào)頻信號作為輸入激勵的仿真圖。DataPar是8通道并行輸入,為了更直觀,圖8中將時域采樣信號DataSer以串行方式輸出并以模擬格式顯示。start是系統(tǒng)的使能信號,rfd信號為高時數(shù)據(jù)緩存有效。busy信號是FFT運算的狀態(tài)標(biāo)志位,其為下降沿時一幀數(shù)據(jù)的運算結(jié)束。

在300 MHz工作時鐘下,完成每一幀數(shù)據(jù)的FFT處理需要638個周期,即2.1 μs,處理速度較快。信號op是輸出處理的狀態(tài)標(biāo)志,處理結(jié)束后op變低,done信號會維持一個周期的高電平,dout是最終的頻域輸出,freq_k是dout對應(yīng)的頻率系數(shù),圖中的波形是線性調(diào)頻信號的功率譜。

將FPGA內(nèi)8路融合后的數(shù)據(jù)導(dǎo)入Matlab,并與Matlab的仿真結(jié)果進行對比。在圖9中,頻率信息主要集中在[k=300][∶]500范圍內(nèi),圖9(a)是LFM信號在Matlab中進行FFT處理后取模的結(jié)果,圖9(b)是LFM信號經(jīng)過FPGA處理后取模的結(jié)果,兩條曲線十分接近。

由于采用定點算法[5]設(shè)計,仿真的輸入和旋轉(zhuǎn)因子都是轉(zhuǎn)換成整數(shù)后參與運算的,存在量化誤差。在多級的運算過程中,會因為數(shù)據(jù)的截尾而產(chǎn)生誤差,影響運算的精度。但由于該誤差較小,不影響后續(xù)頻譜的分析和處理。

5 結(jié) 語

本文利用FPGA實現(xiàn)多路并行結(jié)構(gòu)的FFT處理器,每通道結(jié)構(gòu)類似,容易擴展,增加級數(shù)就能實現(xiàn)更大點數(shù)的FFT,縮短了開發(fā)周期。由于其運算速度快,能實時處理高速A/D采集的中頻數(shù)據(jù),適用于寬帶信號的實時頻譜分析。

參考文獻

[1] 童慶為.基于FPGA的數(shù)字接收機高精度測頻技術(shù)[D].西安:西安電子科技大學(xué),2010.

[2] 田京京.基于FPGA的雷達信號測頻系統(tǒng)研究[D].武漢:華中科技大學(xué),2011.

[3] 霍志.一種基于FPGA的雷達數(shù)字信號處理機設(shè)計[D].長沙:國防科技大學(xué),2011.

[4] 江志紅.深入淺出數(shù)字信號處理[M].北京:北京航空航天大學(xué)出版社,2012.

[5] MEYER?BAESE U.數(shù)字信號處理的FPGA實現(xiàn)[M].北京:清華大學(xué)出版社,2011.

[6] 董暉,畢大平,王冰.寬帶數(shù)字接收機高速信號處理技術(shù)[J].現(xiàn)代防御技術(shù),2005,33(5):50?54.

[7] 王琦.基于FPGA雷達信號數(shù)字接收機的實現(xiàn)[D].南京:南京航空航天大學(xué),2008.endprint