基于FPGA的紅外遙控彩燈控制器的設計

嚴豐 陳學英

摘 要: 設計一種基于現場可編程邏輯器件FPGA的紅外遙控彩燈多模式顯示控制系統。具有成本低、性能可靠、擴展性好等優點。詳細介紹了系統的電路結構,提出一種由SC9148B紅外發射芯片及外圍電路作為發送器,HS0038B紅外一體化芯片作為接收器,FPGA作為核心控制器的紅外遙控系統的構建方法。該系統通過時序仿真與FPGA邏輯驗證,結果表明,該設計能很好地實現彩燈紅外遙控信號的解碼控制、鍵值信號存儲及譯碼、彩燈多模式顯示等功能。

關鍵詞: 紅外遙控; FPGA; 解碼; 顯示

中圖分類號: TN929.1?34 文獻標識碼: A 文章編號: 1004?373X(2015)19?0040?03

Abstract: A multi?mode coloured?lantern display control system with infrared remote control based on FPGA was designed, which has the advantages of low?cost, reliable performance and excellent scalability. The circuit structure of the system is introduced in detail. A construction method of infrared remote control system is put forward, which takes the infrared emission chip SC9148B and peripheral circuit as the transmitter, the integrated infrared chip HS0038B as the receiver, and FPGA as the core controller. This system was verified by time sequence simulation and FPGA logic validation. The actual results show that this design can realize the functions of decoding control of infrared remote control signal for the coloured lanterns, storage and decoding of the key value signal, and multi?mode coloured?lantern display.

Keywords: infrared remote control; FPGA; decoding; display

現代電子技術迅猛發展,傳統的設計方法正逐步退出歷史舞臺,基于可編程[1]邏輯器件FPGA的芯片設計技術逐步成為電子系統設計的主流。傳統的紅外遙控彩燈控制系統的信號解碼多采用單片機或ARM實現,其編碼器和解碼器的設計均為軟件方式,實際應用中容易受到外界干擾而程序跑飛,且軟件解碼為串行運算,響應速度慢,CPU資源占用多,系統可靠性較低。相比之下,基于并行處理的FPGA具有非常顯著的優勢,其速度快、系統集成度高、抗干擾能力強、工作穩定可靠、設計更改方便。本文采用市場主流的FPGA技術實現彩燈的紅外遙控,充分融合了通信技術、數字邏輯處理技術及FPGA技術[2]在工程實踐中的一體化應用。

1 系統設計原理

紅外遙控系統[3]一般主要由紅外發射器、紅外接收器和核心解碼微控制器及其外圍電路等四部分構成。本設計中,在數十米范圍內,當按鍵被按下時,紅外發射器產生與指令/按鍵對應的控制信號,并對控制信號進行識別/編碼,經過調制后,通過紅外發射管將串行數據以紅外光的形式發送出去。接收器接收來自發送器的紅外信號,并對接收到的信號進行檢波、放大、濾波解調、整形等,最后從載波上恢復出基帶信號。還原后的基帶信號被送入核心解碼控制器FPGA,轉換為相應的控制信號完成彩燈控制。

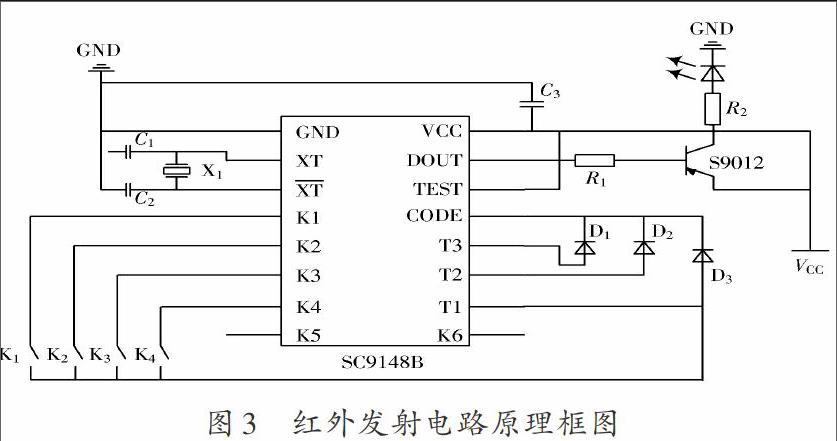

2 紅外發射電路設計

2.1 紅外通信協議

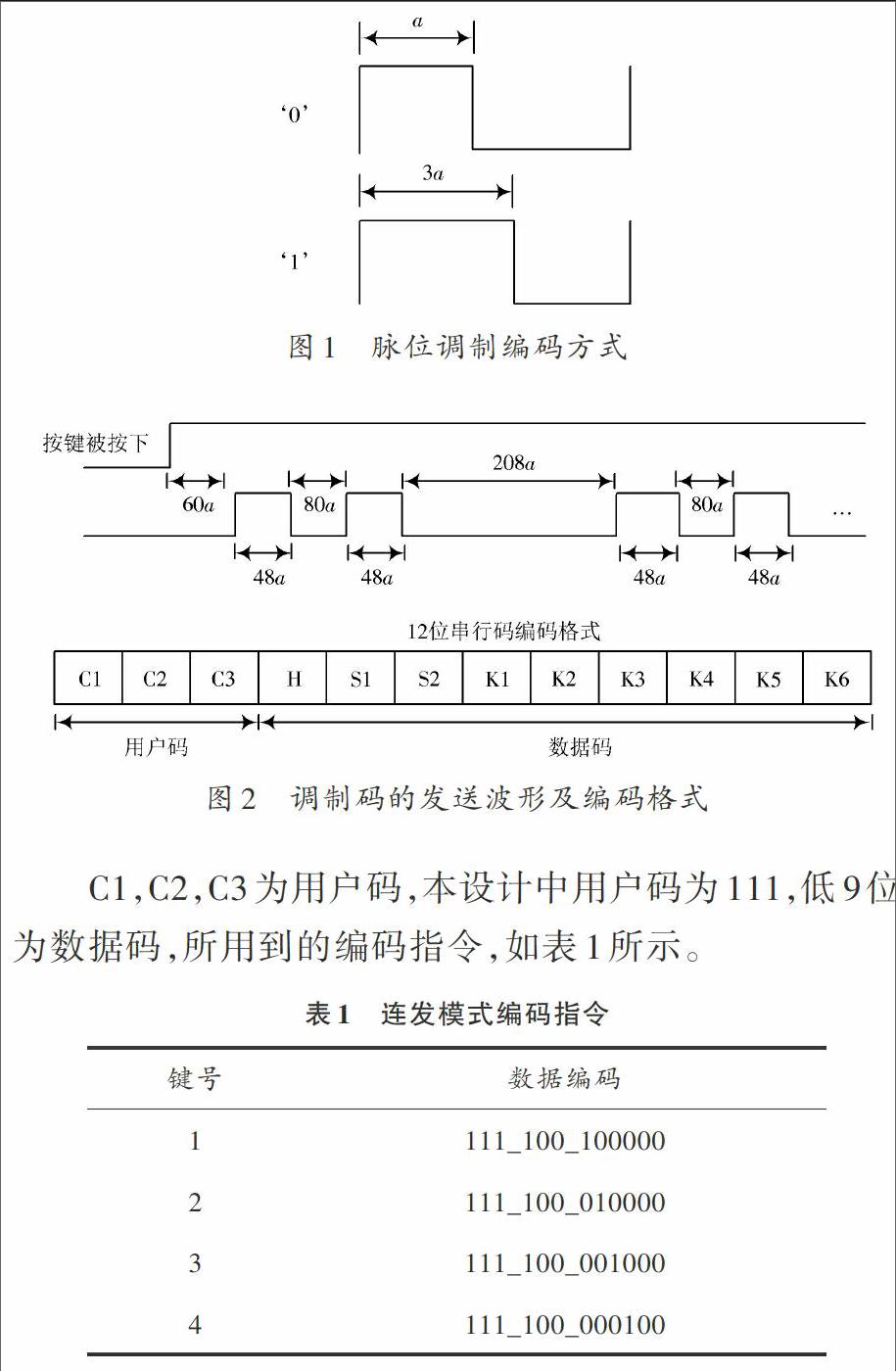

發射電路采用SC9148B為主芯片,其調制方式采用脈位調制(Pulse Position Modulation,PPM),將遙控指令編碼成脈沖序列[4]。其遙控指令的‘1是以占空比為[34]的正脈沖表示,‘0則用占空比為[14]的正脈沖表示,[a=16(38 kHz)。]

脈位調制編碼方式如圖1所示。編碼協議由12位按鍵碼組成,每一位均按照上述編碼規則所代表的‘0,‘1構成,時間長度為[12×4a=48a。]當按鍵被按下時,發射電路將以12位碼(48a)為一組發送兩次編碼,其中60a時間間隔為從按鍵按下到發送編碼的延遲時間,80a為重復發送12位碼(48a)的間隔時間,208a為重復發送兩次編碼的間隔時間。編碼指令如圖2所示格式連續發送。

電路工作原理為,當檢測到按鍵按下時,DOUT端口輸出38 kHz高頻調制信號,經紅外發射驅動電路放大后,通過紅外發射管發送出去。

3 紅外接收電路

采用通用紅外接收頭HS0038B完成對紅外光信號的接收、放大、濾波與解調[5],解調后的邏輯電平信號通過擴展I/O口送入FPGA中,由FPGA編程實現接收信號的解碼功能及相應的彩燈模式控制,從而實現彩燈多模式顯示的紅外遙控功能。設計解碼器時應該注意,HS0038B內部集成有反相器以保證接收頭有足夠的靈敏度,從載波上恢復出來的基帶信號與原調制發射前的基帶信號是反相的。

4 FPGA解碼電路與模式控制電路

FPGA解碼控制器的核心思想是: 根據本設計的紅外通信協議,12位發送數據命令中的位碼‘1或者‘0的時間長度為[4a,]本設計將在每一個[4a]時間里,對每一位碼元進行高電平脈沖采樣[6?7],為方便計算采樣脈沖個數,最大限度減少誤差,故使用采樣時鐘頻率為50 MHz。若采樣后所得的脈沖數超過10 000而少于30 000,則判斷為邏輯‘1;若所得脈沖數超過30 000而少于80 000,則判斷為邏輯‘0;若脈沖數不滿足條件,則視為無效。全局時鐘脈沖采樣數計算過程如下:endprint

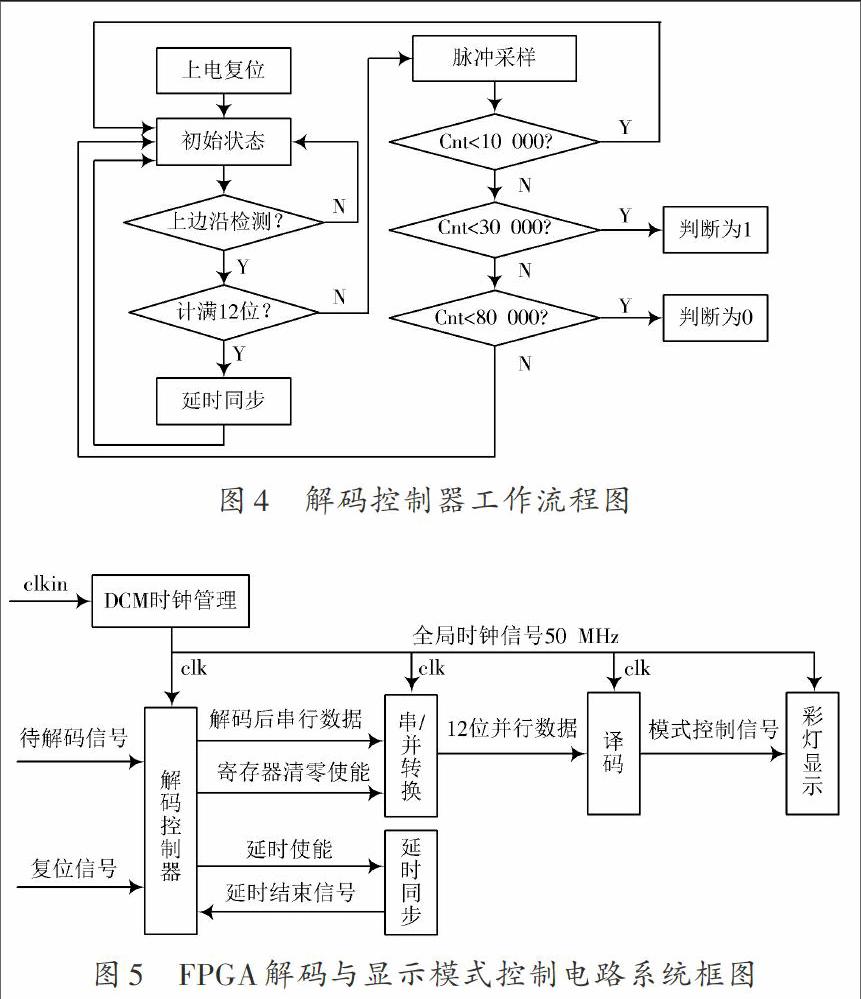

解碼控制器工作流程圖如圖4所示。系統復位進入初始狀態。首先進行輸入上邊沿檢測,若上升沿有效,表示檢測到紅外基帶信號,進而判斷是否接收到完整12位數據編碼,接收到則經延時同步(同步時間大于80a)后回到初始狀態進行下一次12位編碼數據檢測,否則進入脈沖采樣狀態。當高電平采樣脈沖數小于10 000,視為無效,回到初始狀態;脈沖數大于10 000而小于30 000,視為接收到數據編碼1;脈沖數大于30 000而小于80 000,視為接收到數據編碼0;脈沖數大于80 000,視為無效,回到初始狀態。解碼控制器輸出的串行碼逐位進入后級串/并轉換器。

解碼核心FPGA控制器采樣頻率為50 MHz。FPGA設計部分主要包括三個模塊,即時鐘管理電路(Digital Clock Manager,DCM),解碼控制電路,顯示模式控制電路。其中解碼電路包含解碼控制器,信號同步延時器,串/并轉換器三個模塊;顯示模式控制電路由譯碼器、彩燈循環顯示電路組成。FPGA邏輯設計系統框圖如圖5所示。

DCM模塊將輸入時鐘頻率轉換為50 MHz頻率的全局時鐘信號clk,給后續所有模塊提供工作時鐘。解碼控制器對輸入的基帶信號進行采樣,如圖5所示,采樣后的串行數據經過串/并轉換器[8?9]后被并行輸出,再由譯碼器轉換為與按鍵指令對應的模式控制信號,控制彩燈進行多模式顯示。為保證信號同步[10],移位寄存器的時鐘周期為[4a,]由50 MHz全局時鐘分頻得到。

經實際測試系統工作正常,性能良好,FPGA解碼模塊實現了對紅外編碼的實時解碼和顯示。收發距離約為20 m。在Modesim仿真環境下,FPGA解碼與模式控制電路系統時序仿真驗證,如圖6所示。

下面給出仿真結果的說明,為方便描述,圖6(a)中的信號從上至下用[a1,][a2,][a3,…]表示;圖6(b)中的信號從上至下用[b1,][b2,][b3,…]表示。[a1]為50 MHz時鐘信號,[a3]為仿真選用的12位串行編碼輸入信號111100100000,[a10]為12位并行碼數據;[b1]為2位模式控制信號,[b2]為彩燈循環顯示數據碼。由仿真圖可以看到,每一個[a3]信號到來時,解碼控制器準確無誤地將其并行輸出,并由譯碼器轉換為模式控制信號11,在[b1]控制模式下,彩燈依次點亮(低電平代表燈亮),對應碼型依次為01110111,10111011,11011101,11101110。

5 結 語

本文設計并實現了一種基于FPGA紅外遙控彩燈控制電路,可根據紅外發射器的編碼格式,利用FPGA可編程特性靈活地對其進行相應的解碼。本設計很好地實現了四路紅外遙控彩燈顯示模式的循環控制,用戶可根據實際需求自由改變彩燈的循環模式。相比專業芯片或者單片機軟件設計技術,FPGA邏輯器件并行處理方式使得電路響應時間更短,運算成本更小,即使在強干擾環境下也能可靠穩定的工作。同時,隨著FPGA技術的迅猛發展,其成本的迅速降低,體積的不斷減小,在未來工業、照明領域等有著廣泛的應用前景。

參考文獻

[1] 譚會生,張昌凡.EDA技術及應用[M].西安:西安電子科技大學出版社,2002.

[2] 丁躍華,陳艷峰,龍箏.紅外遙控系統的一種設計方法[J].現代電子技術,2007,30(7):50?52.

[3] 牛戴楠.基于FPGA的紅外圖像預處理系統的研究與設計[D].武漢:武漢理工大學,2008.

[4] 侯繼紅.基于CPLD/VHDL語言的紅外遙控解碼器設計[J].通信技術,2010(7):193?194.

[5] 程明陽,陳錦莉,鎖言鵬.一種基于FPGA的實時紅外圖像放大模塊[J].現代電子技術,2011,34(16):146?148.

[6] 蔡勇.基于FPGA的多功能紅外遙控器設計[D].成都:電子科技大學,2007.

[7] 劉瀟婷.基于FPGA的紅外遙控電子密碼鎖的實現[D].大連:大連海事大學,2008.

[8] 張亦華,延明.數字電路EDA入門:VHDL程序實例集[M].北京:北京郵電大學出版社,2003.

[9] 云創工作室.Verilog HDL程序設計與實踐[M].北京:人民郵電出版社,2009.

[10] 林宇航,施隆照.一種基于Verilog HDL的紅外遙控解碼電路的設計[J].科技創新導報,2012(32):24?25.endprint