超聲相控陣系統基于FPGA的PCIe總線傳輸研究*

王 沖 彭召斌 毛 捷 廉國選 李帥源

(中國科學院聲學研究所 北京 100190)

研究報告

超聲相控陣系統基于FPGA的PCIe總線傳輸研究*

王沖彭召斌?毛捷廉國選李帥源

(中國科學院聲學研究所北京100190)

針對超聲相控陣系統的高速傳輸需求,本文應用了基于FPGA的PCIe總線傳輸方案,實現了基于PCIe總線的相控陣數據DMA(直接存儲器讀寫)上傳、控制命令下傳、發送數據緩存及驅動和上位機測試程序設計。通過實驗測試了PCIe總線的DMA傳輸速率,可達6.5 Gbit/s,并成功將該方案應用于64通道超聲相控陣檢測系統中,實現了超聲相控陣系統的PCIe總線數據傳輸。

超聲相控陣檢測,PCIe,FPGA,DMA傳輸

1 引言

超聲相控陣技術是近年來發展最快的無損檢測方法,被廣泛應用于高速鐵路、航空航天、油氣運輸等工業領域[1-4]。傳統超聲相控陣系統的數據傳輸方式以千兆網、USB2.0為主,隨著全波形存儲、快速位置掃查和多角度成像等檢測技術的應用,傳輸帶寬已無法滿足檢測需求。

以蜂窩復合材料的快速、多角度C掃描為例,現場要求掃查速度為200 mm/s,掃查精度為0.2 mm,若每個位置進行30個角度的掃描,每個角度采集4 K個點作全數據存儲,每個采樣點16 bit位寬,則數據采集速率達1.92 Gb/s,千兆網、USB2.0等傳統總線方式顯然無法滿足其帶寬要求。具有更高帶寬的總線傳輸方案成為快速相控陣檢測系統的迫切需求。

快速外部設備互聯(PCIe)是英特爾提出的第3代IO總線技術,可實現設備間基于數據包的高速點對點串行通訊[5]。以PCIe 1.0協議為例,4x鏈路的單向數據速率可達8 Gb/s,為高帶寬的數據傳輸提供了可靠解決方案[6]。

在相控陣系統中,硬件系統多以FPGA為控制核心,相比于千兆網和USB2.0總線,基于FPGA(Field-programmable gate array)的PCIe總線在實現上主要有以下難點:

(1)PCIe總線對FPGA的時鐘管理、邏輯資源、時序控制等有較高的要求;

(2)PCIe總線通過DMA(Direct memory access)實現高速數據上傳,控制協議復雜;

(3)PCIe總線在DMA傳輸的間隙,需要設計安全的數據緩沖池,以保證DMA速率的前提下避免數據溢出。

針對上述難點,本文應用基于Xilinx FPGA端點硬核的PCIe總線傳輸方式,根據相控陣系統總線傳輸的特點,進行了基于PCIe總線的相控陣數據DMA上傳、控制命令下傳、數據發送緩存邏輯及驅動和上位機測試程序設計。通過實驗測試了PCIe總線的DMA傳輸速率,可達6.5 Gbit/s,并成功將該總線傳輸方案應用于64通道超聲相控陣檢測系統中。

2 基于FPGA的PCIe總線傳輸總體設計

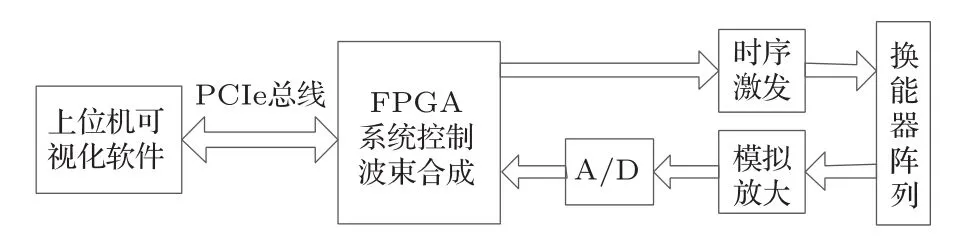

如圖1所示,超聲相控陣檢測系統包括以FPGA為核心的底層硬件、驅動和上位機軟件組成。硬件負責實現換能器陣列的時序激發、模擬接收放大、A/D轉換和波束合成;上位機軟件完成控制參數的計算和檢測數據的成像。

圖1 超聲相控陣系統框架Fig.1 The framework of phased array ultrasonic system

在本系統中,PCIe總線主要完成上位機控制參數的下傳和FPGA波束合成后數據的上傳。其參數和數據的傳輸具有以下特點:

(1)PCIe下傳參數時數據量小,實時性要求不高;

(2)PCIe上傳數據時數據量大,實時性要求較高;

(3)波束合成與PCIe總線間需要較大的數據緩沖池,以緩存突發的上傳數據。

針對以上特點,本文進行了基于FPGA的PCIe總線DMA數據上傳控制邏輯,控制命令下傳邏輯,數據發送緩存邏輯,驅動程序和上位機測試程序設計。

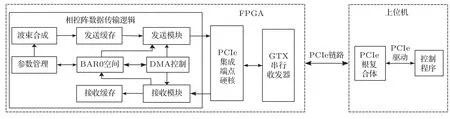

設計框架如圖2所示。

圖2 基于Xilinx FPGA的PCIe總線設計框架Fig.2 The design framework of PCIe bus based on Xilinx FPGA

3 基于PCIe總線的相控陣數據傳輸邏輯設計

3.1基于DMA的數據上傳邏輯

DMA傳輸不占用CPU讀寫周期且傳輸速率高[7]。PCIe的DMA操作將數據封裝在事務層包(TLP)中傳輸,啟動、中斷、完成等狀態存放于BAR0(Base address register)空間的DMA控制狀態寄存器中。

在相控陣檢測系統中,每一次激發都會采集一定量的回波數據進入發送緩存。有待發數據時,發送緩存給DMA寫邏輯使能信號,在上位機啟動和IP核準備好的情況下,通知DMA寫邏輯將數據填充在存儲器寫請求事務包中送入IP核,由IP核完成鏈路層和物理層的發送。

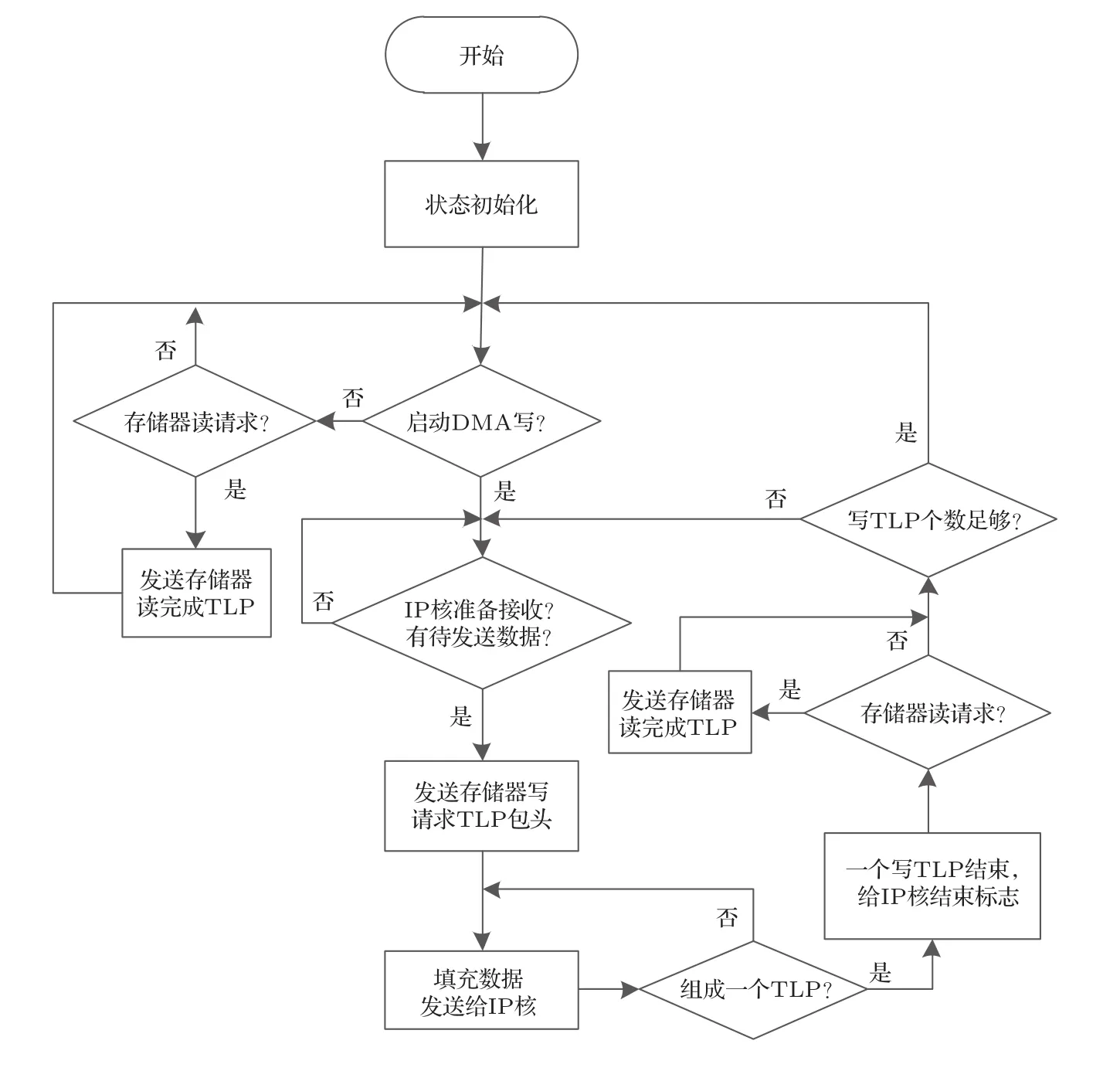

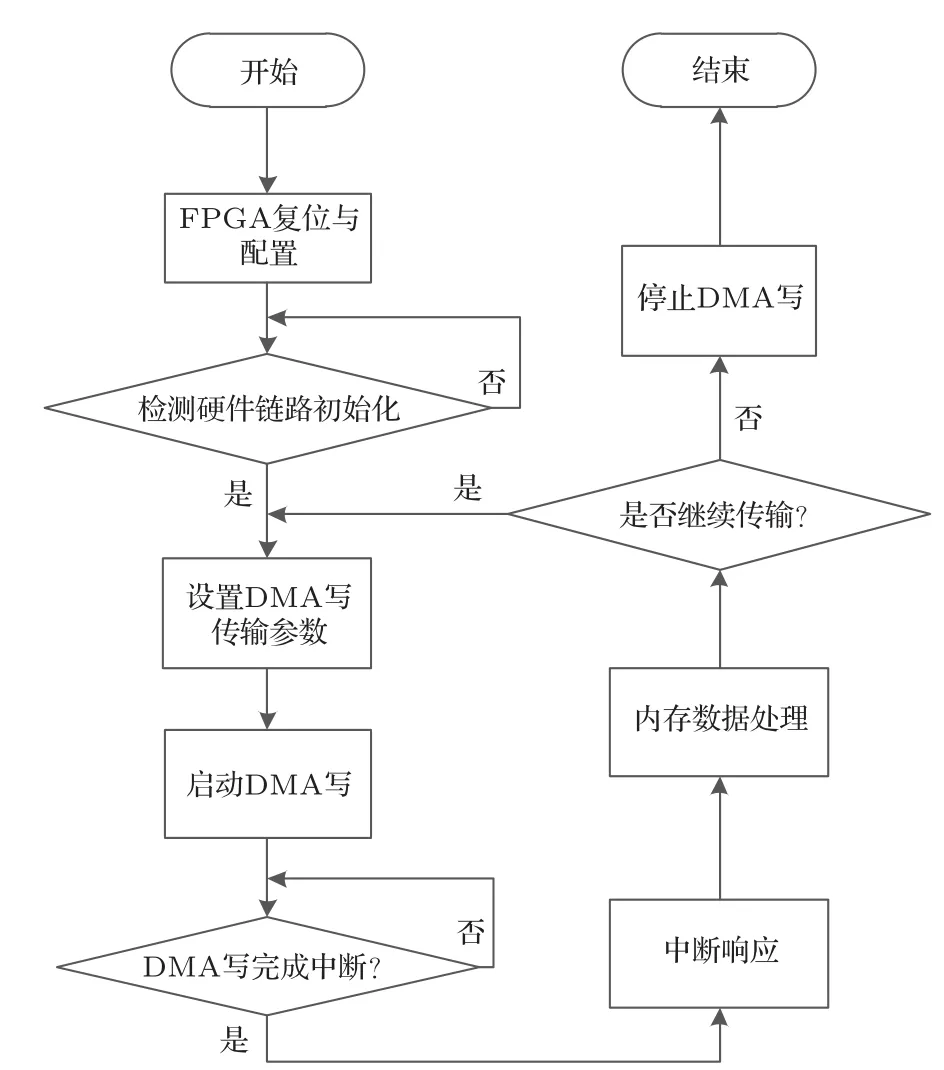

基于DMA的數據上傳邏輯需要上位機與FPGA邏輯協調進行,是本文設計的重點。DMA寫邏輯實現過程如圖3所示,每一次DMA寫的實現過程為

(1)上位機配置傳輸參數,包括目的地址、本次DMA傳輸的數據長度;

(2)上位機啟動DMA,DMA寫邏輯等待發送緩存使能后開始傳輸;

(3)DMA寫邏輯檢測到傳輸數據量等于上位機設定的數據長度時,停止DMA寫,以中斷方式通知上位機,并不再從發送緩存讀取數據;

(4)上位機在收到寫完成中斷后,進入中斷響應函數;

(5)中斷響應完成后,根據狀態位判斷是否需要進行下一次DMA傳輸。

相控陣數據傳輸邏輯在DMA寫的同時,還要響應上位機的讀請求事務包。上位機通過該事務包讀取DMA控制狀態寄存器,了解DMA的工作狀態。本文相控陣數據傳輸邏輯在收到讀請求事務包時,會在DMA寫的間隙將目標寄存器中的值填入讀完成事務包,發送給上位機。

圖3 DMA寫邏輯實現過程Fig.3 The design of DMA writing logic

3.2基于BAR0空間讀寫的控制命令下傳

BAR0是PCIe設備的32 bit寄存器空間,包含了DMA控制狀態寄存器和用戶自定義寄存器,上位機通過對BAR0空間的訪問,控制PCIe設備的數據傳輸。

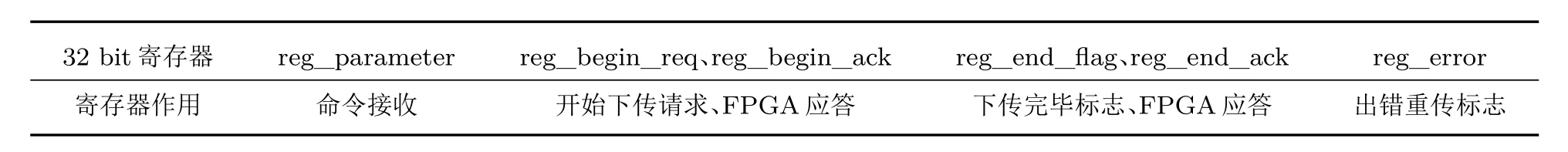

在數據傳輸過程中需要進行控制命令的緩存、管理和傳輸狀態的握手。如表1所示,本文在BAR0空間開設了命令接收和握手寄存器,利用FPGA片內FIFO作命令參數緩存,并設計了傳控的握手協議。其中:

(1)控制命令寄存器reg_parameter,上位機調用存儲器寫函數,將控制命令參數寫入該寄存器,FPGA將該寄存器的值緩存入FIFO中;

(2)握手寄存器reg_begin_req、reg_begin_ack,用于上位機與FPGA之間在傳輸開始時的請求和應答握手;

(3)握手寄存器reg_end_flag、reg_end_ack,用于上位機與FPGA之間在傳輸結束后的完畢標志、應答握手;

(4)出錯重傳標志寄存器reg_error,用于FPGA對每一次傳輸結果的校驗,并將校驗結果放入reg_error中,上位機根據reg_error的值判斷本次傳輸是否出錯及重傳。

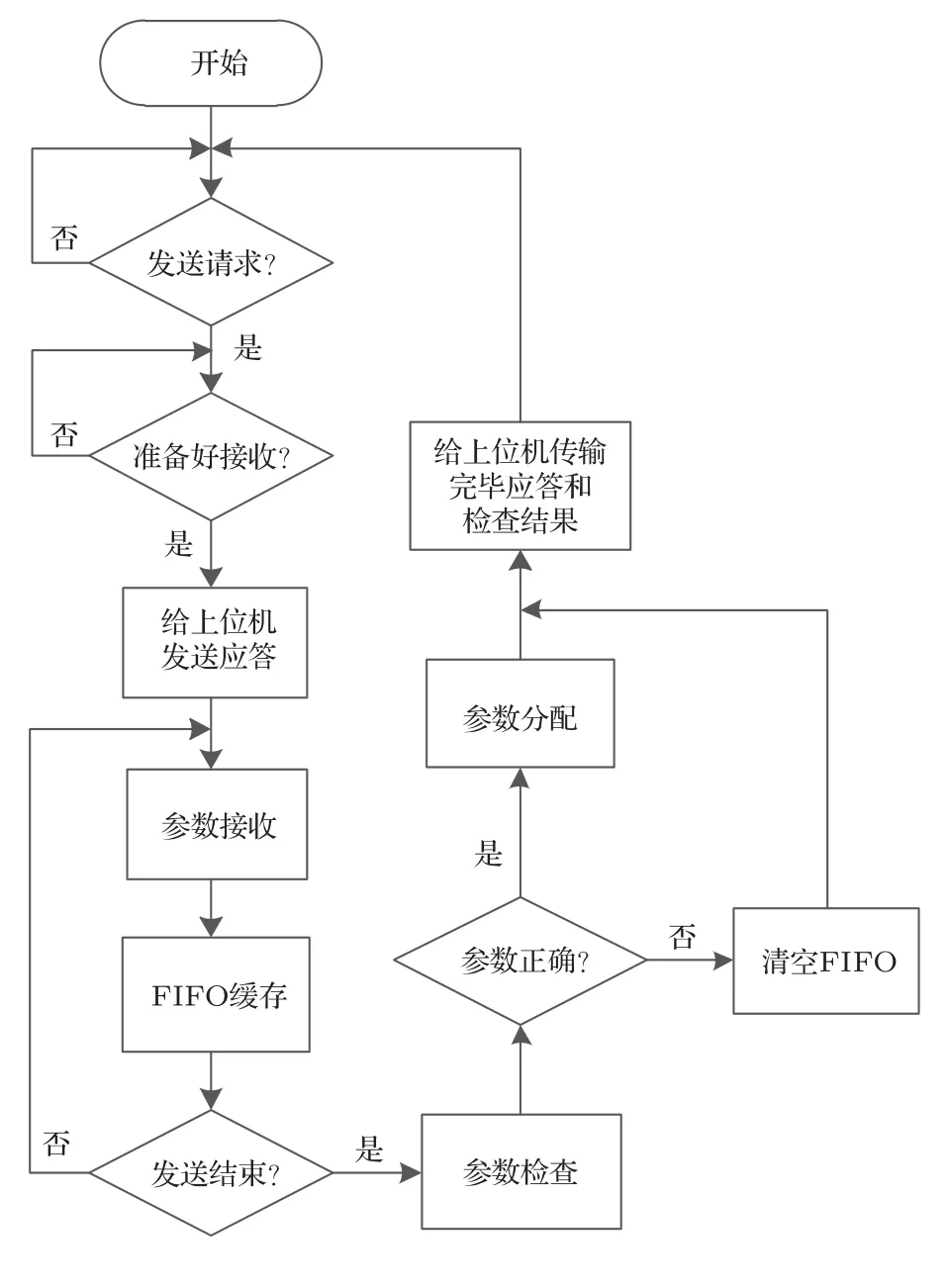

基于BAR0讀寫的參數下傳邏輯實現過程如圖4所示,上位機在控制命令下傳開始和完畢時均與FPGA進行握手,握手成功后進行發送和允許下一次傳輸;同時FPGA根據命令定義對每一次傳輸進行校驗,并將校驗結果通知上位機。

表1 BAR0空間控制命令下傳寄存Table 1 The register table of controlling parameters in BAR0

圖4 基于BAR0讀寫的參數下傳實現過程Fig.4 The design of parameters sending logic based on BAR0 access

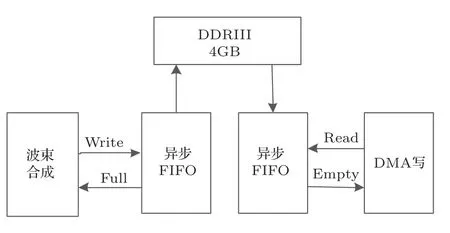

4 基于DDRIII的發送緩存邏輯設計

超聲相控陣系統的數據傳輸有突發性強、數據量大的特點,而PCIe總線在一次DMA寫完成后,需要等待上位機的配置和啟動,如果發送緩存容量過小,極容易造成相鄰兩次DMA寫之間的突發數據丟失。因此本文設計了容量為4 GB的片外DDRIII緩存,如圖5所示,結合片內異步FIFO,作為相控陣邏輯中波束合成與PCIe總線的數據緩沖池,其容量完全滿足相控陣檢測中的突發緩存要求。

圖5 發送緩存設計框架Fig.5 The framework of DDRIII buffer logic

5 驅動及上位機程序設計

硬件系統與上位機的PCIe總線傳輸需要設備驅動和控制程序。本文PCIe設備驅動在WinDriver平臺下開發;PCIe傳輸控制程序在Qt環境下編寫。

5.1WinDriver驅動開發流程

WinDriver是針對WDM模型驅動程序的主流開發工具之一。使用WinDriver的用戶模式開發驅動,可移植性較好,且不需要掌握操作系統內核知識,極大地簡化了驅動開發的難度。Windows 7系統下的開發流程包括以下步驟:

(1)設置硬件環境,上位機查找到PCIe設備,提示安裝驅動;

(2)選擇PCIe設備并建立工程;

(3)生成和安裝INF文件;

(4)生成驅動代碼。

5.2PCIe數據傳輸控制程序

使用WinDriver完成驅動開發后,本文在熟悉WinDriver提供的底層API函數的功能和使用方法的基礎上,設計了以下主要函數,完成底層API的調用和對PCIe設備的操作。

(1)OpenDevice()和StopDMA()實現PCIe設備的打開和關閉;

圖6 上位機PCIe控制程序流程Fig.6 The flow of PCIe controlling program on PC

(2)WriteBAR0()和ReadBAR0()實現對BAR0空間寄存器的訪問;

(3)DMAWriteMenAlloc()實現DMA寫操作時上位機對內存的申請和操作;

(4)IntDealFunction()實現DMA讀寫完成中斷處理。

控制程序工作流程如圖6所示,上位機啟動DMA傳輸后,等待DMA寫完成中斷,在中斷響應中完成內存數據的處理,并根據成像需要開啟下一次DMA傳輸。

6 PCIe總線驗證測試

完成基于PCIe總線的相控陣數據傳輸邏輯設計、驅動及上位機控制程序設計后,本文從DMA寫邏輯正確性、上位機接收數據正確性和接口速率三個方面對PCIe總線進行了驗證和測試。本次測試的PCIe鏈路選擇4x,鏈路位寬為64 bit,每個事務層包的最大鏈路負載為128 B。

6.1DMA寫邏輯正確性驗證

使用Xilinx在線邏輯分析工具Chipscope檢測DMA寫邏輯與IP核之間的接口時序,為方便觀測,數據源采用32 bit的遞增數據,每兩個一組寫入發送緩存中。

圖7中fifo_q_PCIe_us即為DMA寫邏輯從異步FIFO讀出的64 bit數據,其高低32 bit分別從1和0開始作步進為2的遞增運算。

如圖7所示,IP核準備好接收數據時(tready_thrtl為高電平),DMA寫邏輯按事務層包格式在s_axis_tx_tdata_r上輸出包頭和數據,同時給出標志信號s_axis_tx_tvalid_r。前96 bit為即TLP包頭,包頭的后32 bit 0x08F91000為目的地址,緊跟的就是數據。事務包中的每個32 bit數據按照低字節在前高字節在后的順序排列,字節內位序不變,這樣保證數據在上位機內存中按字節先后順序排列。

如圖8所示,在一個TLP傳完時,DMA寫邏輯給s_axis_tx_tlast_r標志,向IP核表明當前是最后一數據。下一個周期便是新的事物包包頭,其目的地址為0x08F91080,增加了128 B,表示上一個事務包共傳輸了128 B數據,與設定的最大鏈路負載參數相符。

圖7 DMA寫邏輯時序圖_1Fig.7 The timing sequence 1 of DMA writing logic

圖8 DMA寫邏輯時序圖_2Fig.8 The timing sequence 2 of DMA writing logic

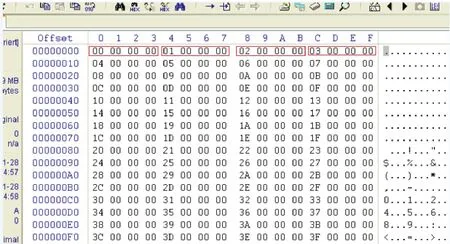

6.2上位機接收數據正確性驗證

將DMA傳輸至上位機的數據使用winhex軟件查看,如圖9所示,每個32 bit數據按照字節從低到高的順序排列正確。

上述DMA寫邏輯時序和上位機數據接收的驗證結果表明,本文PCIe接口的DMA傳輸邏輯和控制程序均可正常工作。

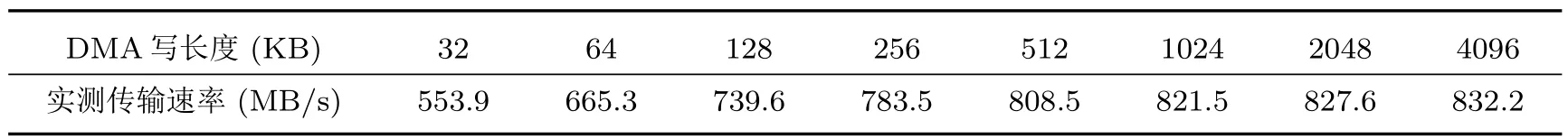

6.3PCIe接口速率測試

PCIe 4x下的最大理論速率為8 Gb/s[8-10],為檢測PCIe接口的傳輸速率,本文使用控制程序分別測試了不同DMA寫長度下的傳輸速率,如表2所示。

圖9 上位機接收數據Fig.9 The receiving data on PC

表2 不同DMA寫長度下的PCIe傳輸速率對比Table 2 The speed of PCIe bus with different DMA writing size

如表2所示,本文的PCIe接口的實際傳輸速率可達832 MB/s以上,即6.5 Gb/s,滿足相控陣檢測系統的帶寬要求。

從表2也可以看出,隨著DMA寫長度的增大,傳輸速率也會增加。原因是增加了每次DMA寫操作中傳輸的有效字節數,減少了存儲器讀寫操作的總次數,從而減少了傳輸中的固定開銷,提高了總體的傳輸速度。但在相控陣檢測系統中,DMA寫長度的增大會使成像軟件的等待時間增大,不利于整體檢測平臺的運行,因此還需要根據實際的相控陣檢測需要,合理地選擇DMA寫長度參數。

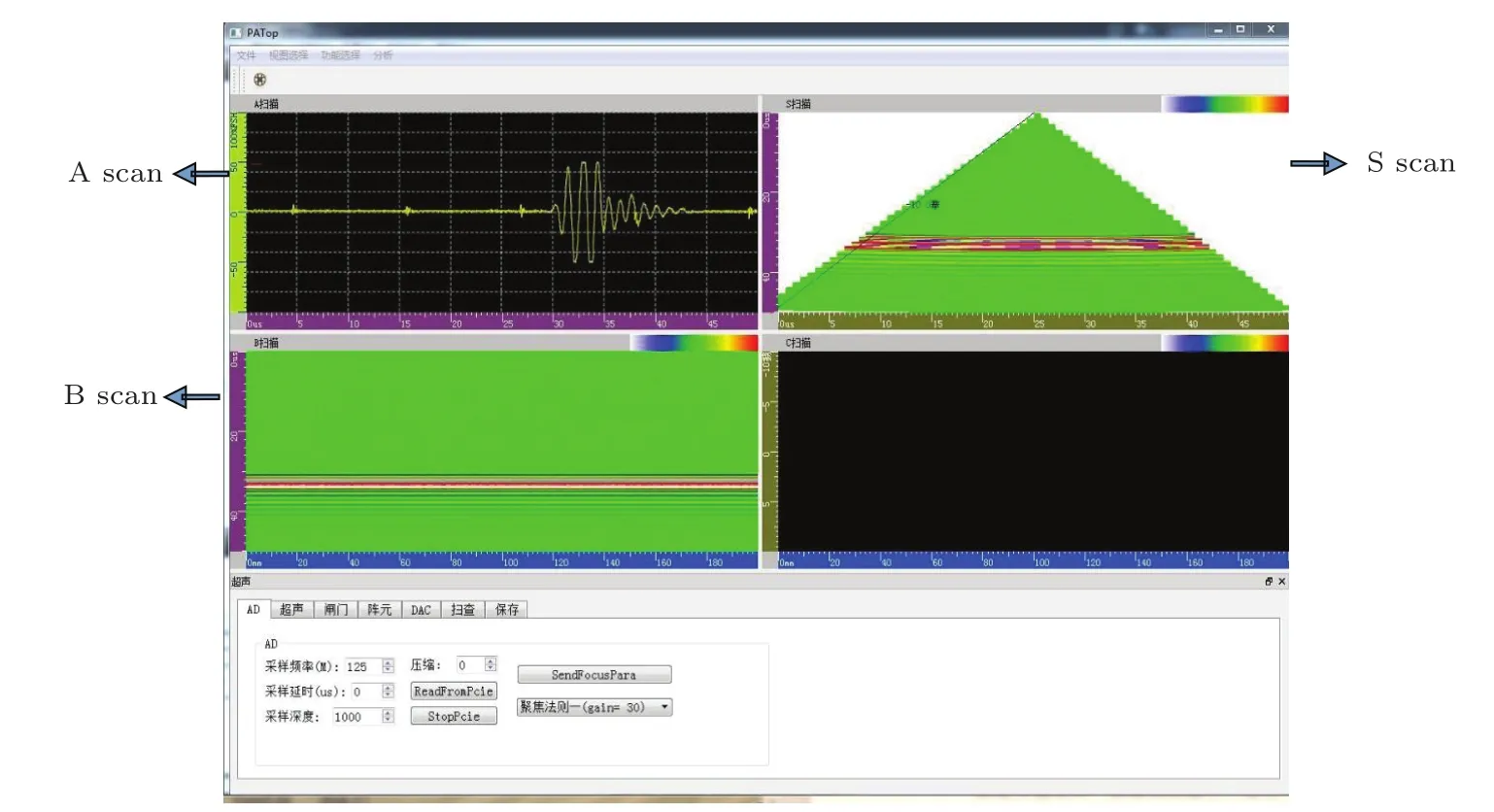

目前,該項技術已成功應用于自研的64通道超聲相控陣檢測系統,實現了控制命令的PCIe下傳和波束合成數據的DMA上傳,并形成了實時A、B與S掃描圖像(如圖10所示)。

圖10 系統A、B、S掃描圖像Fig.10 The A scan,B scan,S scan of phased array ultrasonic system

7 結論

本文首先分析了超聲相控陣檢測中的高速傳輸需求,應用了基于Xilinx FPGA端點硬核的PCIe總線傳輸方案。相比于使用PCIe橋接芯片,基于Xilinx FPGA端點硬核的PCIe總線傳輸具有配置靈活、可靠性高等優勢,可以簡化板級設計,使用戶專注于PCIe事務層開發,縮短系統開發周期。本文通過數據傳輸邏輯、數據發送緩存邏輯和驅動、上位機程序設計,實現了控制命令的PCIe下傳和波束合成數據的DMA上傳,并成功應用于64通道超聲相控陣檢測系統中。測試結果表明,4x PCIe接口的DMA寫速率高達6.5 Gb/s,完全滿足超聲相控陣系統的高速總線傳輸需求,該技術為高性能超聲相控陣設備的高速實時數據傳輸的提供了有效保證。

[1]MCNAB A,CAMPBELL M J.Ultrasonic phased arrays for nondestructive testing[J].NDT&E.,1987,(6):333-337.

[2]ZHANG B X,LIU D D,SHI F F.Ultrasonic focusing and scanning with multiple waves[J].Chin.Phys.B,2013,22(1):014302.

[3]孔超,冀映輝,蔡煒,等.超聲相控陣控制、采集與全并行處理系統設計[J].應用聲學,2011,30(2):105-111.

KONG Chao,JI Yinghui,CAI Wei,et al.The design of control-acquisition and fully parallel processing phased array ultrasonic system[J].J.Appl.Acoust.,2011,30(2):105-111.

[4]彭小沖,費躍農.相控陣超聲接收動態聚焦算法及其物理實現[J].應用聲學,2014,33(5):453-461.

PENG Xiaochong,FEI Yuenong.Receiving dynamic depth focusing algorithm of phased array ultrasound imaging and its physical implementation scheme[J].J. Appl.Acoust.,2014,33(5):453-461.

[5]KAVIANIPOUR H,BOHM C.A high-reliability PCIe communicationsystemforsmallFPGAs.nuclear[C]. Science Symposium and Medical Imaging Conference(NSS/MIC),IEEE,2013.

[6]KAVIANIPOUR H,MUSCHTER S,BOHM C.High performance FPGA based DMA interface for PCIe[C].2012 18th IEEE-NPSS Real Time Conf.,2012.

[7]KAVIANIPOUR H,BOHM C.High performance FPGA-based scatter/gather DMA Interface for PCIe[C].Nu-clear Science Symposium and Medical Imaging Conference(NSS/MIC),IEEE,2012.

[8]李木國,黃影,劉于之.基于PCIe總線的高速數據采集卡設計與實現[J].測控技術,2013,32(7):19-22.

LI Muguo,HUANG Ying,LIU Yuzhi.Design and implementation of a high-speed data acquisition card based on PCIe bus[J].Measurement&Control Technology,2013, 32(7):19-22.

[9]Xilinx Inc:Virtex-6 FPGA integrated block for PCI express[EB/OL].[2015-02-10].http://china.xilinx.com/ support/documentation/ip_documentation/v6_pcie/ v2_5/ug671_V6_IntBlock_PCIe.pdf.

[10]PCI Express Base Specification 2.0[EB/OL].[2015-02-10]. https://www.pcisig.com/specifications.

Research of PCIe bus based on FPGA in ultrasonic phased array system

WANG ChongPENG ZhaobinMAO JieLIAN GuoxuanLI Shuaiyuan

(Institute of Acoustics,Chinese Academy of Sciences,Beijing 100190,China)

PCIe bus solution based on Xilinx FPGA is developed for high-speed data transmission in ultrasonic phased array system.In this solution,DMA(Direct memory access)data up-transfer,control instruction downtransfer,data buffer,PCIe driver and test demo are designed in this paper based on PCIe bus.Test result shows that DMA data up-transfer speed can reach up to 6.5 Gb/s,which satisfies the requirement of high-speed data transmission in ultrasonic phased array system.Also,this solution is successfully adopted in the 64-channel ultrasonic phased array system.

Ultrasonic phased array testing,PCIe,Field-programmable gate array,Direct memory access

TB559

A

1000-310X(2015)05-0377-08

10.11684/j.issn.1000-310X.2015.05.001

2015-02-12收稿;2015-04-25定稿

*中國科學院科研裝備研制項目(Y329011331)

王沖(1990-),男,山東淄博人,碩士研究生,研究方向:信號與信息處理。?

E-mail:pengzhaobin@mail.ioa.ac.cn