SoC多語言協(xié)同驗(yàn)證平臺(tái)技術(shù)研究

王紀(jì),馮志華

(中國航天科工集團(tuán)第二研究院706所,北京100854)

SoC多語言協(xié)同驗(yàn)證平臺(tái)技術(shù)研究

王紀(jì),馮志華

(中國航天科工集團(tuán)第二研究院706所,北京100854)

SoC基于IP設(shè)計(jì)的特點(diǎn)使驗(yàn)證項(xiàng)目中多語言VIP(Verification IP)協(xié)同驗(yàn)證的需求不斷增加,給驗(yàn)證工作帶來了很大的挑戰(zhàn)。為了解決多語言VIP在SoC驗(yàn)證環(huán)境靈活重用的問題。提出了一種基于開放的多語言構(gòu)架庫的解決方案,詳述了多語言協(xié)同驗(yàn)證技術(shù)的原理以及驗(yàn)證平臺(tái)的搭建方法,并通過實(shí)例驗(yàn)證了所提方案的有效性和靈活性。

片上系統(tǒng);驗(yàn)證知識(shí)產(chǎn)權(quán)核;多語言協(xié)同驗(yàn)證;重用

隨著高級(jí)驗(yàn)證方法學(xué)越來越多的成功應(yīng)用于實(shí)際的SoC驗(yàn)證項(xiàng)目中[1],產(chǎn)生了大量由不同語言、不同驗(yàn)證方法學(xué)編寫的可重用組件;而且由于IP來自不同的EDA廠商,相應(yīng)的驗(yàn)證IP也是由不同的廠商提供。僅在SoC驗(yàn)證環(huán)境中重用由同一種語言和驗(yàn)證方法學(xué)實(shí)現(xiàn)的組件或VIP,已經(jīng)不能滿足日益增長的SoC驗(yàn)證需求[2]。如何靈活的重用多語言驗(yàn)證組件、搭建SoC多語言協(xié)同驗(yàn)證平臺(tái)已然成為熱點(diǎn)。

現(xiàn)有的多語言的解決方案分為兩種:一種是基于SystemVerilog DPI(Direct Programming Interface)直接引用外部語言程序的方法[3];另一種是使用EDA廠商提供的多語言庫的方法[4]。前者驗(yàn)證平臺(tái)無法對(duì)外部語言程序?qū)崿F(xiàn)配置,靈活性差[5];后者則存在當(dāng)前使用的多語言庫針對(duì)語言種類單一,不能跨仿真器平臺(tái)的缺點(diǎn)[6]。

文中針對(duì)當(dāng)前多語言協(xié)同驗(yàn)證解決方案存在的不靈活,支持的語言種類單一等特點(diǎn),基于一種新的解決多語言問題的開源庫——UVM-ML OA(Universal Verification Methodology-Multi-Language Open Architecture library),詳述了多語言協(xié)同驗(yàn)證的原理,并描述了搭建SoC多語言協(xié)同驗(yàn)證平臺(tái)的過程,以一個(gè)具體的實(shí)例驗(yàn)證了這種方法在靈活性和可重用方面的優(yōu)點(diǎn)。

1 UVM-MLOA簡介

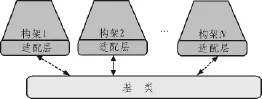

UVM-ML OA庫是由AMD和Cadence公司聯(lián)合推出[7],致力于解決多語言驗(yàn)證組件的快速整合與重用。它提供的一些方法和工具能夠?qū)⒉煌Z言的驗(yàn)證組件整合到一個(gè)大的驗(yàn)證環(huán)境中。抽象驗(yàn)證組件具體實(shí)現(xiàn)的語言與方法學(xué),使多語言組件在同一驗(yàn)證環(huán)境實(shí)現(xiàn)無差別的通信和配置。UVMML OA的基本結(jié)構(gòu)如圖1所示,它由開源的基類和多種構(gòu)架的多語言適配層組成。例如,SV(SystemVerilog)適配層,SC(SystemC)適配層等。

圖1 UVM-ML OA基本結(jié)構(gòu)Fig.1UVM-ML OA basic structure

構(gòu)架是指由同一種語言或驗(yàn)證方法學(xué)實(shí)現(xiàn)的驗(yàn)證組件的集合。構(gòu)架可能由硬件驗(yàn)證語言(SystemVerilog)、建模語言(SystemC)或一般的編程語言(C/C++)實(shí)現(xiàn)。不同的構(gòu)架也可以由同一語言實(shí)現(xiàn):例如,UVM和VMM都是由SystemVerilog編寫。

基類是兩個(gè)或更多構(gòu)架的連接路由,是整個(gè)星形拓?fù)浣Y(jié)構(gòu)的中心點(diǎn)。提供不同組件間控制和數(shù)據(jù)通訊的API(Application Programming Interface)。這種CS(Client-Server)結(jié)構(gòu)能夠忽略具體的方法學(xué)和語言的實(shí)現(xiàn)細(xì)節(jié),協(xié)同不同構(gòu)架間的工作。

適配層是基類和構(gòu)架的連接層,提供與其對(duì)應(yīng)構(gòu)架連接到基類所必須的的API接口。

UVM-ML OA擁有包括多構(gòu)架結(jié)構(gòu)、事務(wù)級(jí)通信、分階段機(jī)制、跨構(gòu)架配置機(jī)制等特征,使其能夠很好的解決實(shí)際應(yīng)用中多語言的難題,靈活的搭建多語言協(xié)同驗(yàn)證平臺(tái)[8]。

2 多語言協(xié)同驗(yàn)證平臺(tái)原理

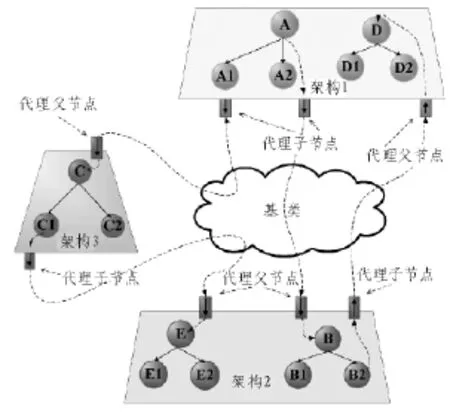

多語言協(xié)同驗(yàn)證平臺(tái)由多種構(gòu)架的VIP組成。驗(yàn)證平臺(tái)可能有一個(gè)或很多邏輯頂層,每一個(gè)頂層都是由不同構(gòu)架子組件組成的樹形結(jié)構(gòu)。每一棵樹都可能包含其他構(gòu)架的子樹。如圖2所示,構(gòu)架1的A組件是整個(gè)多語言協(xié)同驗(yàn)證平臺(tái)的頂層。它除了實(shí)例化了A1、A2兩個(gè)同一構(gòu)架下的子組件外,還例化了一個(gè)構(gòu)架2下的子組件B。

圖2 不同構(gòu)架下的統(tǒng)一樹形結(jié)構(gòu)Fig.2Unified hierarchy in different frameworks

搭建多語言協(xié)同驗(yàn)證平臺(tái)首先要將不同構(gòu)架的子組件實(shí)例到驗(yàn)證平臺(tái)中,使整個(gè)驗(yàn)證平臺(tái)形成一個(gè)統(tǒng)一的樹形結(jié)構(gòu)。結(jié)構(gòu)建立后,為了實(shí)現(xiàn)整個(gè)平臺(tái)的數(shù)據(jù)流動(dòng),不同構(gòu)架的組件需要建立事務(wù)級(jí)的通信。最后建立起跨構(gòu)架的可配置機(jī)制,增強(qiáng)多語言協(xié)同驗(yàn)證平臺(tái)的靈活性。

2.1多構(gòu)架組件的整合

UVM-ML OA通過基類來實(shí)現(xiàn)父組件和外部子組件的連接,確保平臺(tái)間數(shù)據(jù)和控制請(qǐng)求被正確傳遞。每一個(gè)父組件通過各自構(gòu)架適配層的API與基類的API相連;然后基類再與子組件的相應(yīng)構(gòu)架適配層的API相連。這樣,經(jīng)由代理父節(jié)點(diǎn)和代理子節(jié)點(diǎn)建立起了不同構(gòu)架父組件和子組件的抽象連接。如圖3所示,還以構(gòu)架1的A組件為例:在構(gòu)架1的范疇內(nèi),A正常的實(shí)例化了A1、A2兩個(gè)組件;而屬于構(gòu)架2的B子組件則如圖中虛線所示,經(jīng)由各自構(gòu)架的適配層和基類來完成在A中的實(shí)例化,完成多構(gòu)架組件的整合。

圖3 組件的跨構(gòu)架連接Fig.3Parent child relationship maintained through the backplane

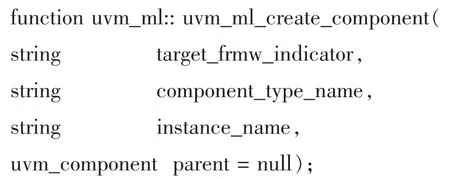

要實(shí)例化一個(gè)不同構(gòu)架的子組件,有必要正確的指定外部組件的構(gòu)架類型和名稱,以及實(shí)例化后的實(shí)例化名。以SV適配層的API實(shí)例化外部構(gòu)架組件為例:使用下面的方法在SV環(huán)境中實(shí)例化其他構(gòu)架的組件。

其中,參數(shù)target_frmw_indicator是待實(shí)例化組件的構(gòu)架類型;參數(shù)component_type_name是待實(shí)例化組件的頂層模塊名;參數(shù)instance_name為組件的實(shí)例化名;參數(shù)parent指定當(dāng)前組件的父節(jié)點(diǎn)。

2.2事物級(jí)連接的建立

多構(gòu)架組件的通訊基于TLM(Transaction Level Modeling)接口[9],UVM-ML OA的基類提供了指定的多語言接口庫,它維護(hù)著平臺(tái)運(yùn)行時(shí)事物級(jí)交易所需的必要信息。多語言平臺(tái)中的TLM接口要跨構(gòu)架實(shí)現(xiàn)通信,有兩個(gè)步驟:首先TLM的端口或套接字必須在基類中注冊(cè);注冊(cè)后將接口綁定,不同架構(gòu)組件間便可以經(jīng)由相應(yīng)的適配層和基類實(shí)現(xiàn)數(shù)據(jù)交易。

2.2.1注冊(cè)

注冊(cè)的多語言端口會(huì)在相應(yīng)的適配層中產(chǎn)生與基類進(jìn)行數(shù)據(jù)流動(dòng)的通道,適配層提供了相應(yīng)的底層結(jié)構(gòu)支持不同構(gòu)架與基類的連接。還以SystemVerilog構(gòu)架的API注冊(cè)TLM1端口和TLM2套接字為例。使用SV適配層的register方法實(shí)現(xiàn)注冊(cè)功能,register方法定義為:

static function void register(uvm_port_base#(uvm_tlm_if#(TRAN_T,P))sckt);

其中參數(shù)sckt代表被注冊(cè)接口的全路徑名稱。

2.2.2綁定

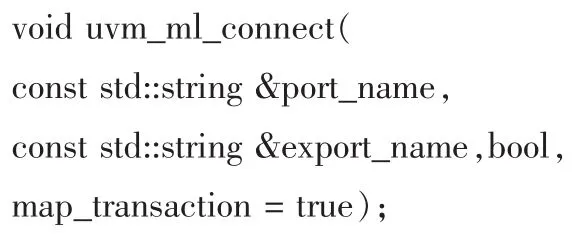

接口被注冊(cè)后建立起了適配層與基類進(jìn)行數(shù)據(jù)流動(dòng)的通道。綁定則是在不同構(gòu)架的適配層與適配層、組件與組件之間建立連接。接口在基類中注冊(cè)后,接著進(jìn)行接口之間的綁定。綁定時(shí),需要為基類提供被綁定的兩個(gè)接口的全路徑名稱,基類會(huì)檢測兩個(gè)接口的合法性,然后將兩個(gè)接口的連接信息加入它的內(nèi)部數(shù)據(jù)庫。以SC構(gòu)架的API綁定TLM1端口和TLM2套接字為例,使用uvm_ml_connect方法實(shí)現(xiàn)綁定。uvm_ml_connect方法的定義為:

其中,port_name是指port端口的全路徑名,如sc.env. port;export_name是export端口的全路徑名,如sc_env. export.name();map_transaction默認(rèn)為true。

2.3驗(yàn)證平臺(tái)的配置

靈活的跨架構(gòu)配置機(jī)制是UVM-ML OA解決方案的一大特點(diǎn)。配置機(jī)制用來配置驗(yàn)證平臺(tái)的眾多參數(shù),在不同構(gòu)架和層次的組件間傳遞數(shù)據(jù),增加平臺(tái)的靈活性。配置機(jī)制是分層次的,在平臺(tái)的樹形結(jié)構(gòu)中較高層次組件的配置信息會(huì)覆蓋低層次組件的配置信息。配置使用間接的方式:配置發(fā)起組件將配置數(shù)據(jù)傳遞到多語言基類中;被配置的外部構(gòu)架組件再從基類中獲取配置數(shù)據(jù)。

在多語言協(xié)同驗(yàn)證平臺(tái)中,配置和獲取數(shù)據(jù)總是成對(duì)出現(xiàn)的。例如,在某個(gè)頂層組件中做配置操作,那么在平臺(tái)的驅(qū)動(dòng)器組件就要做相應(yīng)的獲取操作。

2.3.1配置

一般來講,驗(yàn)證平臺(tái)中每種構(gòu)架的組件只處理本構(gòu)架內(nèi)的配置操作。但在一個(gè)多語言驗(yàn)證環(huán)境中,不同構(gòu)架的組件在整合到一個(gè)平臺(tái)并建立事物級(jí)連接后,配置數(shù)據(jù)也能夠經(jīng)由基類的API傳播到其他語言的構(gòu)架中。

以在SV構(gòu)架的組件配置其他子組件為例,使用uvm_config_*::set(this,inst_name,field_name,value)函數(shù)來設(shè)置配置值。其中,inst_name參數(shù)是被配置子組件的名稱;field_name參數(shù)是子組件內(nèi)被配置對(duì)象的名稱;value參數(shù)代表了具體配置值。設(shè)置的配置值會(huì)在子組件的bulid階段傳遞給子組件。UVM-ML OA支持3種數(shù)據(jù)類型的配置:使用“uvm_config_int”方法配置整型值;使用“uvm_config_string”方法配置字符串;使用“uvm_config_objects”方法配置對(duì)象。

2.3.2獲取

在平臺(tái)運(yùn)行期間,配置數(shù)據(jù)被傳遞基類中,相應(yīng)的目標(biāo)組件要有對(duì)應(yīng)的接收操作從基類中獲取配置數(shù)據(jù)。以e構(gòu)架組件中獲取配置值為例,使用get_config_*(field_name,value)方法獲取配置值。其中,參數(shù)field_name是組件內(nèi)的某一個(gè)被配置過的變量;value參數(shù)是配置值的存儲(chǔ)位置。與set方法類似,get方法也支持3種數(shù)據(jù)類型:使用“get_config_int”方法獲取整型值;使用“get_config_string”方法獲取字符串;使用“get_config_objects”方法獲取對(duì)象。

3 實(shí)用案例

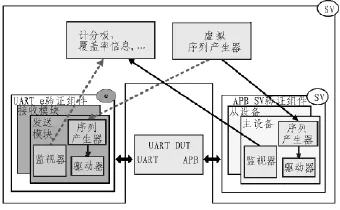

上一節(jié)中,介紹了UVM-ML OA庫處理多語言協(xié)同驗(yàn)證的原理,本節(jié)將以一個(gè)SoC多語言協(xié)同驗(yàn)證項(xiàng)目中的UART模塊為具體實(shí)例,說明SoC多語言協(xié)同驗(yàn)證平臺(tái)的實(shí)現(xiàn)方案,整個(gè)平臺(tái)的結(jié)構(gòu)如圖4所示。

圖4 多語言驗(yàn)證平臺(tái)結(jié)構(gòu)Fig.4Multi-language verification platform structure

作為整個(gè)SoC驗(yàn)證項(xiàng)目的一部分,UART模塊經(jīng)由橋接器集成到整個(gè)SoC系統(tǒng)中。針對(duì)項(xiàng)目組手中擁有由廠商提供的SV的APB總線驗(yàn)證IP和先前的驗(yàn)證項(xiàng)目中留下的,由e語言實(shí)現(xiàn)的UART驗(yàn)證IP。決定搭建多語言協(xié)同驗(yàn)證平臺(tái)對(duì)UART模塊進(jìn)行驗(yàn)證。

如上圖所示,搭建多語言協(xié)同驗(yàn)證平臺(tái)的關(guān)鍵在于:虛擬序列產(chǎn)生器如何驅(qū)動(dòng)異構(gòu)組件的數(shù)據(jù)激勵(lì)、異構(gòu)組件的監(jiān)視器如何與平臺(tái)建立連接、異構(gòu)驗(yàn)證組件在平臺(tái)中如何實(shí)現(xiàn)無差異的配置。

遵循前面章節(jié)多語言協(xié)同驗(yàn)證平臺(tái)搭建的方法,主要步驟如下:

1)整合異構(gòu)組件:實(shí)例化異構(gòu)組件到頂層是整個(gè)平臺(tái)搭建的基礎(chǔ)。將e語言構(gòu)架組件整合到SV環(huán)境中,需要在SV構(gòu)架的testbench文件中實(shí)例化e構(gòu)架的頂層文件e_uart_top。這樣就把所有的組件整合到一個(gè)統(tǒng)一的樹形結(jié)構(gòu)中,部分代碼如下。

function void build_phase(uvm_phase phase);

super.build_phase(phase);

//建立多語言組件連接節(jié)點(diǎn)

etop=uvm_ml_create_component("e","e_uart_top"," e_uart_top",this);

...

endfunction

2)事物級(jí)接口的連接:將不同構(gòu)架的組件整合到一個(gè)統(tǒng)一的結(jié)構(gòu)中后,序列產(chǎn)生器和監(jiān)視器要通過TLM接口與SV架構(gòu)的驗(yàn)證頂層建立事物級(jí)的連接。

這里通過使用register方法和connect方法建立事物級(jí)的連接。以激勵(lì)產(chǎn)生器的連接為例,部分代碼如下。

//建立階段

seqr_proxy=ml_sequencer_proxy:type_id:create(" seqr_proxy",this);

...

class my_env extends uvm_component;

...//連接階段

uvm_ml:connect({e_seqr,"b_isocket"},

my_uvc.seqr_proxy.b_target_socket.get_full_name())

…

endclass

3)跨架構(gòu)配置驗(yàn)證平臺(tái):配置平臺(tái)的參數(shù)可以增加平臺(tái)靈活性,動(dòng)態(tài)的控制平臺(tái)的運(yùn)行。在這個(gè)案例中,在頂層配置e構(gòu)架UART驗(yàn)證組件的address參數(shù),驗(yàn)證平臺(tái)運(yùn)行過程中觀察測試結(jié)果。部分代碼如下。

//頂層的配置操作

uvm_config_int:set(this,"uvm_test_top.testbench. e_uart_top.e_env.e_seqr","address",'h7f);

super.build_phase(phase);

...

//e構(gòu)架的序列產(chǎn)生器獲取配置數(shù)據(jù)

unit e_seqr{

keep uvm_config_get(address);

...

}

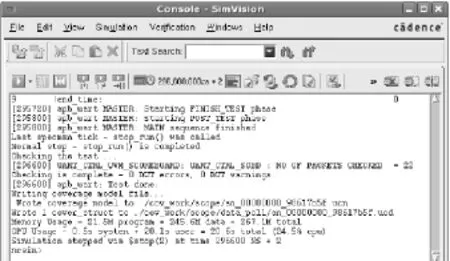

經(jīng)過上面幾個(gè)步驟,完成了SOC驗(yàn)證項(xiàng)目中UART模塊的多語言協(xié)同驗(yàn)證平臺(tái)的搭建,使用IES仿真后的部分結(jié)果如圖5所示。

圖5 仿真結(jié)果Fig.5Simulation results

實(shí)驗(yàn)結(jié)果表明,UVM-ML OA被成功應(yīng)用于SoC多語言協(xié)同驗(yàn)證項(xiàng)目中,對(duì)于多語言驗(yàn)證IP的重用提供了一種有效地解決方案。驗(yàn)證IP由EDA公司提供,或來自于項(xiàng)目組長期積累的成熟模塊,它們的重用提高了驗(yàn)證的可靠性和可信度。

4 結(jié)束語

文中基于UVM-ML OA呈現(xiàn)了一種全新的SoC多語言協(xié)同驗(yàn)證的解決方案。詳細(xì)講述了多語言協(xié)同驗(yàn)證的原理,并基于實(shí)際案例闡述了解決方案的有效性和靈活性。結(jié)果表明UVM-ML OA能有效的應(yīng)對(duì)實(shí)際應(yīng)用中SoC驗(yàn)證面臨的多語言協(xié)同驗(yàn)證問題,為驗(yàn)證人員提供了更可靠、更靈活的多語言驗(yàn)證解決方案。

[1]王嘉良.SoC可重用驗(yàn)證平臺(tái)研究與開發(fā)[D].上海:東華大學(xué),2011.

[2]Yang X,Niu X,F(xiàn)an J,et al.Mixed-signal System-on-a-Chip(SoC)verification based on SystemVerilog model[C]// System Theory(SSST),2013 45th Southeastern Symposium on.IEEE,2013:17-21.

[3]Aynsley J.SystemVerilog Meets C++:Re-use of Existing C/ C++Models Just Got Easier[C]//Design and Verification Conference&Exhibition(DVCon).San Jose,CA:Accellera,2010:255-262.

[4]Erickson A.Transaction-Level Friending:An Open-Source,Standards-Based Library for Connecting TLM Models in SystemC andSystemVerilog[C]//Design and Verification Conference&Exhibition(DVCon).San Jose,CA:Accellera,2013:321-330

[5]Edelmen R,Glassar M.Inter Language Function Calls BetweenSystemCandSystemVerilog[C]//Designand Verification Conference&Exhibition(DVCon).San Jose,CA:Accellera,2007:143-150.

[6]文良,靳榮利,吳龍勝,等.基于AHB總線接口的可重用性驗(yàn)證環(huán)境的實(shí)現(xiàn)[J].微電子學(xué)與計(jì)算機(jī),2011,28(7):201-207. WEN L,JIN R,WU L,et al.Building Reused eVC Verification Based on AHB Bus[J].Microelectronics& Computer,2011,28(7):201-207.

[7]M.Guy.UVM-ML Open Architecture-version 1.4.4:Enabling Multi-Language and Multi-Framework Verification[EB/OL].[2014-12-02].http://forums.accellera.org/files/file/65-uvm-mlopen-architecture.

[8]B.Sniderman,V Yankelevich.Multi-Language Verification:SolutionsforRealWorldProblems.[C]//Designand VerificationConference&Exhibition(DVCon).India:Accellera,2014:87-92.

[9]F.Hannes,S.Kishore.Multi-Language Verification:Solutions forRealWorldProblems.[C]//DesignandVerification Conference&Exhibition(DVCon).India:Accellera,2014:63-70.

Research of SoC multi-language co-verification platform technology

WANG Ji,F(xiàn)ENG Zhi-hua

(Institute 706,Second Academy of China Aerospace Science and Industry Corporation,Beijing 100854,China)

The characteristic of SoC based on IP design makes the verification projects increase the demand for multi-language VIP(Verification IP)Co-verification,which has brought great challenges to the verification work.In order to solve the problem of the multi-language VIP be flexible reused in SoC verification environment.Proposes a solution which is based on an open source multi-language Framework Library,detailed multi-language co-verification technology and the method of building the verification platform,and through a example demonstrates the effectiveness and flexibility of the proposed approach.

SoC;VIP;Multi-Language;co-verification;reuse

TN406

A

1674-6236(2015)20-0130-04

2015-01-08稿件編號(hào):201501062

中國人民解放軍總裝備部預(yù)研基金(513150502)

王紀(jì)(1990—),男,安徽宿州人,碩士研究生。研究方向:嵌入式設(shè)計(jì)與驗(yàn)證。