高性能處理器存儲控制器分析與優化設計

孫也

(吉林廣播電視大學,吉林 長春 130022)

高性能處理器存儲控制器分析與優化設計

孫也

(吉林廣播電視大學,吉林 長春 130022)

針對處理器訪存延時問題,本文對X處理器和DDR3 SDRAM進行了深入分析。為提高訪存過程的并行性,對存儲控制器的結構進行了優化設計。設計了全異或地址映射方式和分層訪存調度器,從而提高了存儲器帶寬利用率,具有一定的實際應用價值。

存儲控制器;優化;處理器

一、引言

存儲控制器決定了計算機的內存容量、內存類型與速度等重要參數,控制著存儲器的訪問速度,決定了處理器性能的發揮,尤其在多線程、多核心的處理器中更為突出。因此,存儲控制器設計的好壞直接影響處理器性能的高低。

針對現有X處理器存儲控制器中存在的訪存延時問題,為提高訪存過程的并行性,本文對存儲控制器地址映射方式和訪存調度模式進行了優化設計,通過對命令重排序,改變訪存地址,減少延時,以此提高存儲器帶寬利用率和存儲性能。

二、存儲控制器基本結構

存儲控制器連接存儲器和L3 cache,用于接收來自L3 cache的訪存請求,按照訪存請求的優先級進行調度,將訪存請求轉換成存儲器能夠識別的語言后發送到存儲器,完成數據讀寫任務。

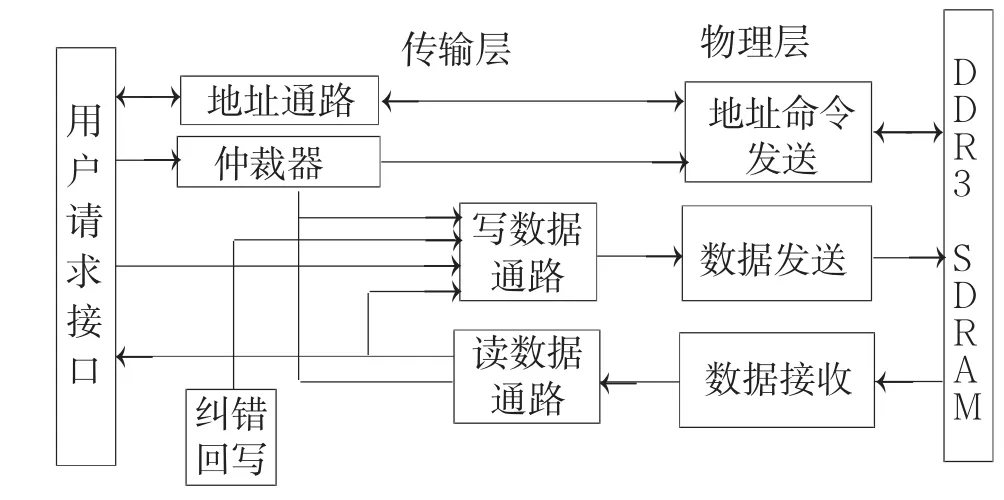

X處理器集成了4個寬度為64位的DDR3存儲控制器,工作頻率達1600MHz,從而滿足其高性能運算的需求。具有限制功耗、錯誤檢測、自動配置等功能,防止因功耗過大而影響處理器的性能,提高了存儲控制器的可靠性及可維性,其結構如圖1所示。

圖1 存儲控制器結構

可以看出,存儲控制器主要包括傳輸層和物理層,前者主要用來接收來自用戶層的存訪請求,轉化為物理層可識別的語言后發送到物理層,同時也承擔接收物理層返回數據的功能。再按照上層邏輯所需要的時序發送給上層用戶邏輯,后者則按規定的格式將傳輸層送來的信息發送到DDR3芯片上,同時也擔負接收DDR3讀出數據的作用。

三、存儲控制器優化設計

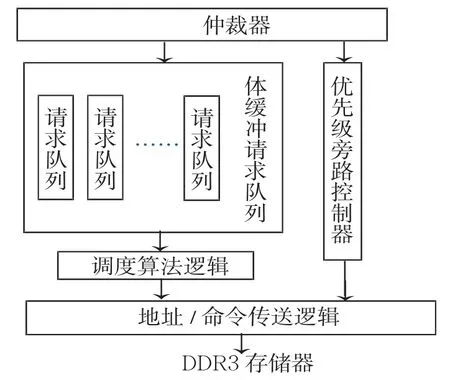

X處理器芯片集成了4個采用多體并行存儲結構的存儲控制器,每個存儲控制器可以管理4個rank,共享一條外部總線,數據訪問量很大,所以對映射方式和存儲調度過程都有很高的要求。基于此,本文在原有存儲控制器結構的基礎上,對存儲控制器中進行優化設計:一是增加了訪存調度器模塊;二是對用戶請求接口映射邏輯進行改進;三是增加了虛擬緩沖行模塊,如圖2所示。

圖2 存儲控制器優化結構

1、地址映射設計

用戶請求接口是上層用戶與DRAM控制器之間的接口,包括地址映射邏輯、控制邏輯以及請求隊列三個組成部分,用于接收L3 Cache發送的訪存請求、請求信號的讀、寫與傳輸,以及完成物理地址到存儲器實際地址的映射。

基本地址映射方式只針對同一個通道中的同一行的映射關系,并行執行程序的優勢還沒有發揮出來。同時,多核多線程處理器容易導致bank發生訪問沖突,這一問題用現有的地址映射方法還不能有效解決。針對這一問題,本研究對地址映射方式進行優化,設計了一種全異或地址映射方式,即取出一部分請求地址與rank地址異或形成新的rank地址,另一部分與bank地址異或形成新的bank地址,如圖3所示。

圖3 優化后的映射方式

2、分層訪存調度

內存系統的帶寬和延時與訪問的存儲體地址和行列地址有著密切的聯系,為此本文采用分層調度算法,訪存調度流程如圖4所示,可根據當前請求和下一請求的地址是確定當前請求訪問狀態。當前請求讀寫訪問結束時,被訪問行將關閉,新的命中行開啟,否則當前請求將禁止自動預充,讀寫訪問結束時,當前被訪問行保持開啟狀態。該方法可有效改變訪存地址,減少延時,提高存儲性能。

圖4 訪存調度流程

四、結論

X處理器是一款多核多線程高性能處理器。為解決處理器與存儲器之間速度差距問題,本文的設計設計一款符合X處理器訪存特性的高效存儲控制器。提出了改變地址映射方式和存儲調試模式的優化設計方案,提高了數據傳輸的并行性,降低了訪存延時,大大提高了處理器的性能。

[1]鄧麗.高帶寬低延遲的DDR2存儲器控制器的研究與實現[D].長沙:國防科技大學,2006:25~28.

[2]陳先.嵌入式SRAM控制器驗證關鍵技術研究[D].西安:西安電子科技大學,2009(1):13-15.

TP332

A

1008-7508(2015)09-0101-02

2015-07-11

孫也(1981-),吉林長春人,吉林廣播電視大學講師,計算機科學與技術專業。