基于FPGA的數字頻率計設計

周嘉騰+++胡佳文

摘 要:利用FPGA的等精度測量原理設計數字頻率計,可實現1HZ-100MHZ信號頻率的等精度頻率測量并增加測量周期、時間間隔,占空比的功能。本設計以Altera FPGA系列DE0-Nano Cyclone IV器件為核心,運用VHDL語言設計功能模塊,進行信號的控制、數據讀取、運算處理以及屏幕顯示。實驗表明:該頻率計具有測量精度高、功能豐富、控制靈活等特點。

關鍵詞:等精度測量 FPGA 電壓比較器

隨著微電子技術和計算機技術的發展,可編程邏輯器件,EDA技術,SOPC等新概念和新技術層數不窮新技術的應用迅速滲透到電子,通信,信息汽車制造等領域,有力的推動了社會生產力的發展和社會信息化程度的提高。在電子技術中,頻率是最基本的參數之一,并且與許多電參量的測量方案和結果都有密切的關系,因此,頻率的測量方法的研究越來越受到重視。基于傳統測頻原理的頻率計的測量精度隨被測信號頻率的下降而降低,在實用中有較大的局限性,而FPGA等精度頻率計不但具有較高的測量精度,而且在整個頻率區域能保持恒定的測量精度。

理論分析

1、低頻信號測量

低頻信號一般采用間接測頻法。通過測量待測信號的周期并求其倒數,需要有標準頻率的信號,在待測信號的一個周期內,記錄標準頻率的周期數,這種方法的計數值會產生±1個脈沖誤差,并且測試精度與計數器中記錄的數值有關,為了保證測試精度,測周期法只適用于低頻信號的測量。

2、高頻信號測量

高頻信號采用直接測頻法。直接測頻法就是在確定的閘門時間內,記錄被測信號的脈沖個數。由于閘門時間通常不是待測信號的整數倍,這種方法的計數值也會產生最大為±1個脈沖誤差。進一步分析測量準確度:待測信號脈沖周期為Tx,頻率為Fx,當測量時間為T=1s時,測量準確度為&=Tx/T=1/Fx。由此可知,直接測頻法的測量準確度與信號的頻率有關:當待測信號頻率較高時,測量精確度也較高,反之測量準確度較低。因此直接測頻法只適合測量頻率較高的信號,不能滿足在整個測量頻段內的測量精度保持不變的要求。

3、等精度測量

等精度測頻的方法是實在直接測頻方法的基礎上發展起來的,他的閘門時間不是固定的值,而是被測信號的整數倍,即與被測信號同步,因此避免了對被測信號計數所產生±1個字誤差,并且達到了在整個測試頻段的等精度測量。在測量過程中,有兩個計數器分別對標準信號和被測信號同時計數,首先開啟閘門開啟信號(預設閘門上升沿),此時計數器并不開始計數,而是等到被測信號的上升沿到來時,計數器才開始真正計數,然后預設閘門關閉信號(下降沿)到時,計數器并不立即停止計數,而是等到被測信號的上升沿到來時才結束計數,完成一次側量過程。

采用等精度頻率測量法,測量精度保持恒定,不隨所測信號的變化而變化。在快速測量的要求下,要保證較高精度的測頻,必須采用較高的標準頻率的信號。單片機受本身時鐘頻率和若干指令運算的限制,測頻速度較慢,無法滿足高速高精度的測頻要求;而采用高集成度、高速的現場可編程門陣列FPGA為實現高速、高精度的測頻提供了保證。

系統設計

1、電路設計

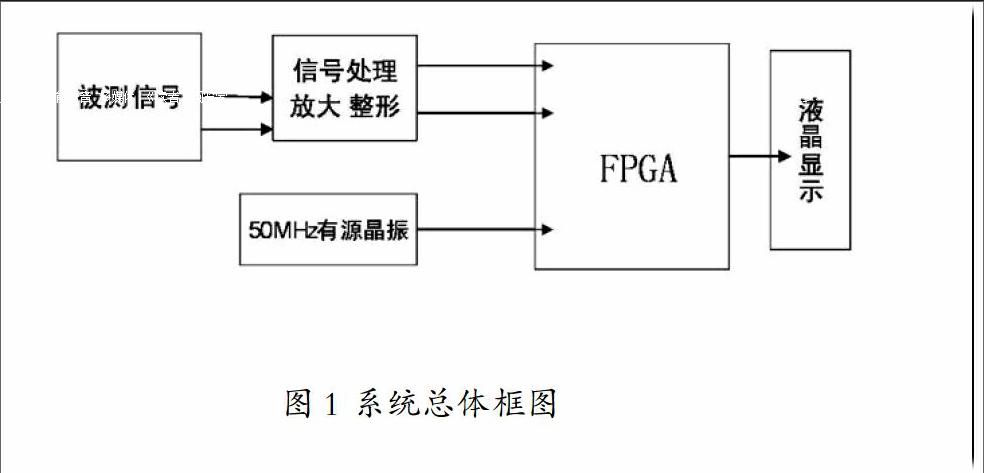

系統總體框圖如圖1所示。

圖1 系統總體框圖

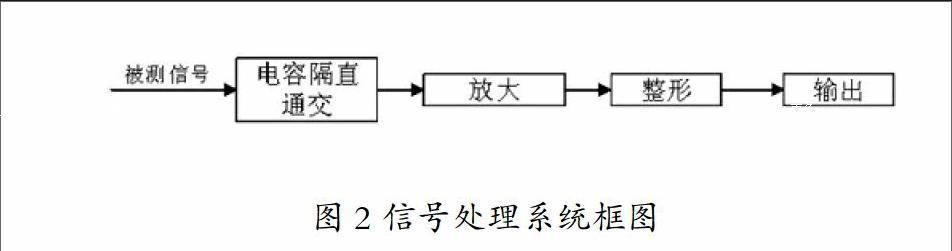

信號處理系統如圖2所示。

圖2 信號處理系統框圖

1.1放大電路

運算放大器是集成器件,集成電路中大量使用有源器件組成的有源負載,以獲得大電阻,提高放大電路的放大倍數;將其組成電流源,以獲得穩定的偏置電流,所以一般集成運放的放大倍數與分立元件的放大倍數相比大得多,而且其相對精度好,故對稱性能好,特別適宜制作對稱性要求高的電路。低噪聲高速運算放大器OPA842使用統一,兩個內部增益穩定,電壓反饋架構增益級,實現了非常低的失真在很低的頻率范圍,“經典”差分輸入提供了所有熟悉的精度好處,偏置電流的消除和非常低的運算amps,反向電流噪聲與寬帶電流差分增益/相位性能,低電壓噪聲,高輸出電流驅動是OPA842理想的最高動態范圍的應用。

1.2整形電路

集成電壓比較器比集成運放的開環增益低,失調電壓大,共模抑制比小;但其響應速度快,傳輸延遲時間短,而且可將模擬信號轉換成二值信號,即只有高電平和低電平兩種狀態的離散信號,不需外加限幅電路就可直接驅動TTL、CMOS等集成數字電路。我們采用高速比較器TLV3501。

1.3 FPGA和液晶顯示模塊

本設計采用臺灣友晶Altera DE0-Nano FPGA入門學習開發板,DE0-Nano展示了一個緊密型的FPGA開發平臺適用于諸如自動控制裝置和便攜式項目的原型電路設計,該平臺采用了有著22320個邏輯單元的Cyclone IV芯片實現了盡可能的簡易設計。

采用現場可編程門陣列(FPGA)為控制核心采用現場可編程門陣列(FPGA)為控制核心,利用VHDL 語言編程,下載燒制實現。將所有器件集成在一塊芯片上,體積大大減小的同時還提高了穩定性,可實現大規模和超大規模的集成電路,測頻測量精度高,測量頻率范圍大,而且編程靈活、調試方便。

利用FPGA高速的信號采集處理能力,采用等精度測量頻率,在整個頻率范圍內測量都能達到相同的精度,不隨頻率的變化而變化。

JLX12864G-332 圖像型點陣液晶模塊使用方便、顯示清晰,廣泛應用于各種人機交流面板。JLX12864G-332 可以顯示 128 列*64 行點陣單色圖片。

2、提高抗干擾的措施

采取抗干擾措施以提高儀器靈敏度。具體措施:①數字地與模擬地嚴格劃分,并于電源模塊濾波前一點落地;②各單元供電在線路板上多加裝去耦濾波電容以旁路電網干擾,對高低頻信號干擾信號具有很強的抑制能力;③由于輸入信號的變化可能很大,在大信號時能滿足要求,而在小信號時則很容易受到干擾,所以電路設計時采用大面積接地,輸入引線采用高頻監控電纜以消除外界的電磁場干擾。

測試結果及分析

1、測試條件與儀器

測試條件:實驗室環境,硬件電路與系統原理圖完全相同,硬件電路保證無虛焊。檢查多次。

測試儀器:數字示波器、數字萬用表、低頻信號發生器、高頻信號發生器。

2、測試方法

使用信號發生器產生1hz到10Mhz的頻率,用標準頻率計測得標準頻率,再用設計的頻率計測得頻率,最后求出誤差。

3、測試分析

經過實測,表明本設計方案是科學的,合理的。具體能測出以下幾個信號:

可以檢測1Hz-100MHz的正弦信號,被測信號的有效值電壓范圍為10mV-1V,測量相對誤差的絕對值小于10^-4。

可以檢測1Hz-5MHz的方波信號,被測信號的有效值電壓范圍為50mV-1V,測量相對誤差的絕對值小于10^-2,被測時間間隔范圍0.1us-100ms,測出信號的占空比10%-90%,顯示的分辨率為0.1%。

結論

本次設計是基于FPGA的等精度數字頻率計的設計。在高速時鐘隨處可見的現代電子系統,有著非常廣泛的研究價值,經實驗驗證,該頻率計達到設計要求,可以改變數字頻率計的測量范圍,具有較高的整體性和可靠性,而且容易生產造價比較低,具有較好的市場前景。與傳統的頻率計相比,利用FPGA設計的頻率計提高了系統設計的實用性和可靠性,而且實現數字系統的軟件化是數字邏輯設計的趨勢。

參考文獻:

[1] 周立功等.SOPC嵌入式系統基礎教程[M].北京:北京航空航天大學出版社,2006.

[2] 莫琳.基于FPGA的等精度頻率計的設計與實現[J].現代電子技術,2004,23 (10):81-82.

[3] 張杰,姚劍,葉林等.頻率測量的新方法[J].工業儀表與自動化裝置,2003,29(1):63-65.

基金項目:浙江海洋學院2015年度大學生科技創新項目。

(作者單位:浙江海洋學院)endprint