面向交換機驗證測試的流量生成器研究與實現

趙曉輝,李昀義,王曉婷,郭華儉,王憶文

(1.成都華微電子科技有限公司,成都610041;2.電子科技大學微電子與固體電子學院,成都610054)

面向交換機驗證測試的流量生成器研究與實現

趙曉輝1,李昀義2,王曉婷2,郭華儉2,王憶文2

(1.成都華微電子科技有限公司,成都610041;2.電子科技大學微電子與固體電子學院,成都610054)

流量生成器是交換機驗證與測試平臺的核心組成部分,它可以模擬網絡流量行為,根據網絡協議生成測試數據包,對交換機進行功能驗證和性能測試。基于SoC架構的流量生成器,利用軟件的靈活性來生成復雜的流量模型,利用硬件生成符合協議的數據包,能夠模擬現代網絡中高負載、高速率、環境復雜的網絡流量。基于Xilinx Virtex-5系列FPGA開發板,實現了一種流量生成器,具備單端口速率Gbps量級的均勻、Poisson和MMPP三種流量模型,并通過測試平臺對流量生成模型進行了驗證。

交換機;流量生成器;流量模型;片上系統;現場可編程邏輯陣列;驗證

1 引 言

交換機作為現代大型網絡系統的基礎,在信息交換、數據傳輸領域有著非常重要的作用,其性能決定著網絡系統的性能和穩定性。所以,交換機的驗證測試也成為了交換機研究的一個重要方向。現行交換機的網絡流量線速率已達到Gbps量級,而且在實際的網絡環境中負載流量可能出現各種不同的復雜情況。普通的功能測試和壓力測試,已經不能判斷所設計的交換機是否適應現代網絡需求。這對交換機測試設備提出了更高要求。

流量生成器,就是模擬網絡流量行為,產生符合網絡協議測試數據包的測試設備。搭載流量生成器的測試平臺,可以模擬真實網絡流量行為,完成對網絡設備的功能驗證和性能測試,幫助其在設計階段實現功能驗證和錯誤定位,也可在應用階段完成性能測試和改良升級。

目前,常見流量生成器有基于PC的軟件實現和基于專用測試設備的硬件實現兩種方式。軟件實現方案[1],由軟件程序產生數據包發送至線卡,該方案可實現多種流量模型,修改靈活、價格低廉,但隨著端口數量的增減,傳輸速率受限于軟硬件接口的帶寬。硬件實現方案[2-3],則采用多硬件系統并行運行產生數據包,以解決軟硬件接口的瓶頸,但一般價格高昂、流量模型稀少。通過SoC架構實現流量生成器[4-5],既可以利用軟件的靈活性生成各種復雜的流量模型,也可以發揮硬件高速并行的優勢,生成高速、高負載、多端口的網絡流量。

針對航空領域廣泛使用的FC-AE交換機,以SoC架構方案為模板,在基于Xilinx Virtex-5系列開發板搭建的SoC平臺上,實現了單端口速率達到Gbps量級,支持均勻、Poisson和MMPP三種流量模型的流量生成器。

2 網絡流量模型

為了精準地測試和評估交換機的性能,流量模型的研究變得尤為重要。基于SoC架構的流量生成器,根據現代網絡特性以及測試需求,選取了均勻、Poisson和MMPP三種典型的流量模型。均勻流量模型根據固定負載,產生恒定速率的流量,用于測試交換機端口間數據傳輸功能驗證。Poisson和MMPP兩種流量模型在網絡流量行為建模中應用廣泛,可分別適用于交換機的低負載、低突發性能測試以及高負載、高突發性能測試。

2.1 Poisson模型

在網絡流量建模發展的初期,便使用Poisson模型來研究網絡流量。Poisson模型即指在時間序列t內,包到達的數量n(t)符合參數為λt的Poisson分布,如公式所示[6]。

其相應的包到達時間間隔序列T呈負指數分布,即F(t)=1-e-λt。其中,Poisson過程的強度表示單位時間間隔內出現包數量的期望值,即包到達的平均速率,其值為1/E(t)。

Poisson模型假設網絡事件(如數據包到達)是獨立分布的,并且只與一個單一的速率參數λ有關。Poisson模型較好地滿足了網絡的建模需求,在低負載、低突發性的小型網絡設計、維護、管理和性能分析等方面發揮了很大作用。

2.2 Markov模型

對于一個給定的狀態空間S={S1,S2,…,Sm},Xn表示在n時刻狀態的隨機變量,如果Xn+1=Sj的概率只依賴于當前的狀態,{Xn}就形成了一個Markov鏈。Markov模型是利用某一變量的現在狀態和動向去預測該變量未來的狀態和動向的一種分析方法。其在隨機過程中引入相關性,在一定程度上描述了網絡流量行為的突發性[6]。

Markov調制的Poisson過程(MMPP)便是常見的Markov模型中的一種,它是一種雙隨機過程,可理解為參數為λ的Poisson過程和一個參數為υ的更新過程的疊加[7-8]。MMPP由于相關性和突發性的特點,在高負載、高突發性、多業務類型的主干網絡建模中應用廣泛。

3 流量生成器的設計與實現

采用基于SoC架構的流量生成器,具有成本低、配置靈活、端口易擴展的特點。加之IP化的設計方式,使得其可適用于不同網絡協議交換機或其它網絡設備的測試。

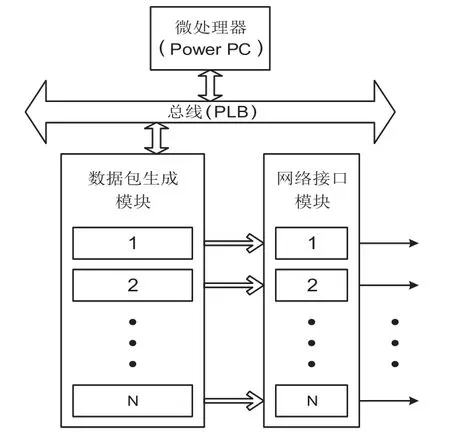

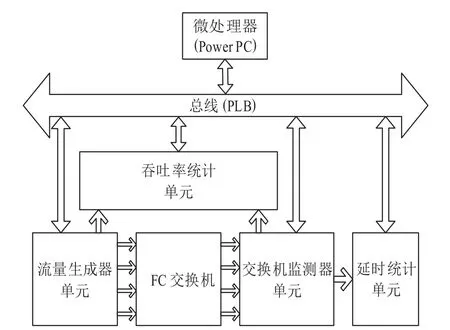

該流量生成器在基于Xilinx Virtex-5系列的FPGA開發板搭建的以Power PC 440為硬核微處理器的SoC平臺上實現。針對選取的均勻、Poisson和MMPP三種流量分布,經過合理的軟硬件劃分,將靈活多變的流量模型交由軟件完成,而要求快速響應的數據包產生、發送過程交由硬件完成。如圖1所示,軟件部分為微處理器,硬件部分包括數據包生成模塊、網絡接口模塊。

圖1 基于SoC架構的流量生成器

流量生成過程由Power PC上運行的流量產生程序根據用戶的配置信息轉化為流量模型的配置信息和數據包生成參數,由軟硬件接口將配置信息和生成參數傳遞至數據包生成模塊,數據包生成模塊便可在指定時刻產生相應的數據包,網絡接口模塊將數據包轉換為相關的網絡協議發送至網絡設備。

3.1 軟硬件接口

軟硬件接口,即微處理器上運行的流量產生程序通過PLB總線與數據包生成模塊交互的數據格式。主要包括兩大類型:一種為配置信息,包括網絡協議類型(數據包幀格式)、端口信息(源/目地址)等,該部分在系統上電后只進行初始化配置,不隨程序的運行而更改;另一種為數據包生成參數,主要為數據包時間間隔(前后兩個數據包之間的延時間隔)和數據包幀長,該部分在測試設備運行中由程序根據用戶配置的流量模型而生成,每個生成參數都可以使數據包生成模塊產生一個獨一無二的數據包,并控制其在指定時刻發送。

3.2 軟件部分

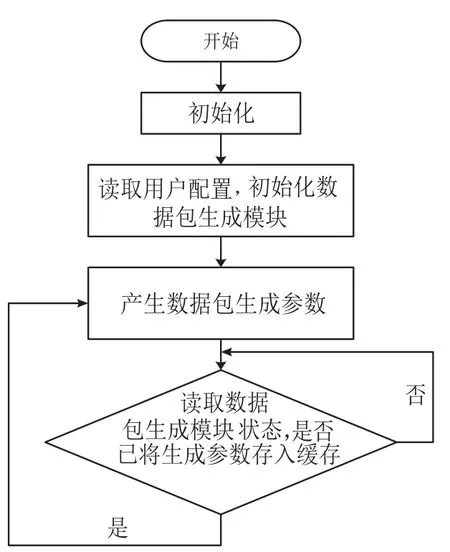

軟件部分的主要功能為SoC平臺的初始化和流量模型的產生。流量模型的產生,就是將設計的均勻流量模型、Poisson模型和MMPP模型,根據用戶配置參數轉化為硬件能夠識別的配置信息和數據包生成參數,并發送至軟硬件接口。其工作流程如圖2所示,具體步驟如下:

(1)PowerPC在系統上電后,通過PLB總線對SoC硬件模塊進行初始化;

(2)讀取用戶配置信息,并轉化為硬件可識別的配置信息,對數據包生成模塊進行初始化配置;

(3)流量產生程序根據用戶配置信息,產生數據包生成參數并傳輸至數據包生成模塊;

(4)讀取數據包生成模塊狀態,若數據包生成模塊未讀取數據包生成參數,則等待;若數據包生成模塊已讀取數據包生成參數,則進入步驟3。

3.3 硬件部分

硬件部分的主要功能是根據軟件傳輸至軟硬件接口的數據包生成參數,產生符合網絡協議的數據包格式,并在流量模型的要求時刻發送至傳輸端口。

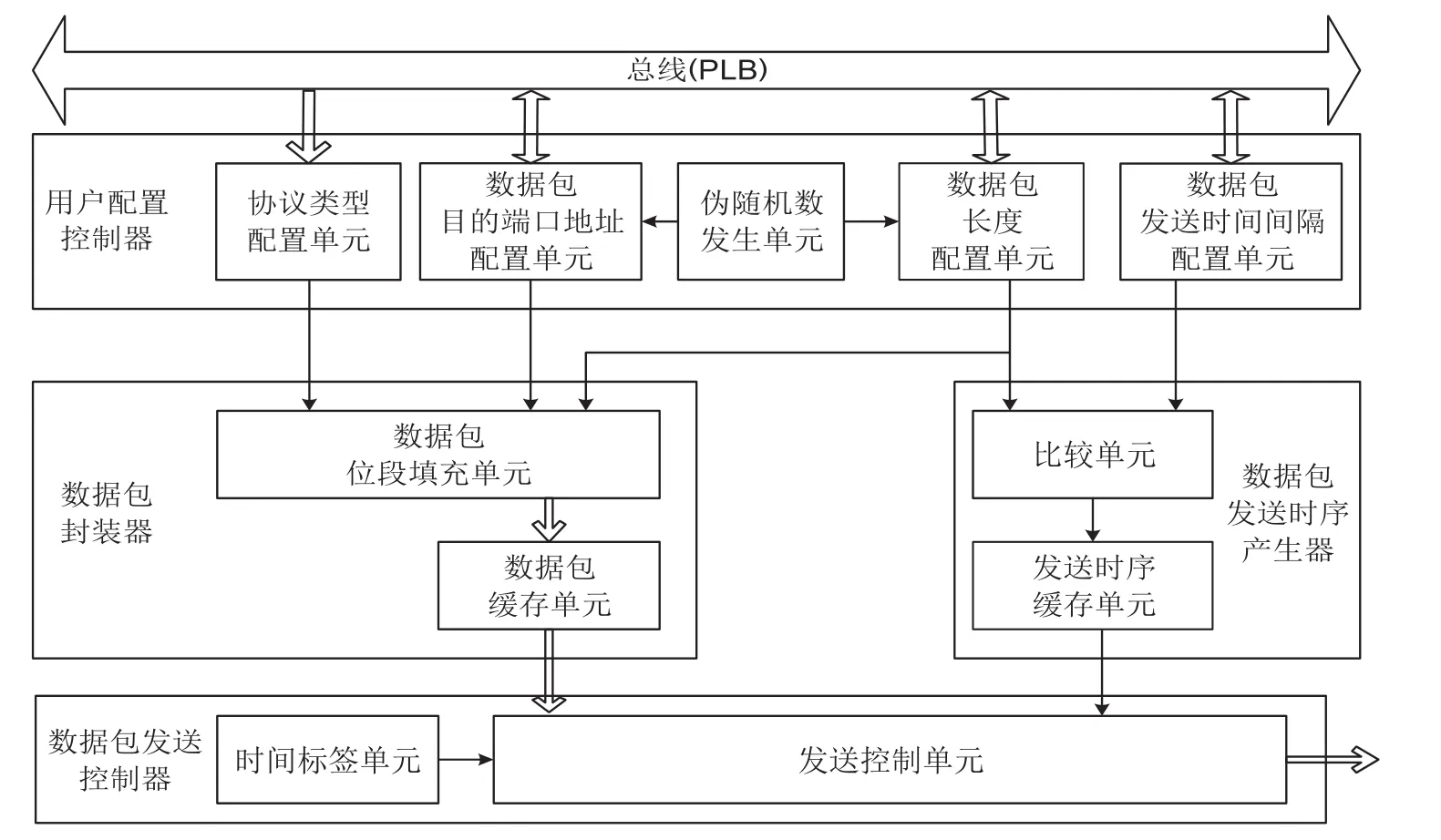

該部分采用Verilog HDL編制,利用FPGA的可編程邏輯實現,并作為定制IP掛載在SoC總線上,其架構如圖3所示。數據包生成模塊包括:用戶配置控制器、數據包封裝器、數據包發送時序產生器和數據包發送控制器。用戶配置控制器,負責將初始化配置信息和數據包生成參數寫入對應單元;數據包封裝器,根據配置的協議類型信息、端口信息、數據包幀長信息,生成符合要求的數據包,并寫入數據包緩存;數據包發送時序產生器,根據數據包時間間隔和數據包幀長信息,對數據包時間間隔進行修正,并寫入發送時序緩存;數據包發送控制器,根據修正后的數據包時間間隔信息,將數據包緩存單元的數據包發送到網絡接口模塊。網絡接口模塊與網卡功能類似,將流量生成器產生的數據包通過物理層轉化傳輸到網絡設備,該模塊可根據不同的網絡協議進行設計,以擴展流量生成器的適用范圍。

圖2 流量生成器軟件流程

圖3 流量生成器硬件架構

4 流量模型驗證

該流量生成器在支持FC-AE協議的交換機測試中,進行了應用。在真實的測試實驗中,搭建了如圖4所示的測試環境。FC交換機為被測設備,其余部分均為測試平臺。

圖4 FC交換機測試平臺

為驗證設計的流量生成器是否符合理論流量模型,在測試初期,去除了上述環境中的FC交換機,將流量生成器接口直接搭載在監測器上。

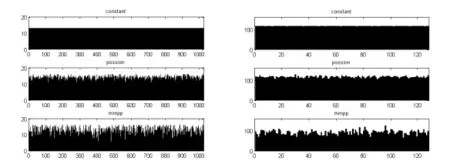

圖5給出了流量模型驗證中的部分測試結果。對三種不同的流量模型,設置相同的測試參數進行對比,其中,負載率為0.8、數據包幀長為1000bytes、測試長度為10ms。左圖的每一個柱形圖表示0.1ms內產生的數據包個數,右圖為0.8ms內產生的數據包個數。由圖5可知,均勻模型可以以恒定速率產生并發送測試數據包。Poisson模型在短時間刻度的情況下很好的體現了網絡行為的突發性,但在長時間刻度的情況下趨于平滑。Markov模型無論是短時間刻度和長時間刻度都很好的體現了網絡突發性。這與實際的流量模型情況一致。

圖5 流量生成器驗證結果

5 結束語

在FC-AE協議環境中,對所實現的流量模型進行了設計、驗證與應用。基于SoC架構的軟硬件協同設計方案,使得該流量生成器可根據用戶的配置信息,靈活配置為多種預設的流量模型和負載條件,精確、迅速地產生數據包,極大地緩解了軟硬件接口帶寬對端口速率的影響,單端口數據流線速率可達Gbps量級。通過更改網絡端口模塊,還可以廣泛地適用于多種網絡協議。該設計既能解決軟件實現方案中高速交換機驗證測試的困難,又能解決專用測試設備成本高的問題,為交換機驗證與測試提供了一種有效解決方案。

[1] Avallone S,Guadagno S,Emma D,et al.D-ITG Distributed Internet Traffic Generator[C]./QEST 2004 Proceedings.First International Conference on the IEEE:Quantitative Evaluation of Systems,2004.

[2] Sanl M,Schmidt E G,Güran H C.FPGEN:A fast,scalable and programmable traffic generator for the performance evaluation of high-speed computer networks[J].Performance Evaluation,2011,68(12):1276-1290.

[3] Spirent.Hypermetrics fibre channel test module[EB/ OL].2009 http://www.spirent.cn/~/media/Datasheets/Broadband/PAB/SpirentTestCenter/STC_HyperMetrics_FC-Module_datasheet.pdf.

[4] Covington G A,Gibb G,Lockwood J W,et al.A Packet Generator on the NetFPGA Platform[C]./Annual IEEE Symposium on.IEEE:Field-Programmable Custom Computing Machines,2009.

[5] Tagami A,Hasegawa T,Hasegawa T,et al.OC-48c traffic tester for generating and analyzing long-range dependence traffic[J].Transactions of the Institute of Electronics Information&Communication Engineers B,2002,85:975.

[6] 張賓,楊家海,吳建平.Internet流量模型分析與評述[J].軟件學,2011,22(1):115-131.ZHANG B,YANG J,WU J.Analysis and Commentary of Internet Traffic Models[J].Journal of Software,2011,22(1):115-131.

[7] 逯昭義.通信業務量理論與應用[M].北京:電子工業出版社,2011.LUZ.TheoryandApplicationsofCommunication Business Volume[M].Beijing:ElectronicsIndustry Press,2011.

[8] Shah-Heydari S,Le-Ngoc T.MMPP Modeling of Aggregated ATM Traffic[J].Canadian Conference on Electrical&Computer Engineering,1998,1:129-132.

Research and Implementation of Traffic Generator for Switch

Zhao Xiaohui1,Li Yunyi2,Wang Xiaoting2,Guo Huajian2,Wang Yiwen2

(1.Chengdu Sino Microelectronics Technology Co.,Ltd.,Chengdu 610041,China;2.School of Microelectronics and Solid-State Electronics,University of Electronic Science and Technology,Chengdu 610054,China)

The traffic generator,as the key component of the platform for verifying and testing switch,can generate data packets for different network protocol by simulating network traffic.The SoC-based traffic generators,using software to generate the complex traffic types and hardware to generate data packets,can meet the requirements of the network in high-speed,high-load and complex environment.A traffic generator is realized based on Xilinx Virtex-5 FPGA development board with the models of uniform,Poisson and MMPP traffic at Gbps line rates,and verified on the test platform.

Switch;Traffic generator;Traffic model;SoC;FPGA;Verification

10.3969/j.issn.1002-2279.2015.04.006

TN919.6

A

1002-2279(2015)04-0020-04

趙曉輝(1975-),男,遼寧省昌圖縣人,高級工程師,主研方向:大規模集成電路設計及應用,數據傳輸與處理。

2015-06-03