基于CPCI的動態可重構系統設計與實現

熊璐

摘 要: 近年來航天測控任務出現了測控目標多,信息傳輸量大,工作模式多樣化等特點,為了滿足實際測控任務中對設備的處理能力和靈活性的更高要求,該文實現了一種基于CPCI的動態可重構系統設計。在基帶設備中通過應用程序將配置文件由CPCI總線根據需要實時寫入到信號處理板上,并由主控FPGA將配置數據加載到核心處理器件FPGA和DSP中。與傳統的FPGA和DSP加載方式相比,這種方法可以在極短的時間實現基帶設備不同功能和模式的快速切換,不僅節約了硬件資源同時也使系統具有較大擴展性和靈活性,能夠滿足不同應用需求。該文給出這種可重構系統的詳細設計和工程中的典型應用,該設計已經在實際中應用并取得理想的效果。

關鍵詞: FPGA; DSP; 動態配置; CPCI

中圖分類號: TN911?34 文獻標識碼: A 文章編號: 1004?373X(2016)08?0104?04

Design and implementation of dynamic reconfigurable system based on CPCI

XIONG Lu

(The 10th Research Institute of CETC, Chengdu 610036, China)

Abstract: In recent years, many features of multi?target, large amount of information transmission, and diversification of work mode have appeared in aerospace tracking and control tasks. In order to meet the higher requirements of the device processing capacity and flexibility in actual observation and control tasks, the design of dynamic reconfigurable system based on CPCI is realized in this paper. In the baseband device, the configuration files are written on the signal processing board through CPCI bus in real time according to requirements, and then the layout data is loaded to FPGA and DSP by main?control FPGA. Compared with traditional loading modes of FPGA and DSP, this method can realize the fast switch of different functions and modes of base band equipment in very short time. It not only saves the resources of system, but also make the system have greater expansibility and flexibility. The design of this kind of reconfigurable system is discussed in detail and the typical application in practical project is given in this paper, which has achieved an ideal effect in practical work.

Keywords: FPGA; DSP; dynamic configuration; CPCI

近年來隨著航天事業的發展,測控任務出現了測控目標多,信息傳輸量大,工作模式多樣化等特點,因此對設備的處理能力和靈活性提出了更高要求。通過動態實時的重構基帶設備,使其具有不同的測控功能,不僅能夠滿足多種場合的任務需求還節約了硬件資源和設備成本,具有靈活、高效等特點。

1 CPCI總線概述

CPCI(Compact Peripheral Component Interconnect)總線是一種高性能局部總線,數據總線為32位,可擴展為64位,數據傳輸速率[1]為128~528 MB/s。由于CPCI 局部總線獨立于處理器的獨特設計和其高性能、低成本、開放性等方面的優勢,它在航天領域的應用相當廣泛。在本設計中通過CPCI總線進行配置數據流的傳輸,相對于傳統的電纜和網絡下載具有速度快、延時小、可靠性高等特點。

2 硬件實現

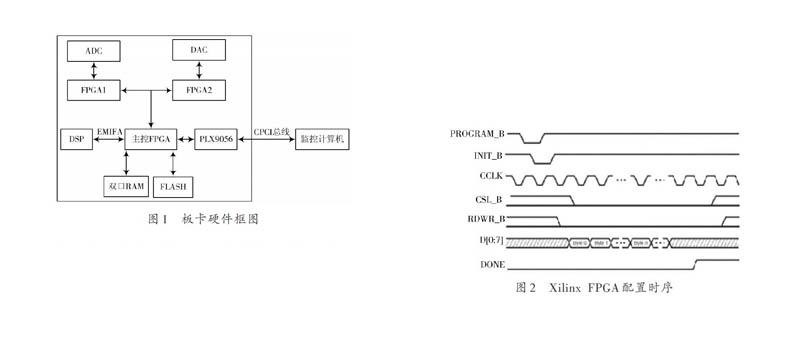

圖1為應用于某航天地面測控基帶設備中CPCI信號處理板卡硬件框圖。FPGA1和FPGA2為Xilinx 公司VIRTEX 6系列FPGA,對ADC采樣中頻輸入信號的數據進行功率調整,數字濾波,載波恢復,信息提取,位同步,幀同步,信息提取,調制等處理。DSP為 TI公司的TMS320C6455,實現參數計算,頻率捕獲,傳輸控制等功能。主控FPGA是采用Xilinx公司的VIRTEX 5 FPGA實現,完成板上V6 FPGA和DSP程序的加載,電源管理與各芯片之間的接口控制等功能。雙口RAM用于緩存上報監控計算機的數據和DSP的配置數據。PLX9056為CPCI總線接口芯片,實現PCI協議到本地總線的轉換。監控計算機通過CPCI總線將數據讀取后進行后續處理,同時監控計算機還可以通過CPCI總線把需要調制的數據注入到FPGA和DSP中,調制后由DAC轉換成模擬中頻信號。通過監控計算機的人機交互界面可實現對板卡的參數控制、狀態監視、信息存儲等功能。

為了實現動態重構,以監控計算機為主設備,通過CPCI總線將配置數據送到底層板卡上,并控制整個配置流程。主控FPGA作為配置數據的通道,與板卡FPGA1,FPGA2,DSP接口,并且設計了配置狀態機用于實現FPGA的配置時序。將不同模式的硬件配置文件存放在監控計算機硬盤中,通過監控軟件實時加載不同的模式配置文件,即可實現系統重構,完成測控功能切換。

3 FPGA動態配置

3.1 Xilinx VIRTEX 6系列FPGA配置方式介紹

現場可編程門陣列(Field Programmable Gate Array,FPGA)以其高度的靈活性以及豐富的I/O資源與內嵌模塊等優勢,在航天領域越來越廣泛的應用[2]。Xilinx公司根據FPGA是否能夠自己主動加載配置數據分為主模式、JTAG模式以及從模式[3]。主模式根據配置數據位寬和控制時序的不同又分為Master Serial,Master SPI,Master BPI?Up,Master BPI?Down,Master SelectMap等幾種接口。

主模式加載片外非易失性存儲器中的配置比特流,配置所需的時鐘信號由FPGA內部產生,且FPGA控制整個配置過程。在主模式下,FPGA上電后,自動將配置數據從相應的外存儲器讀入到FPGA內部SRAM中,實現內部結構映射。JTAG 模式主要用于調試,可將PC 中的比特文件流下載到FPGA中,斷電后丟失。

在JTAG模式下,配置時鐘為JTAG接口的TCLK,數據直接從TDI進入FPGA,完成相應功能的配置。從模式需要外部的主控設備(如處理器、微控制器或者DSP等)將數據下載到FPGA中,其最大的優點在于FPGA的配置數據可以放在系統的任何存儲部位,如:硬盤、FLASH、網絡等。

從模式根據配置數據的位寬不同又分為Slave SelectMap和Slave Serial兩種模式。在從模式下,FPGA 作為從屬器件,由相應主控設備器配置所需的時序,實現配置數據的下載。

通過設置FPGA的MODE引腳的值,可以改變FPGA的配置模式。在本設計中選用了并行從模式即Slave SelectMap來實現FPGA的動態配置。

3.2 FPGA動態配置設計實現

該模式的配置主要由以下信號進行控制:

PROGRAM_B:為低時復位芯片,復位后INIT_B變成低表示FPGA正在初始化配置存儲,當采樣到MODE引腳的值后,如果沒有發生CRC錯誤INIT_B將拉高,若發生CRC錯誤,則INIT_B為低。

RDWR_B:控制配置數據的方向,為高時從FPGA讀取配置數據,為低時向FPGA寫入配置數據。

CSI_B:片選信號為低時,使能SelectMap總線。在只有一片FPGA的情況下,可以將此引腳直接接地。

CCLK:配置時鐘。在VIRTEX 6系列FPGA中,CCLK最高[4]可以達到105 MHz。但由于受到PCB工藝布線等因素影響,過高的時鐘往往會受到信號過沖,建立保持時間等的影響,導致配置失敗。因此為了保證配置的可靠性在本設計中采用主控FPGA產生50 MHz時鐘輸出給待配置FPGA。

D[0∶7]:8 b配置數據信號。在Xilinx的ISE開發環境中,對FPGA的工程進行編譯,可以生成配置所需的不同二進制文件。FPGA 的配置文件有多種不同的格式,例如BIT,BRT,BIN,MCS,EXO,TEK,HEX等[5]。ISE軟件調用 Bit Gen 程序可直接生產BIT和BIN文件。由于BIN文件僅有配置數據無其他多余信息,因此在本設計中采用了BIN文件進行配置。

DONE:高有效,表示配置成功。

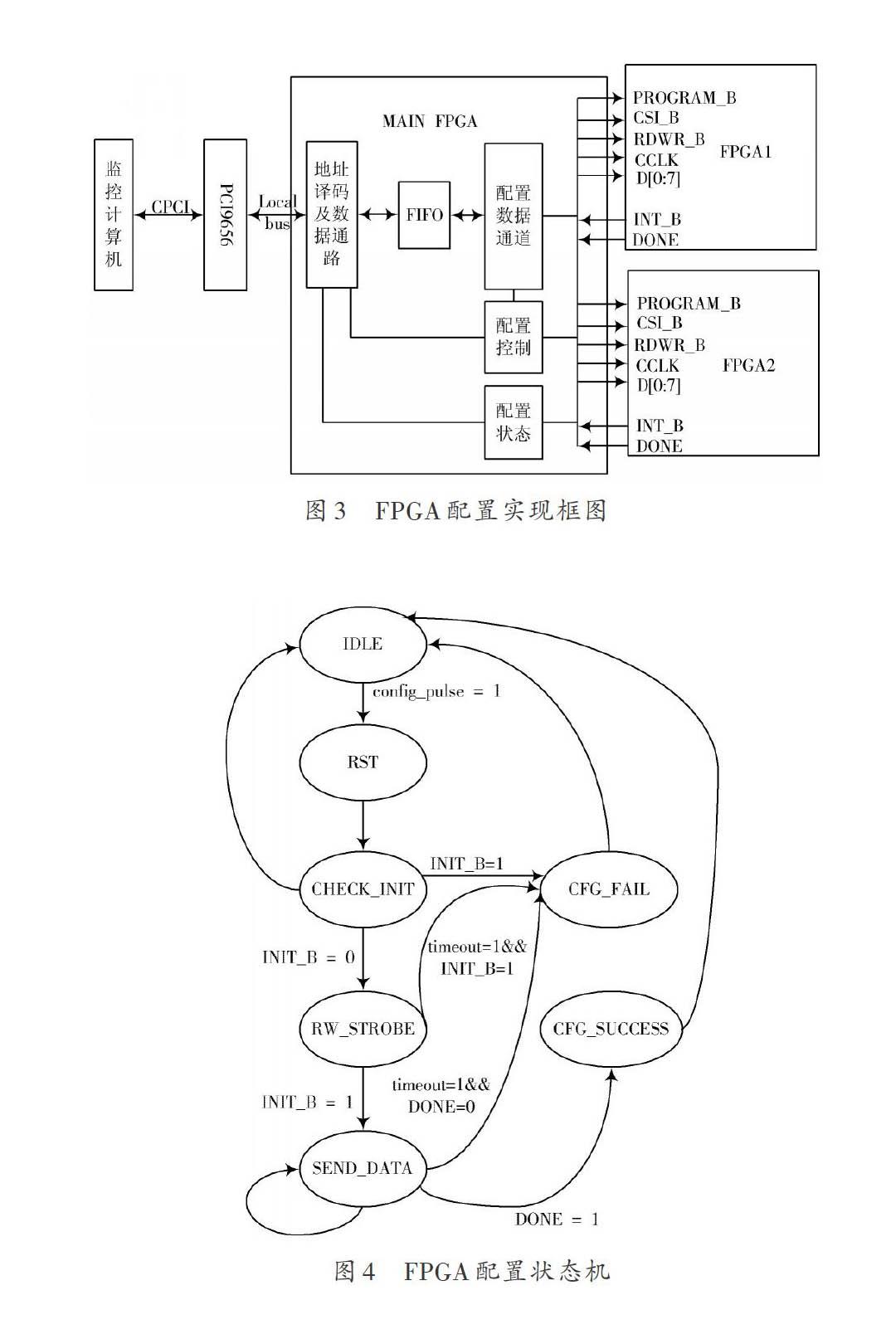

如圖3所示為主控FPGA中用戶邏輯的模塊劃分框圖及與片外FPGA的配置信號連接圖。地址譯碼及數據通路模塊實現與PCI9656的接口,對PCI總線的地址進行譯碼和數據傳輸控制。FIFO用于緩存配置數據。配置控制模塊實現動態配置的控制邏輯狀態機。配置狀態模塊把FPGA1和FPGA2的狀態上報到計算機。FPGA1和FPGA2所有需要配置的信號連接到主控FPGA的I/O引腳上。

當需要動態改變FPGA配置內容時,計算機將配置數據通過CPCI總線按字節把配置文件數據經過PCI9656寫入FIFO中。主控FPGA中的配置控制邏輯檢測到FIFO非空后,并判斷配置哪一塊FPGA后,讀取FIFO中的數據,并按照圖 2中配置模式的時序把配置數據連續寫入FPGA1或FPGA2中。配置成功后,被配置的FPGA將自動拉高DONE信號電平,此時計算機可通過讀取該信號的值來監測被配置FPGA的狀態,判斷是否配置成功。

為了實現圖2配置時序,在主控FPGA配置控制模塊中通過Verilog HDL代碼設計了具有圖4狀態轉換圖的狀態機[6]。

IDLE狀態:該狀態為初始狀態,等待總線配置命令。當需要進行模式切換時,監控計算機向映射到內存空間的CPCI指定地址寫入0,1,0產生開始配置的脈沖config_pulse。狀態機檢測到總線的開始配置脈沖后,進入RST狀態。

RST狀態:在該狀態下,主控FPGA拉低PROGRAM_B,被配置FPGA進入復位狀態。為了保證復位的有效性,復位時間[5]至少不低于250 ns。被配置FPGA復位以后,拉高PROGRAM_B,狀態機進入CHECK_INIT狀態。

CHECK_INIT狀態:在該狀態下通過檢測INIT_B信號判斷是否進行狀態轉換。若復位成功,被配置FPGA將清除用于配置的內部存儲,并拉低INIT_B。當狀態機檢測到INIT_B為低后,狀態進入RW_STROBE狀態。如果該狀態下INIT_B仍為高,表示配置失敗,進入CFG_FAIL狀態,結束配置。

RW_STROBE狀態:在該狀態下,判斷被配置FPGA的內部SRAM是否完成初始化,為下一步寫入配置數據做準備。當FPGA內部SRAM初始化完成并且沒有發生CRC錯誤時,INIT_B信號將變高。一旦狀態機檢測到INIT_B為高,主控FPGA拉低RDWR_B信號,進入SEND_DATA狀態。當內部計時器超過設定時間1 s,INIT_B還未變高,則進入CFG_FAIL狀態,結束配置。

SEND_DATA狀態:在該狀態下,主控FPGA完成將配置數據送入待配置FPGA的功能。若FIFO不為空,讀取FIFO中的配置數據,并將數據送入FPGA中。FIFO作為配置數據的通道需要被上層應用和配置邏輯監測空滿狀態。上層應用通過CPCI總線讀取FIFO的狀態,若FIFO數據半滿則需要向FIFO中寫入一部分配置數據塊。監控計算機由于在實際應用中有多個線程同時運行并且受到CPCI總線傳輸效率不高的因素影響,雖然采用了DMA傳輸方式,寫入FIFO的數據速率仍會低于50 MB/s的配置速率,因此會出現FIFO空的情況。若出現FIFO空,則需要拉高CSI_B信號,當FIFO中有配置數據之后才拉低CSI_B,保證配置數據的連續性。若監控計算機發生異常導致FIFO數據中斷,將進行超時判斷,超時后進入CFG_FAIL狀態,并結束配置。寫完配置數據后,檢測DONE信號,若為高則表示配置成功,進入CFG_SUCCESS狀態,結束配置。若檢測到DONE信號一直為低,則進入CFG_FAIL狀態,并結束配置。

CFG_SUCCESS狀態:前一狀態若檢測到DONE信號為高,則進入該狀態,表示本次配置成功,并在下一個時鐘周期,進入初始IDLE狀態。

CFG_FAIL狀態:配置超時或者數據傳輸異常,DONE信號無法拉高等情況下,都進入該狀態,表示配置失敗。

4 TMS320C6455DSP動態加載

4.1 TMS320C6455 DSP概述

TMS320C6455 DSP是TI公司的一款高性能DSP,不僅具有高速的數據運算能力,還有豐富的外部接口,如外部存儲器EMIF接口,高速串行接口Serial RapidIO,PCI接口,三速以太網MAC控制器等[7]。

TMS320C6455 DSP內部有豐富的存儲資源,它的L2級RAM存儲容量達4 Mb/s,分配的內存地址范圍為0x00800000~0x009FFFFF。為了滿足更多應用對內存的需求,可以通過DDR2控制接口或EMIFA接口擴展系統的內存。

4.2 基于EMIFA接口的啟動過程

DSP的啟動是將程序和數據段加載到其內部存儲空間,并且初始化內部寄存器的過程。通常啟動模式主要有:NOBOOT模式、主機(HPI/PCI接口)模式、EMIFA模式、主I2C模式、從I2C模式、SRIO模式等模式。本設計中采用了EMIFA片外ROM啟動模式。TMS320C6455 DSP的EMIFA接口能與各種外部設備接口,如SRAM,FIFO,ROM,FLASH等。EMIFA對應的DSP的地址空間分為4片空間,分別對應的片選信號CE2~CE5,可擴展的地址空間達1 GB。

上電復位后,DSP通過DMA/EDMA控制器,自動將存有程序代碼的片外存儲器中1 KB數據搬移到起始地址為0x800000的內存中[8]。搬移完成后,DSP將從該地址執行程序。通常在這段1 KB程序里存放為Bootloader程序,Bootloader程序將保存在片外存儲器中的其他程序數據搬移到DSP L2 RAM空間中,并在搬移完成后讓DSP跳轉到程序起始處開始執行,此時DSP完成整個啟動過程。

4.3 DSP動態配置的實現

如圖1所示,DSP的EMIFA CE3的地址數據等控制信號通過主控FPGA與雙口RAM和FLASH連接。在板卡上電的初始狀態下,DSP的EMIFA的CE3信號線通過MAIN FPGA與FLASH連接。當需要進行功能切換時,計算機首先通過CPCI總線將DSP的程序二進制文件寫入雙口RAM中。然后控制主控FPGA將EMIFA CE3的數據、地址、控制等信號切換到雙口RAM上。為了讓DSP重新啟動,監控軟件向主控FPGA中復位寄存器寫入1,產生復位DSP的脈沖。DSP復位之后,重新開始啟動過程,但通過EMIFA CE3地址空間訪問的內存將不再是FLASH,而是片外雙口RAM。DSP加載雙口RAM中的程序數據后,實現DSP功能的切換。由于片外雙口RAM比FLASH具有更高的工作時鐘,這種DSP的啟動方式,相對于FLASH加載的方式,不僅可以減少燒寫FLASH的環節,縮短DSP的啟動時間,而且可通過監控軟件的人機界面隨時更改DSP加載的程序內容,具有很大的靈活性。

5 結 語

本系統利用CPCI總線傳輸不同的配置文件實現系統的可重構,具有簡單,易于開發的特點。通過應用軟件實際測試,整板(包括2片FPGA,1片DSP)的重構時間不超過2 s。CPCI總線結構動態重構系統具有很大的優越性,不僅數據傳輸速率高,資源利用率高,減小了系統規模功耗,而且可以對不斷變化的環境迅速適配。本設計已應用于實際工程中,并取得了良好的效果。

參考文獻

[1] BUDRUK Ravi, SHANLEY Tom, ANDERSON Don. PCI Express系統體系結構[M].北京:電子工業出版社,2005.

[2] 王文華,韓雙麗,張宇.航天應用FPGA配置可靠性研究[J].空間科學學報,2011,31(1):106?111.

[3] Xilinx Technology Inc. Virtex?6 FPGA configuration user guide [EB/OL]. (2012?09?11) [2015?04?20]. http://www. xilinx.com/support/documentation/user_guides/ug360.pdf.

[4] Xilinx Technology Inc. Virtex?6 FPGA data sheet: DC and switching characteristics DS152 [EB/OL]. (2011?04?01) [2015?04?20]. http://www.xilinx.com/support/documentation/data_

sheets/ds152.pdf.

[5] 孟龍,郄志鵬,朱江,等.基于CPCI總線的FPGA加載設計[J].通信技術,2013,46(5):127?129.

[6] Xilinx Technology Inc. A CPLD?based configuration and revision manger for Xilinx platform flash PROMS and FPGAs [EB/OL]. (2005?01?19) [2015?04?22]. http://www.xilinx.com/support/documentation/application_notes/xapp693.pdf.

[7] Texas Instruments Inc. TMS320C6455 fixed?point digital signal processor [EB/OL]. (2012?03?23) [2015?04?10]. http://www.ti.com/lit/ds/symlink/tms320c6455.pdf

[8] Texas Instruments Inc. TMS320C6000 tools: vector table and boot ROM creation[EB/OL]. (2004?04?20) [2015?04?11]. http://www.ti.com/lit/an/spra544d/spra544d.pdf