一種數字遙測接口容差測試方法及實現

安衛鈺 韓笑冬 王志富

(中國空間技術研究院通信衛星事業部,北京 100094)

一種數字遙測接口容差測試方法及實現

安衛鈺 韓笑冬 王志富

(中國空間技術研究院通信衛星事業部,北京 100094)

通過對衛星常用數字接口電路及其傳輸特性分析,研究了影響接口傳輸性能的時延、幅值和上升沿特性,提出了一種數字遙測傳輸接口容差測試方法并研制了測試設備,可以對數字信號進行時延、電平幅值和上升沿的拉偏,實現了接口容差指標的定量測試。通過對衛星單機設備接口拉偏試驗,驗證了測試方法的正確性和測試設備的實用性。

衛星;數字接口;容差;測試方法

1 引言

衛星從研制到發射,須要經過多個階段的測試驗證,由于各階段的環境溫度和電纜規格不同,會使單機設備間的數字傳輸接口發生不匹配現象,影響遙測遙控信息的正常傳輸。尤其是設備熱試驗期間,由于環境溫度的劇烈變化,信號的傳輸特性隨之變化,時序競爭現象時有發生,使單機間無法正常通信,影響衛星完成任務。

對接口電路容差指標進行分析和測試,提高接口在極限環境下的工作性能,可以有效地保證整星信息流的正常傳輸。國內外均對電路容差進行過研究分析,通過提取關鍵特性參數,使用仿真工具分析系統累積誤差,然后運用數字化技術進行迭代設計,提高系統的設計裕度[1-3]。但是這些方法只適用于設計階段,無法對硬件進行實測,由于仿真工具的理想化,實際電路與設計值存在偏差。本文提出了一種對數字遙測電路容差定量測試的方法,適用于遙測視頻信號接口和RS422差分接口,通過硬件設備對電路關鍵特性參數進行拉偏測試,模仿多種工況下星上設備單機接口的傳輸性能,可在整星集成測試前發現潛在的接口不匹配現象。

本文對容差測試機理進行了研究,分析了傳統容差分析方法的利弊,論述了接口容差測試設備的實現原理和關鍵技術,通過該設備對星上單機設備的驗證試驗,論證了測試方法的有效性。

2 容差分析與測試原理

目前,通用的容差分析方法是計算各種工況下電路的性能參數、輸入量和元器件參數之間的關系,使用仿真軟件對電路進行最壞情況分析或蒙特卡羅分析[4],求出電路輸出性能參數的偏差范圍,找出對電路敏感度影響較大的參數并進行控制,使電路滿足要求。如性能參數較差則修改電路設計,重新進行容差分析直到滿足指標要求。但是單機一旦生產完成后,缺少容差指標驗證方法,由于仿真工具中元器件的參數與實際值會有偏差,導致單機實際狀態與仿真設計的理想電路有差異,在環境惡劣情況下會發生接口不匹配現象。

為了實現對衛星數字接口的容差測試,本文提出了容差定量測試的方法,須要研制測試設備對特定接口電路進行最壞情況試驗。對模擬數字遙測傳輸信號,進行時延拉偏、電平拉偏和上升沿拉偏,時序拉偏精度20ns,幅值拉偏精度50mV,上升沿拉偏精度100ns,接口正常工作時拉偏參數的上下限即為接口的容差值。通過多路信號比較分析,可以對多路信號之間的時序關系進行測試。

以圖1所示的一種典型的數字遙測傳輸接口時序為例。門控信號有效時在時鐘的下降沿采集數據信號,理想情況下門控和時鐘信號的上升沿是對齊的,實際情況下兩個信號到來時間并不是對齊的,信號的上升沿、幅值也略有不同,不同的工況會使數據采集電路進入不同的邏輯狀態,引起數據傳輸的不穩定。容差定量測試方法可以對電路進行最壞情況試驗,使被測電路處于溫度、信號電壓、上升沿和延時等主要因素均為上下限的條件下,測試電路性能參數偏差。

3 測試設備實現方案

3.1 系統方案

測試設備是基于現場可編程門陣列(FPGA)和數字信號處理器(DSP)相結合的嵌入式硬件平臺[5],設計了專用時延、幅值和上升沿的拉偏電路,利用上位機(PC機)軟件控制電路拉偏參數。

為了實現對接口信號的拉偏,須要對信號進行多級處理。在FPGA中通過內部處理邏輯生成標準時序信號,并接收DSP傳送的拉偏設置參數,根據時延拉偏參數對多路信號的時序關系進行調整,以時鐘同步信號為基準,調整其它信號與時鐘同步信號之間的延時量(可超前或滯后),FPGA通過外部輸出接口將信號送出,此時信號幅值為3.3V。接著對信號進行幅值轉換,達到與星上設備接口匹配和幅值拉偏的目的。最后,對接口信號的上升沿時間進行調整,通過可變阻容網絡實現。測試設備原理如圖2所示,主要由上位機、控制管理模塊、信號幅值轉換模塊、阻容網絡模塊、鋰電池、精密時鐘基準源等組成。

上位機與DSP通過隔離串口總線通信,它提供用戶操作界面,用于設置系統工作模式、拉偏參數、顯示接收數據等功能,分為配置和工作模式。運行在配置模式時,進行接口類型的選擇和拉偏值設置,將配置信息發送給控制管理模塊,控制管理模塊響應并回傳,上位機對回傳數據進行判斷,正確后發出開始執行指令。運行在工作模式時,進行數據雙向收發,同時接收控制管理模塊傳來的遙測數據和向控制管理模塊發送指令數據。

3.2 時延拉偏方法

控制管理模塊實現系統的核心功能,使用FPGA模擬數字量接口時序并對不同信號之間的延時關系進行調整;DSP完成與上位機的通信,將配置信息發送給FPGA處理。FPGA使用XILINX公司Spartan 6芯片XC6SLX100,外部時鐘采用穩定度為1×10-6的恒溫晶振[6],頻率為50MHz。

接口的時延拉偏在FPGA中實現,FPGA內部采用級聯方式:第一級根據具體的通信協議,為信號設置狀態機,產生時鐘信號與門控信號對齊的時序。時鐘由FPGA內部的直接數字式頻率合成器(DDS)產生,頻率控制字位寬為32bit,按照上位機設置的時鐘頻率,計算出DDS模塊的頻率控制字,得到規定頻率的時鐘信號。門控信號的周期為1024個時鐘周期,高電平持續時間為第M到第N個時鐘周期(M和N可由上位機設置),對時鐘從0開始計數,門控信號狀態機初始態輸出為0;計數達到M時,在時鐘的上升沿門控轉入輸出為1狀態;計數達到N時,在時鐘的上升沿門控轉入輸出為0狀態;計數達到1024后,對計數器清零,門控轉為初始態;繼續對時鐘進行計數,產生周期性的門控信號。

第二級在每路信號后面設置延時器,FPGA采用50MHz頻率,內部設置最小延時單元為20ns,計算信號延時需要的最小延時單元個數,當上位機設置門控信號超前時鐘信號時,將時鐘信號延時相應的節拍數;當上位機設置門控滯后時鐘時,將門控信號延時相應的節拍數。因此,信號時延的精度可達到20ns。

3.3 幅值拉偏電路

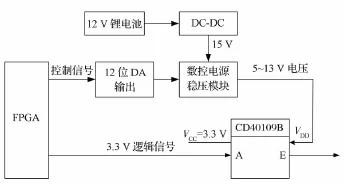

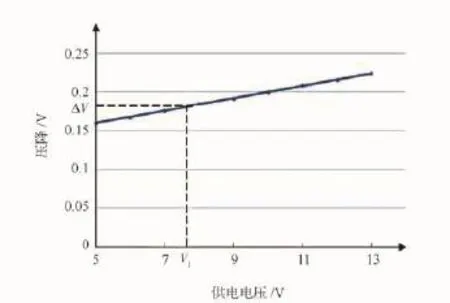

星上接口電路分為單端接口和差分接口。針對單端接口,使用數字控制電源[7]對CD40109B電源轉換芯片的輸出端供電電壓進行調節,實現方式如圖3所示,其中VCC代表芯片輸入端供電電壓,VDD代表輸出端供電電壓。數控電源提供5~13V電壓的精確調節功能,12位數模轉換(DA)控制器對數控電源進行控制,控制分辨率可以達到15V/4096=3.66mV。通過改變輸出端的電源電壓可以實現輸出信號的幅值變化,但是由于限流電阻和芯片內部場效應管特性,輸出信號相對供電電壓存在壓降,為此測試了不同供電電壓下輸出信號的壓降值,繪制了壓降補償曲線,如圖4所示。將壓降和其對應的補償值制成表格存入DSP存儲區,DSP軟件調用此表對接收到的上位機設置值進行補償,例如,接收到的信號電壓設置值為V1,查詢表格得到補償值ΔV,將補償后的電壓值V1+ΔV傳輸給FPGA,FPGA據此設置供電電壓值。

通過對幅值拉偏設置進行補償,提高了幅值拉偏的精度。由于電源紋波和地線雜波的干擾,經測試,設備的電壓幅值輸出精度為50mV。

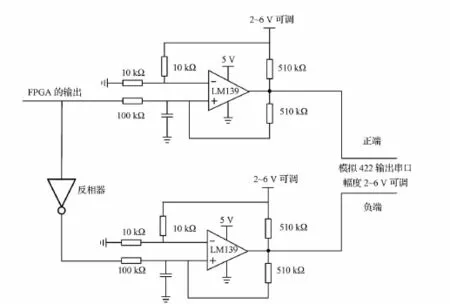

星上差分電路主要采用422差分驅動芯片,芯片正常工作供電電壓范圍為4.5~5.5V,僅改變芯片電壓無法實現大范圍的幅值拉偏,所以提出了一種專用的改變差分電平輸出的方法,如圖5所示。FPGA輸出的邏輯電平一路經過比較器輸出,另一路經過反相后再經過相同的比較器電路,實現2~6V的幅值輸出范圍。

圖3 單端接口拉偏方式Fig.3 Deflection method of single circuit

圖4 壓降補償曲線Fig.4 Compensation graph of voltage

圖5 差分電路拉偏方式Fig.5 Deflection method of difference circuit

3.4 上升沿拉偏電路

星上單機對上升沿時間拉偏需求為0.1~100.0μs,通過一種可變阻容網絡來實現信號上升沿的改變。使用繼電器開關控制接入電路中的電阻和電容值,調整電路的時間常數,可以改變輸出信號的上升沿時間,如圖6所示。本設計中上升沿時間定義為信號幅值從10%到90%之間的時間間隔,為2.2倍的時間常數。

圖6中,設計了4組電阻和4組電容單元,每組電容單元均由一個電容和一個可變電容器并聯組成,可變電容調節方式為手動調節。A組為精調電容單元,電容調節范圍(C1+C2)為20~110pF,調節精度為0.1pF,配合4組電阻,可實現的上升沿調節范圍為0.02~1.36μs;B、C、D組實現大范圍的上升沿參數調整,使用的可調電容器(C4,C6,C8)范圍為100~1000pF,調節精度為10pF,通過繼電器的接合實現了800~8500pF的容值調整范圍,配合4組電阻,上升沿調節范圍為0.88~105.09μs。因此,滿足了星上單機拉偏需要的上升沿范圍。

由于B、C、D組的可變電容調節精度較差,在進行較大時間上升沿精調時,須接入A組電容單元。使用示波器觀察輸出信號的上升沿,手動調節C2旋鈕改變電容值,待上升沿滿足精度要求。上升沿時間最長(100μs),拉偏精度最差,理論計算誤差小于10ns,但是由于電路板的寄生感抗、容抗和示波器的測量誤差,可實現的拉偏精度優于100ns。

圖6 接口邊沿拉偏示意圖Fig.6 Circuit of interface rise time deflection

3.5 星地接口安全設計

接口容差的硬件測試方法考驗接口在極端情況下的傳輸性能,會帶來一定的測試風險,因此測試系統的可靠性和安全性設計是重要內容,也是測試方法能否最終得到應用的有效保證[8-9]。安全設計須要考慮限流限壓保護和接口隔離。在電源輸出端采用固態限流器進行限流,在信號輸出端并聯穩壓二極管進行限壓,保證不會有過流過壓信號進入星上設備。

供電和接地是接口隔離設計的主要考慮因素。本設計采用12V鋰電池供電,避免了將市電220V高電壓及其地線干擾引入星上設備的風險,并由隔離電源將12V電壓轉換為設備內部所需電壓。計算機和功能模塊之間通過磁耦隔離芯片通信[10],可以實現2500Vrms的有效絕緣電壓。

通過以上設計可以對接口電路進行保護,保證測試系統與星上設備的隔離,使得測試系統發生故障時不會影響到星上設備。

4 容差測試方法驗證

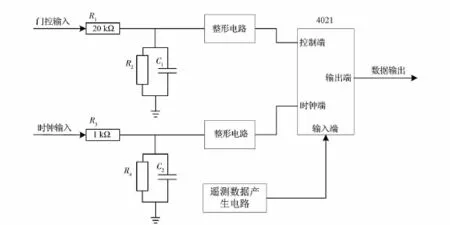

為了驗證本文提出的接口容差測試方法,在某衛星型號單機設備上進行了應用。針對該單機的遙測數字量傳輸接口,分別通過蒙特卡羅仿真方法和硬件測試方法分析容差指標,接口時序關系如圖1所示,接口電路示意如圖7所示,該單機接收門控和時鐘信號,輸出遙測數據。

圖7 遙測傳輸接口電路示意圖Fig.7 Circuit of telemetry transmission interface

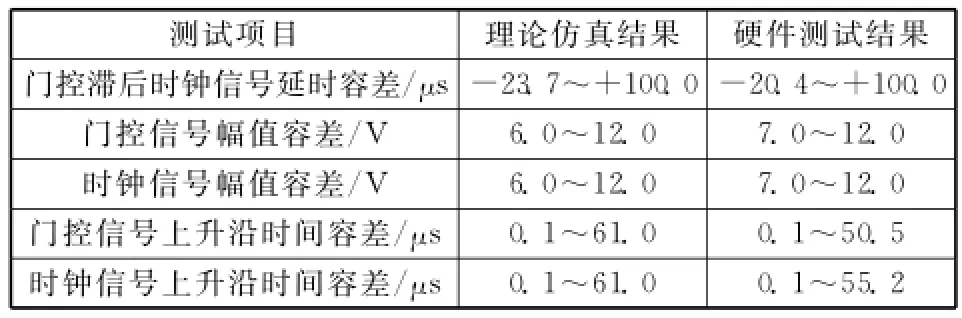

使用Multisim軟件對電路進行仿真分析,使用接口容差測試設備對實際電路進行測試,分別得到了接口的容差指標,分析對比見表1。由表1可見,理論仿真結果和電路實測結果存在誤差,對接口電路按本文方法進行硬件實測是有必要的。

接口容差測試設備對多個衛星型號的單機設備進行了驗證試驗,試驗結果表明:時序延時、幅值和上升沿條件的惡化,均會影響信號傳輸,在真空高低溫情況下,容差指標會發生相應偏移。通過接口容差測試系統驗證,滿足容差指標要求的單機設備,在整星總裝測試中均未發生接口不匹配現象。

表1 理論分析與硬件測試結果對比Table 1 Contract of theory analyze and hardware test

5 結束語

本文分析了對衛星數字傳輸接口進行容差測試的必要性,傳統的電路容差仿真方法存在較大誤差,因此提出了對接口容差進行硬件測試的方法,并研制了相關測試設備。遙測接口容差測試設備基于嵌入式平臺實現,采用最壞情況試驗法,對遙測信號進行大范圍和高精度的拉偏測試。通過理論分析與硬件測試方法對比,證明了硬件測試方法的有效性。本測試方法已實際應用于衛星單機間遙測接口設計,有效避免了接口不匹配現象,并對衛星其它數字接口容差測試具有推廣應用的意義。

(

)

[1]Isabel Gonzalez,Ismael Sanchez.Statistical tolerance synthesis with correlated variables[J].Mechanism and Machine Theory,2009,44(6):1097-1107

[2]尹峰,王巍,梁濤.基于關鍵特性的數字化容差分配技術研究[J].航空制造技術,2011(22):53-56 Yin Feng,Wang Wei,Liang Tao.Research of digital tolerance distribution technology based on key characteristics[J].Aeronautical Manufacturing Technology,2011(22):53-56(in Chinese)

[3]李紅,付興武.基于容差分析的電路參數中心值設計研究[J].現代電子技術,2005,28(23):88-90 Li Hong,Fu Xingwu.Research of central value design of circuit parameter based on tolerance analysis[J].Modern Electronics Technique,2005,28(23):88-90(in Chinese)

[4]劉維罡,沈頌華,駱明珠.航空電源系統的容差分析及仿真研究[J].測控技術,2007,26(6):79-82 Liu Weigang,Shen Songhua,Luo Mingzhu.Circuit tolerance analysis and simulation study for aviation power system[J].Measurement &Control Technology,2007,26(6):79-82(in Chinese)

[5]李楊,孫玉國,金鑫.基于嵌入式邏輯分析儀的FPGA測試[J].儀器儀表學報,2006,27(6):2372-2373 Li Yang,Sun Yuguo,Jin Xin.FPGA signal extraction based on embedded logic analyzer[J].Chinese Journal of Scientific Instrument,2006,27(6):2372-2373(in Chinese)

[6]盧祥弘,陳儒軍,何展翔.基于FPGA的恒溫晶振頻率校準系統的設計[J].電子技術應用,2010(7):101-104 Lu Xianghong,Chen Rujun,He Zhanxiang.The design of frequency calibration system for OCXO based on FPGA[J].Application of Electronic Technique,2010(7):101-104(in Chinese)

[7]胡輝,楊花雨.基于單片機控制的數控電源設計[J].商丘職業技術學院學報,2013,12(5):60-61 Hu Hui,Yang Huayu.Design of digital power source based on single chip microcomputer[J].Journal of Shangqiu Vocational and Technical College,2013,12(5):60-61(in Chinese)

[8]焦榮惠,李砥擎,陳粵.一種衛星低頻接口自動測試系統[J].航天器工程,2014,23(4):115-119 Jiao Ronghui,Li Diqing,Chen Yue.An automatic test system of satellite low frequency interface[J].Spacecraft Engineering,2014,23(4):115-119(in Chinese)

[9]崔海濤,于曦.復雜電磁環境下RS422接口保護電路的實現[J].航空計算技術,2011,41(6):119-124 Cui Haitao,Yu Xi.Design and achievement for a kid of protection electrocircuit to RS422interface[J].Aeronautical Computing Technique,2011,41(6):119-124(in Chinese)

[10]鄭采君,肖原.新型磁耦合隔離電路設計[J].電子設計工程,2011,19(4):162-166 Zheng Caijun,Xiao Yuan.Design of new magnetic coupling isolating circuit[J].Electronic Design Engineering,2011,19(4):162-166(in Chinese)

(編輯:李多)

A Tolerance Test Method for Digital Telemetry Interface and Its Implementation

AN Weiyu HAN Xiaodong WANG Zhifu

(Institute of Telecommunication Satellite,China Academy of Space Technology,Beijing 100094,China)

A test method of digital telemetry interface is introduced by analyzing the character of common interface circuit and researching the schedule,voltage and rise time of signal transmission.Test equipment is invented.It has the capability of producing schedule deflection,voltage deflection and rise time deflection.So,it can measure the interface tolerance quantitatively.A deflection test of satellite units verifies the validity of the test method and the practicality of the equipment.

satellite;digital interface;tolerance;test method

V416

A

10.3969/j.issn.1673-8748.2016.02.019

2015-09-10;

2015-12-29

國家重大航天工程

安衛鈺,男,碩士,工程師,研究方向為航天器總體設計。Email:anweiyuan@126.com。