基于堆棧遍歷的智能斷電控制系統設計

黃冠華,陸興華

(廣東工業大學華立學院,廣州 511325)

基于堆棧遍歷的智能斷電控制系統設計

黃冠華,陸興華

(廣東工業大學華立學院,廣州511325)

摘要:通過設計電源的智能斷電控制系統,避免過載導致電器設備的損壞。提出一種基于堆棧遍歷的智能斷電控制系統設計方法。系統主要包括了預處理機動態增益控模塊、放大器模塊、智能斷電濾波模塊和電源模塊。設計了時鐘信號驅動電路、時鐘電路、復位電路和動態增益控制電路,在Visual DSP++ 4.5軟件開發環境下進行系統軟件開發,并進行了仿真實驗。

關鍵詞:智能斷電控制;電壓;堆棧;系統設計

[1]

ZHENJian-jun,ZHANGYi,HUGuang-bo.Researchoninductivepowertransmissiontechnologybasedonspiralplanarcoil[J].ElectricalAutomation,2014,36(2):78-80.

[5]張睿.基于多徑PID控制的網絡終端動態干擾監測設計[J].科技通報,2014,30(6).

ZHANGRui.DesignofnetworkterminaldynamicmonitoringbasedonmultipathPIDcontrol[J].BulletinofScienceandTechnology,2014,30(6).

[6]李劍,馬新春,陳星志,等.基于物聯網的電機節能管理系統設計[J].電子設計工程,2015(18):27-29.

LIJian,MAXin-chun,CHENXing-zhi,etal.Designofmotorenergymanagementsystembasedoninternetofthings[J].ElectronicDesignEngineering, 2015(18):27-29.

[7]丁青青,魯偉,徐長波,等. 三相并聯混合有源電力濾波器的無源控制策略[J].電機與控制學報,2014,18(5):1-6.

DINGQing-qing,LUWei,XUChang-bo,etal.Passivity-basedcontrolofathree-phaseshunthybridactivepowerfilter[J].ElectricMachinesandControl,2014,18(5):1-6.

(本文編輯:嚴加)

電力與電源的控制系統是一種高精度高可靠性的控制系統,特別是電力控制系統中的電源斷電控制系統,是保障整個電力系統安全可靠運行的關鍵。通過設計電源的智能斷電控制系統,避免過載導致電器設備的損壞。隨著科技技術的發展和現代集成化電子元器件的不斷革新,采用集成DSP數字處理芯片,結合嵌入式計算機控制方法,進行電源的斷電控制成為未來智能斷電控制系統發展的趨勢,隨著對電力精確控制提出更高的要求,研究智能斷電控制系統優化設計方法具有重要意義[1]。

智能斷電控制系統工作原理是通過輸出電脈沖信號實現對過載峰值電壓的量化分析,傳統的斷電控制系統設計采用單一道址計數方法進行斷電控制,當達到器件所能承受的最高負荷時進行智能斷電,該方法受到分離元件工作溫度的影響較大,控制性能不好。對此,相關文獻進行了改進設計[2-3],其中,文獻[4]提出一種基于分散DCS控制的智能斷電控制系統設計方法,基于模塊化設計思想,采用ADSP-BF537控制電源智能斷電,通過CAN通信模塊設計進行峰值電壓和峰值電流的判斷,實現斷電控制,但該控制方法的抗干擾性能不好,避免了溫漂現象。文獻[5]提出一種基于交流耦合誤差補償的智能斷電控制方法,對斷電脈沖采用緩沖寄存方法,在緩沖區設置成雙緩沖,提高斷電的準確度,但該方法需要CAN總線發送的遠程幀,導致遠程控制性能不好。

針對這些問題,本文提出一種基于堆棧遍歷的智能斷電控制系統設計方法,首先進行了斷電控制系統的總體設計和性能參數指標描述,然后進行了系統的硬件設計和軟件設計,最后通過系統仿真實驗進行了性能測試和驗證,仿真實驗表明,采用該方法具有較好的控制性能,展示了較好的應用價值。

1智能斷電控制系統總體設計和模塊分析

1.1智能斷電控制系統總體設計

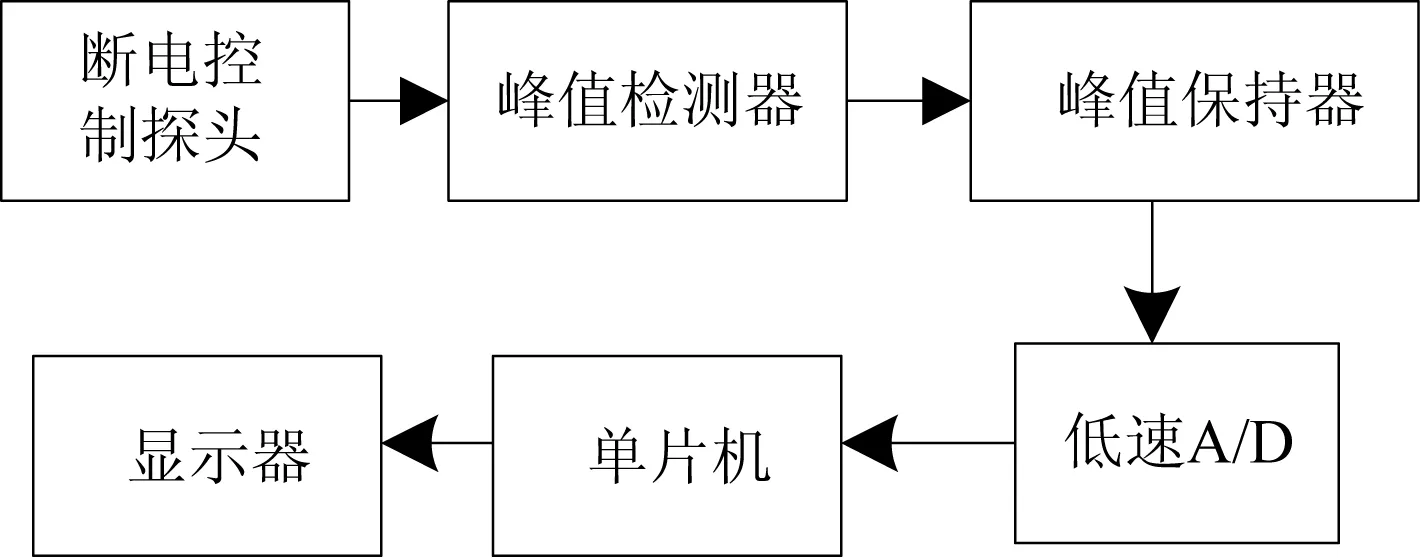

智能斷電控制系統是采用電壓脈沖探頭對電源的電脈沖信號進行檢側,檢測到脈沖峰值后進行能譜測量,先通過VXI總線驅動的高速電壓脈沖檢測器進行數據的A/D轉換,基于模擬信號預處理進行斷電信息的采集和控制[6],通過電流傳感器采集電流信號,采用AD9225設計智能斷電控制系統的時鐘電路,峰值保持器將電源的電壓峰值鎖止在低速A/D采樣端口,當電源收集到一個斷電脈沖后,進行循環堆棧尋址,對應單片機內存加1,最后把斷電信息通過人機交互實現信息顯示。

系統總體工作流程如圖1所示。

圖1 智能斷電控制系統總體工作流程

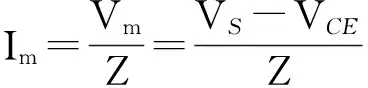

在圖1中,A/D轉換器前通過CAN總線發送短電控制脈沖,在VisualDSP++ 4.5軟件中[7],通過小型化、低功耗的低速A/D將SP內部緩沖額短短峰值電壓進行量化,轉為數字信號,過D/A調節高壓放大倍數,增加驅動能力,采用Aeroflex公司發布3280系列高端邏輯芯片控制中間件配置,在上一個緩沖區中,設計DC-DC電源轉換模塊、PLC可編程邏輯控制,此時智能斷電控制系統的整流電路的放大倍數為:

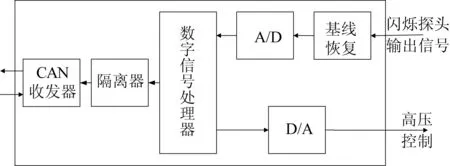

智能斷電控制系統的D/A轉換器輸出的電壓阻抗,利用匹配網絡來控制系統功放管內阻,進行智能斷電控制,智能斷電控制系統的總體設計框圖如圖2所示。

圖2 智能斷電控制系統的總體設計框圖

由圖2可見,智能斷電控制系統主要包括了預處理機動態增益控模塊、放大器模塊、智能斷電濾波模塊和電源模塊。下面分別對各個模塊的運行參量和原理進行分析。

1.2斷電控制系統的模塊分析

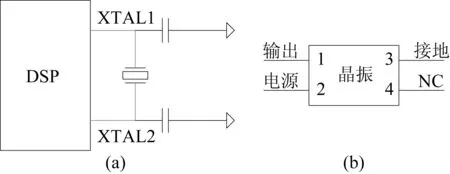

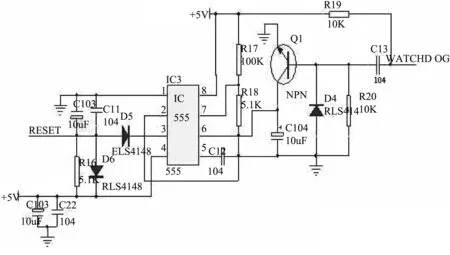

智能斷電控制系統的數據采集與處理系統是整個系統設計的關鍵,在智能斷電控制的DSP系統中,通過外部晶體配合電壓脈沖進行時鐘信號的驅動,得到智能斷電控制系統的時鐘信號驅動電路如圖3所示。

圖3 智能斷電控制系統的時鐘信號驅動電路

其中,VCE為A/D芯片的采樣降,與智能斷電控制系統的電流大小有關,VCE隨晶振的供電電源的電壓而增大。在不會影響晶振時,VCE一般在10V左右(運放手冊可查),采用堆棧循環遍歷原理對斷電控制電路進行循環堆棧控制,得到輸出的導納及阻抗參數分別為:

(1)

(2)

(3)

(4)

(5)

(6)

在智能斷電A/D轉換控制中,根據串并聯復合匹配進行斷電控制系統的特征采樣,得到智能斷電控制系統的設計過程描述如下:

(1)采用電容進行交流耦合控制,阻抗值G、B和堆棧循環控制阻抗為SvL,電容充電完畢后,確定GX值。

(2)輸入信號的平均幅度,指定φX值(如φX≤20°),進行電荷脈沖堆積,按式(1)計算值。

(3)由式(2)計算BL2值,當脈沖頻率較低時由式(3)、式(4)求R、ZX。

(4)假設V代表耦合電容,由式(4)確定ZLC值。

(5)由式(5)確定L1、C值。L1、C值需要在各頻率點進行循環堆棧遍歷控制,隨參數不斷變化,直到各點的cosφXi均滿足要求,當高端DI大時,抑制了基線漂移。

(6)計算PL、PD。實現智能斷電控制。

2系統設計與實現

2.1系統硬件設計

在智能斷電控制的總體設計和原理分析的基礎上,進行系統硬件設計。系統設計主要是對智能斷電控制系統的時鐘電路設計和控制電路設計,采用16位定點DSP內核進行式中電路控制,使用有源晶振。

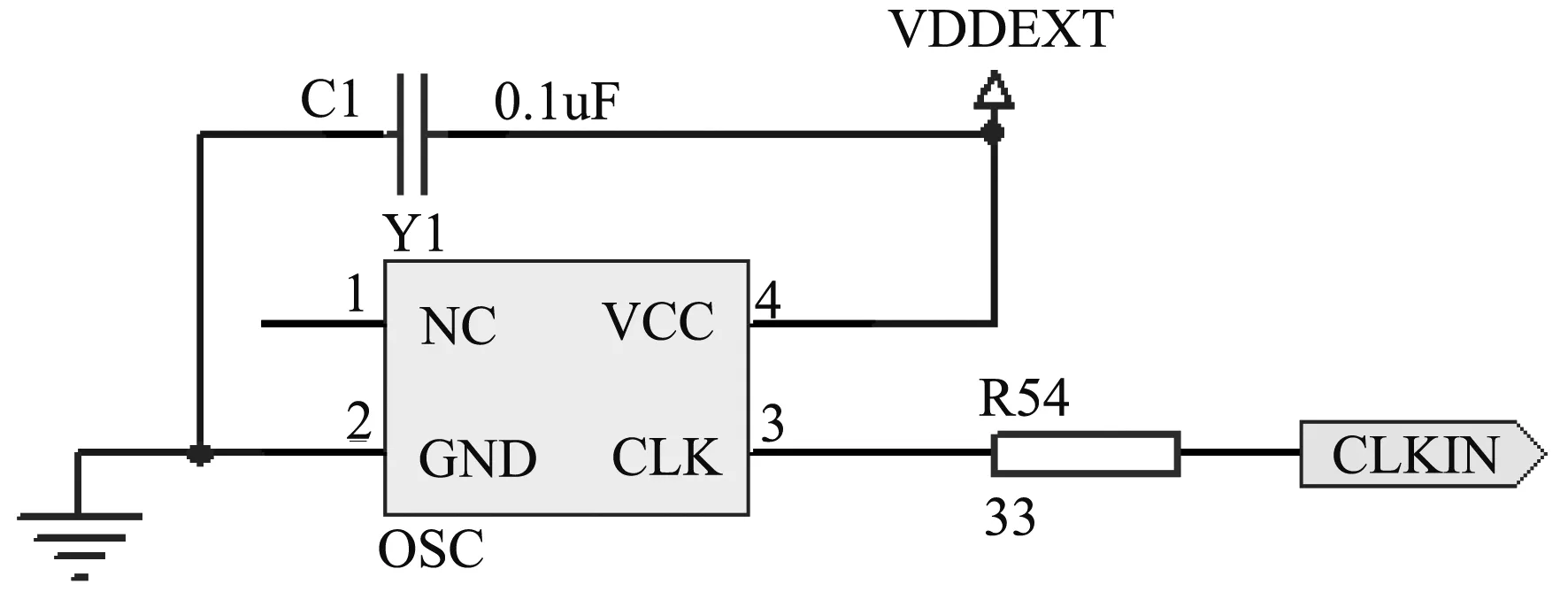

采用ADSP-BF537的內核,經24倍頻后形成103 838Hz時鐘電路內核,從串行的TWI存儲器引導,采用串行的SPI存儲器引導數據加載到DSP中,得到智能斷電控制系統的時鐘電路如圖4所示。

圖4 智能斷電控制系統的時鐘電路

為了提高斷電系統的時鐘控制性能,在電源入口處放1個10~100μF的晶振電容,在時鐘電路的末端要放1個0.1μF的電容抑制低頻干擾,布線應盡可能的短發射功率可以小一點,允許相位角適當大一點,在時鐘控制電路中產生EMI輻射,引起阻抗變化,本文設計的智能斷電控制系統具有VCC檢測功能,設計獨立的看門狗電路,在看門狗輸出為低電平時進行電壓復位,確保DSP系統中電路穩定,復位電路采用分立元件構成,當VCC不足3.3V時進行看門狗復位,本文設計的智能斷電控制系統的復位電路原理圖和芯片接口圖如圖5所示。

在復位電路設計的基礎上,進行程序加載電路設計,實現對智能斷電控制系統的動態增益控制模,智能斷電控制系統的動態增益控制的準確度穩定在±1/2LSB,IO電源(3.3V),采用10、0.1、0.001μF的電容并聯進行功率補償、CCDF功率,采樣時鐘由CLKBUF給出,第二級選用VCA810,工作電壓±1.5V,DG3301在3.3V到5V的電平轉換,在MAX7425的前級采用數字地和模擬地進行直流偏置控制,通過SCSI-68反饋動態增益控制雙端口RAM,通過0電阻單點相連,實現對智能斷電控制系統的動態增益電路設計,智能斷電控制系統的動態增益模塊如圖6所示。

圖6 智能斷電控制系統的動態增益模塊

智能斷電控制系統的高壓部分由電壓信號控制,在VisualDSP++ 4.5軟件開發環境下進行系統設計和調試,軟件設計部分描述如下。

2.2智能斷電控制系統的軟件設計

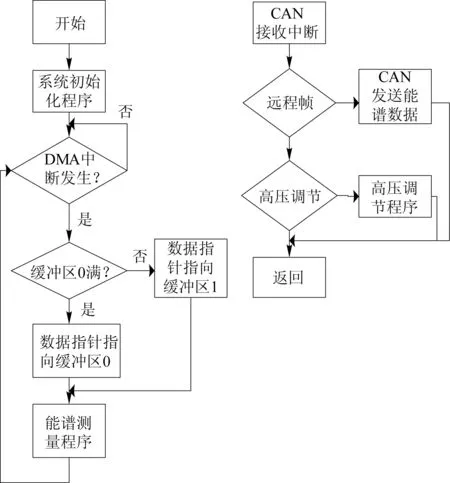

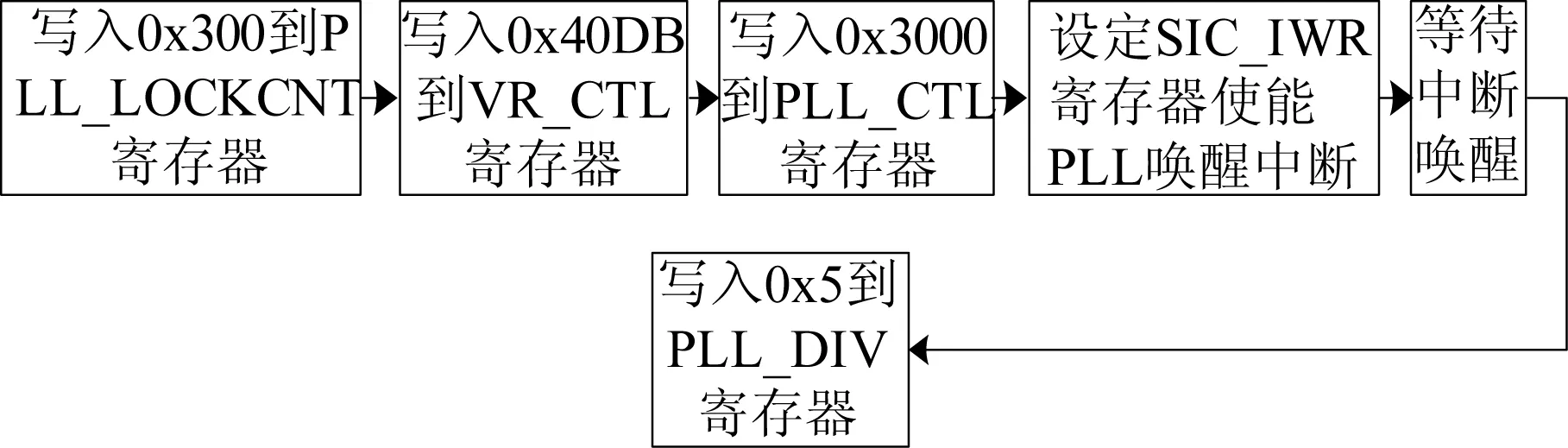

在智能斷電控制系統的硬件模塊設計的基礎上,進行軟件設計,通過軟件開發實現人機交互控制,在VisualDSP++中采用集成開發環境IDDE進行信息交換,開發應用程序之前,進行智能斷電控制及程序加載,智能斷電控制系統中使用的交叉編譯器統一為arm-linux-gcc-4.1.2,arm-linux-gcc-4.1.2編譯器,文中采用的交叉編譯以及使用標準GCC編譯的方式,用來配置qtx11、編譯和安裝,腳本名為install-qt-x11.sh,編譯GSL庫、Tslib庫文件,實現智能斷電控制中的諸如濾波、去抖、校準等流程,智能斷電控制系統軟件開發實現流程如圖7所示。

圖7 智能斷電控制系統軟件開發實現流程

首先進行初始化,包括:智能斷電控制的時鐘頻率初始化、智能斷電控制的存儲器初始化,數據指針中斷初始化,判斷A/D采樣是否完成,同步串口0初始化,智能斷電控制的初始化流程如圖8所示。

圖8 智能斷電控制的初始化流程

進一步配置CAN_MD1寄存器,判斷CAN配置的完整性,通過PPI接口的DMA功能進行中斷標志位通知,程序運行過程中采用循環堆棧遍歷進行斷電的高壓調節,要調節的數字量ΔD=65 536×V/5,輸出范圍為0~5V,接通,過燒寫器燒寫AT25HP512與DSP的接口,修改最上層的Makefile文件,實現智能斷電控制,在指定交叉編譯器的執行“Makemenuconfig” ,程序為:

exportIHIHIHY:JKKJGGYFT:= $(SEOHBWSNH)

ARCH?=armSoundcardsupprt

CROSS_COMPILE?=arm-linux-

Apihonkolks(assgrweet-legbb) --->

(/homesghghments/nfs)BusyBbgexInssvgrgnbrefix

BusyboxLidfhgnbryTudgthnng---> [*]Supportfor/etc/networks

3實驗分析

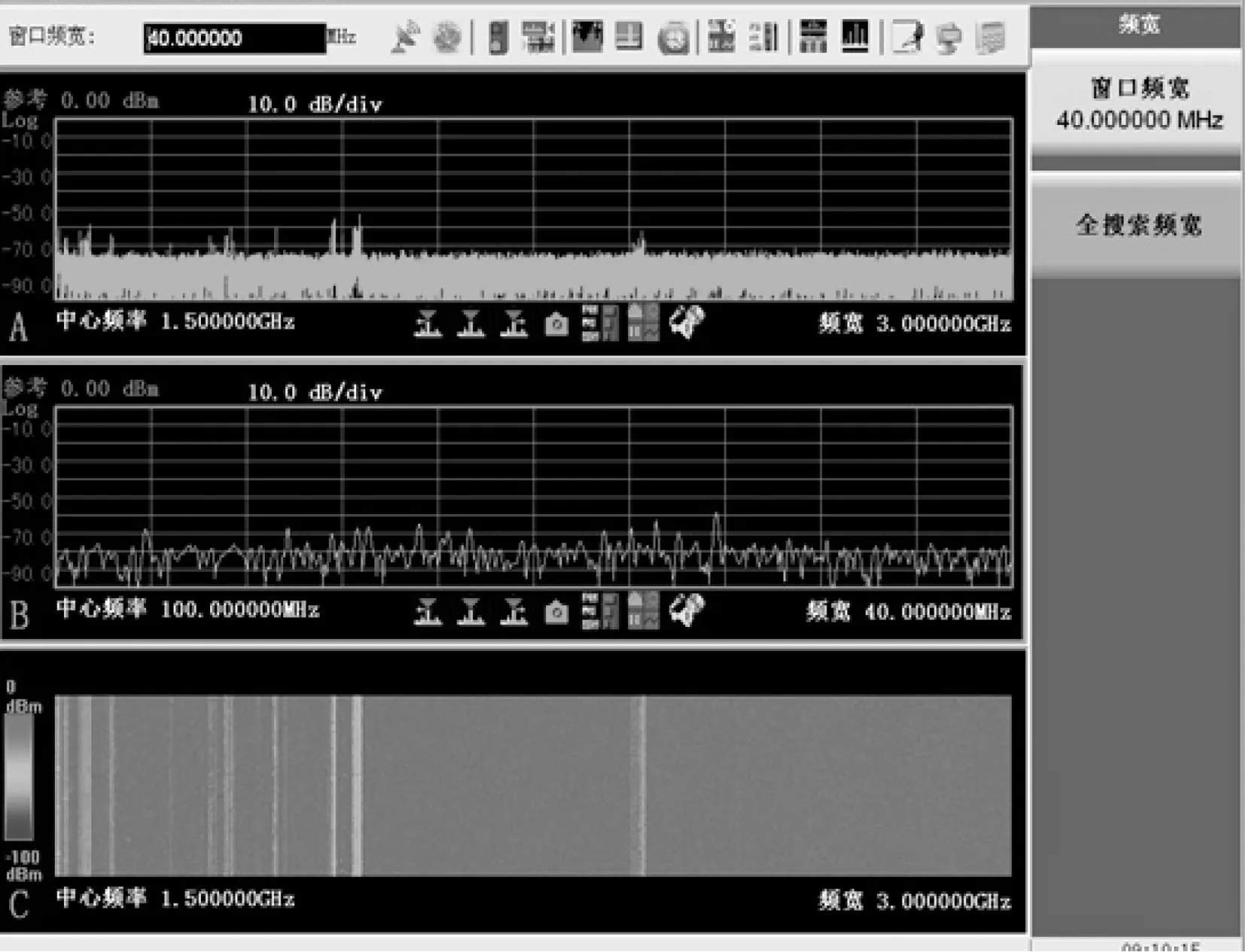

為了測試本文設計的基于循環堆棧遍歷的智能斷電控制系統的性能,進行了仿真實驗。系統測試中,斷電脈沖的采樣頻率為600MHz,nop為單周期指令,斷電控制系統的高壓調節低電平為3.3V,始調用內核中的AD7656.ko驅動模塊,開始AD采集,得到智能斷電控制系統A/D輸入端為25MHz的正弦信號。

輸入波形如圖9所示。

圖9 智能斷電控制系統的輸入波形

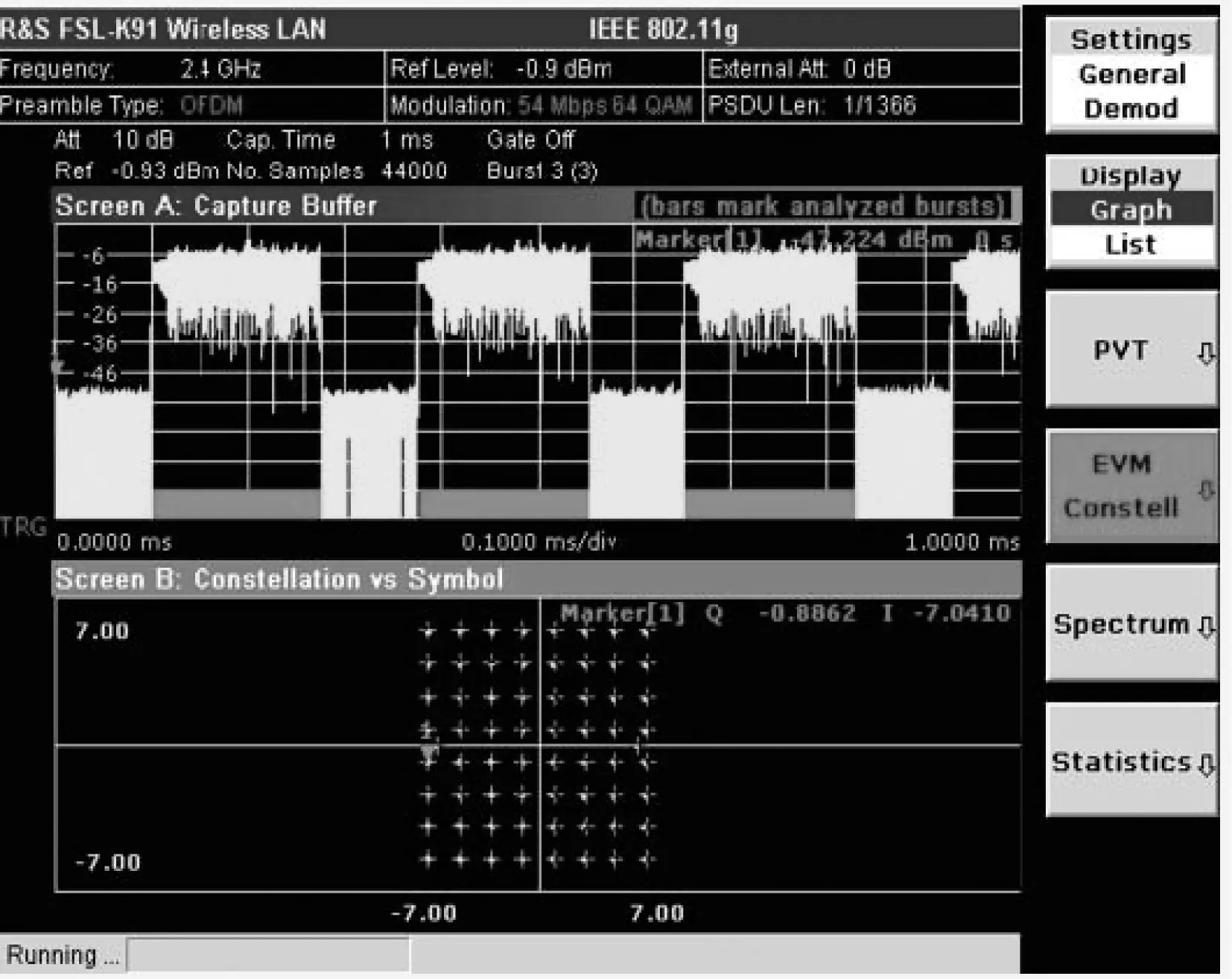

根據上述系統輸入波形為采樣樣本,進行智能斷電控制,在輸入端接入標準信號發生器,輸出端接入示波器,調理電路的低通截止頻率為80Hz,得到斷電控制的脈沖響應輸出見圖10。

圖10 智能斷電脈沖輸出響應

從圖10可見,采用本文方法能有效實現智能斷電控制,斷電控制信號發生器接入到四路AD采集通道,檢測到斷電控制信號的AD能完整采集斷電控制請求脈沖信號,有效抑制了溫度漂移和基線漂移,展示了較好的應用價值。

4結語

通過設計電源的智能斷電控制系統,避免過載導致電器設備的損壞。傳統的斷電控制系統設計采用單一道址計數方法進行斷電控制,當達到器件所能承受的最高負荷時進行智能斷電,受到分離元件的工作溫度的影響較大,控制性能不好。

本文提出的基于堆棧遍歷的智能斷電控制系統設計方法,在VisualDSP++ 4.5軟件開發環境下進行系統軟件開發,仿真實驗表明,采用該方法設計的系統具有較好的智能斷電控制性能,斷電控制信號的AD能完整采集斷電控制請求脈沖信號,有效抑制了溫度漂移和基線漂移,性能優越。

參考文獻:

[1]甄建軍,張毅. 基于螺旋平面線圈的感應電能傳輸技術研究[J].電氣自動化, 2014,36(2): 78-80.

ZHENJian-jun,ZHANGYi,HUGuang-bo.Researchoninductivepowertransmissiontechnologybasedonspiralplanarcoil[J].ElectricalAutomation,2014,36(2):78-80.

[2]李鵬,孫未蒙,李文強,等.一種改進積分滑模面在飛控中的應用[J].控制工程,2010,17(3):269-289.

LIPeng,SUNWei-meng,LIWen-qiang,etal.Applicationofimprovedintegralslidingsurfacetoflightcontrolsystem[J].ControlEngineeringofChina,2010,17(3):269-289.

[3]孫克輝,賀少波,董燕青. 簡化洛倫茲混沌系統的追蹤同步控制[J]. 信息與控制, 2015,44(4): 393-397.

SUNKe-hui,HEShao-bo,DONGYan-qing,etal.Trackingsynchronizationcontrolofthesimplifiedlorenzchaoticsystem[J].InformationandControl,2015,44(4):393-397.

[4]溫陽東,宋陽,王穎鑫,等. 基于模糊神經網絡的電力變壓器故障診斷[J]. 計算機測量與控制, 2013, 21(1): 39-41.

WENYang-dong,SONGYang,WANGYing-xin,etal.Faultdiagnosismethodforpowertransformerbasedonfuzzyneuralnetwork[J].ComputerMeasurement&Control,2013,21(1):39-41.

[5]克智. 基于智能變頻的無線通信基站節能研究[J]. 科技通報, 2012, 28(8): 62-65.

LIUKe-zhi.Wirelesscommunicationbasestationenergyaavingresearchbasedonintelligentfrequencyconversion[J].BulletinofScienceandTechnology,2012,28(8):62-65.

[6]雷邦軍,費樹岷,翟軍勇,等. 靜止無功補償器(SVC)的一種新型非線魯棒自適應控制設計方法[J]. 中國電機工程學報,2013, 33(30):65-70.

LEIBang-jun,FEIShu-min,ZHAIJun-yong,etal.AnovelimprovednonlinearrobustadaptivecontroldesignmethodofSVC[J].ProceedingsoftheCSEE,2013(30):65-70.

[7]陳達軍,于肇賢.計算機仿真在多級放大電路設計中的應用[J].電子設計工程,2015(18):30-33.

CHENDa-jun,YUZhao-xian.Applicationofcomputersimulationinamulti-stageamplifyingcircuitdesign[J].ElectronicDesignEngineering,2015 (18):30-33.

(本文編輯:嚴加)

Design of Intelligent Power Off Control System Based on Stack Traversal

HUANG Guan-hua, LU Xing-hua

(HualiCollege,GuangdongUniversityofTechnology,Guangzhou511325,China)

Abstract:The design of the intelligent power shutdown control system can help avoid electrical equipment damage caused by overload. This paper presents an intelligent power shutdown control system based on stack traversal. The system mainly includes the dynamic gain control module, the amplifier module, the intelligent power off filter module and the power module. The clock signal driving circuit, clock circuit, reset circuit and dynamic gain control circuit are designed. The system software is developed in DSP++ Visual 4.5 software development environment.

Key words:intelligent power off control; voltage; stack; system design

DOI:10.11973/dlyny201603004

基金項目:2012廣東省質量工程項目(粵教高函[2012]204號);2013年廣東省高等學校專業綜合改革試點項目(粵財教[2013]329號);2013廣東省大學生創新創業訓練計劃項目(1365613040);2012廣東省質量工程項目(粵教高函[2012]204號)

作者簡介:黃冠華(1992),男,主要研究方向為電力電子技術。

中圖分類號:TP273

文獻標志碼:A

文章編號:2095-1256(2016)03-0282-05

收稿日期:2016-03-15 2016-03-18