基于MSl的數字時鐘的電路設計

鄭 旭(黑龍江大學,150080)

?

基于MSl的數字時鐘的電路設計

鄭 旭

(黑龍江大學,150080)

數字時鐘的特點是以數字顯示秒、分、時,它是一種相較于傳統機械時鐘更準確、更直觀的時鐘裝置,數字時鐘也不需要機械傳動裝置,所以被廣泛使用。在日常生活中我們隨處可見數字時鐘,數字電子鐘以兩種方式實現:單片機控制,數字集成電路構成。本次設計是由數字集成電路構成的數字電子時鐘。

MSI;數字時鐘;電路設計

1 數字時鐘設計功能要求

該設計的電子鐘應該能夠準確計時,并將時間以數字形式顯示。在電路中,可以利用NE55振蕩電路提供的脈沖信號。同時在計時出現誤差時電路還可以完成校時、校分和校秒功能。具體要求如下:

(1)用NE555芯片產生時鐘脈沖;

(2)用數碼管顯示時間數字;

(3)數碼管顯示時、分、秒;

(4)具有校時功能。

2 設計方案

2.1方案概述

此次設計的電子鐘電路主要由以下幾部分組成:脈沖基準電路,計數器,譯碼器,時鐘顯示數碼管,校時器。

(1)脈沖基準電路:它是數字鐘的核心,由它產生時間基準源信號,提供給計數器,它的精確度決定了時間的精準。

(2)計數器:對基準信號進行計數。

(3)譯碼器:將計數器的輸出轉換成數碼管的驅動信號。

(4)時鐘顯示:將經過譯碼的數字顯示出來。

(5)校時器:調整時鐘的時間。

本數字鐘的工作原理如下:

由NE555電路產生1Hz的脈沖信號作為時間基準,提供給計數器計數,當秒計數器達滿60的時候向分計數器進位,并且秒計數器清零,當分鐘計數器達滿60的時候向時計數器進位,并且分鐘計數器清零,當時計數器滿24的時候時計數器清零。當時間與現實時間出現誤差的時候可以通過校時器進行校時。

2.2方案設計

2.2.1脈沖基準電路設計

本次設計采用NE55與電容電阻組成的多諧振蕩電路來產生1Hz的脈沖信號輸送給計數器。

NE555(Timer IC)為8腳時基集成電路,它只需簡單的電阻器、電容器,即可完成特定的振蕩延時作用。其延時范圍極廣,可由幾微秒至幾小時之久;.它的操作電源范圍極大,可與TTL,CMOS等邏輯電路配合,也就是它的輸出電平及輸入觸發電平,均能與這些系列邏輯電路的高、低電平匹配;其輸出端的供給電流大,可直接推動多種自動控制的負載;它的計時精確度高、溫度穩定度佳,且價格便宜。

NE555管腳介紹:

Pin 1 (接地) -地線(或共同接地) ,通常被連接到電路共同接地。

Pin 2 (觸發點) -這個腳位是觸發NE555使其啟動它的時間周期。觸發信號上緣電壓須大于2/3 VCC,下緣須低于1/3 VCC 。

Pin 3 (輸出) -當時間周期開始555的輸出腳位,移至比電源電壓少1.7伏的高電位。周期的結束輸出回到0伏左右的低電位。于高電位時的最大輸出電流大約200 mA 。

Pin 4 (重置) -一個低邏輯電位送至這個腳位時會重置定時器和使輸出回到一個低電位。它通常被接到正電源或忽略不用。

Pin 5 (控制) -這個接腳準許由外部電壓改變觸發和閘限電壓。當計時器經營在穩定或振蕩的運作方式下,這輸入能用來改變或調整輸出頻率。

Pin 6 (重置鎖定) - Pin 6重置鎖定并使輸出呈低態。當這個接腳的電壓從1/3 VCC電壓以下移至2/3 VCC以上時啟動這個動作。

Pin 7 (放電) -這個接腳和主要的輸出接腳有相同的電流輸出能力,當輸出為ON時為LOW,對地為低阻抗,當輸出為OFF時為HIGH,對地為高阻抗。

Pin 8 (V +) -這是555個計時器IC的正電源電壓端。供應電壓的范圍是+4.5伏特(最小值)至+16伏特(最大值)。

根據NE555內部管腳圖和所設計的NE555外部電路可知,C1是外接定時電容,R1、R3是充電電阻,并且R3又是放電電阻。C2用于防干擾。接通電源后,電源通過電阻對C充電,充電至當Thold=2/3的Vcc時, A1輸出為1,比較器A2輸出高電平,輸出端3輸出低電平,放電三極管T導通,電容C又要通過R2、T放電,Vcc下降,當Vcc下降至1/3Ucc時,VT截止,C又重新充電,以后恢復以上過程。其震蕩周期為:

在實驗的時候選擇1M的電阻為R1、R3,由公式可以計算出電容。

2.2.2計數器電路設計

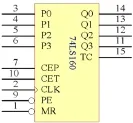

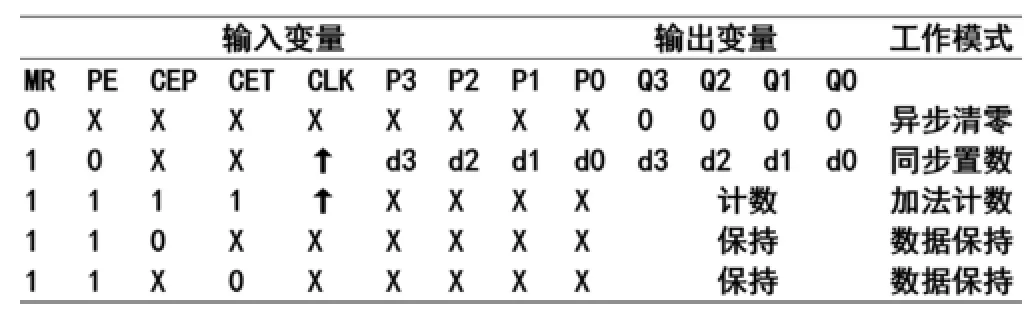

本設計時分秒的計數器選用十進制計數器74LS160。按照時間顯示的要求,秒的個位部分為逢十進一,十位部分為逢六進一,從而共同完成60進制計數器。74LS160實現60進制的方式有兩種:異步清零、同步置數。它的引腳圖如圖3所示,工作真值如表1所示:

圖3 74LS160的引腳圖

表1 74LS160工作真值表

秒計數器的個位和十位由兩個74LS160芯片組成,個位的74LS160計數范圍為0~9,因此將個位的74LS160計數器計滿十的時候的進位作為十位的計數器的計數信號,即將個位的74LS160的TC腳接到十位的74LS160的7腳和10腳,將秒的時鐘信號接到十位的74LS160的2腳CLK上,當個位的74LS160產生進位的時候十位的7腳和10腳為1,其處于加法技術的工作模式下,在時鐘高電平脈沖的作用下,十位的計數器74LS160計數加1。因此通過此種方式對秒計數器的十位進行計數。

2.2.3時鐘顯示電路設計

本設計中計數器的輸出為BCD碼,需選用一個譯碼器來實現數字的顯示,這里選用74ls47 bcd譯碼器。74LS47是BCD-7段數碼管譯碼器/驅動器,74LS47的功能用于將BCD碼轉化成數碼塊中的數字,通過它解碼,可以直接把數字轉換為數碼管的顯示數字。74LS47是輸出低電平有效的七段字形譯碼器,與它配合的是共陽七段數碼管,因為共陽數碼管直接與電源相連因此在數碼管的輸入與74LS47輸出之間應該并聯330歐的電阻來進行限流。

2.2.4校時器電路設計

在校時的時候我們必須模擬一個時鐘信號來時計數器進行加1計數,在校時的時候為了防止我們模擬的時鐘信號與正在運行的各個計數器系統的CLK信號發生沖突,因此在校時的時候應該斷開時鐘信號的輸入,此時可以將NE555產生脈沖和校時設置按鍵的信號進行相與,當校時按鍵按下的時候,與電路輸出0時秒計數器停止運行。本設計的與門采用四2輸入與門芯片74ls09。

當進行校時的時候按鍵被按下74LS09的12腳接地為0,因此不管時鐘脈沖為什么電平,74LS09的11腳輸出都為0,因此這種情況下可以屏蔽時鐘脈沖,為了防止在未按下校時按鈕的時候,按了三個時分秒其中的一個修改按鍵對,時鐘的時間產生影響,因此在校時按鈕未被按下的時候三個時分秒三個按鍵必須是失效,因此可以采用74ls09的一個與門來實現屏蔽在正常模式下,時分秒三個按鍵被誤按下時對時鐘工作的影響。

3 結語

本次設計了一個數字集成電路構成的數字電子鐘,設計的電子鐘主要由下面這幾部分電路組成:脈沖基準電路、計數器電路、譯碼器電路、時鐘顯示數碼管電路、校時器電路,實現了數字鐘顯示時間、計數、校時等功能。

[1]康華光.電子技術基礎.數字部分 北京:高等教育出版社,2000

[2]陳堅.電力電子學[M].北京:高等教育出版社,2002

[3]高吉祥.電子技術基礎實驗與課程設計.電子工業出版社,2002

Circuit design of digital clock based on MSI

Zheng Xu

(Heilongjiang University,150080)

In daily life,we can see the digital clock,digital clock in two ways:single chip microcomputer control,digital integrated circuit.The design is a digital electronic clock which is made up of digital integrated circuits.

MSI;digital clock;circuit design