基于FPGA的全數字鎖相環電機調速系統設計

陳 歡

(無錫科技職業學院,214112)

基于FPGA的全數字鎖相環電機調速系統設計

陳歡

(無錫科技職業學院,214112)

數字鎖相環具有抗干擾能力強、鎖相效果好等優點。而電機鎖相控制系統調速精度高,易于用程序實現。本文介紹了一種基于FPGA的數字鎖相環,用于電機調速系統的設計。

鎖相環;FPGA;鑒相器;濾波器

0 引言

“鎖相”概念的出現源自于對同步問題的研究,由荷蘭科學家C. Huygens提出。法國科學家DeBellescize在1932年發表了對鎖相環路的數學建模,并提出了同步檢波理論,鎖相技術的理論才得以初步發展和確立。模擬鎖相環和后來出現的模數混合鎖相環均存在固有缺陷,對噪聲敏感,造成電路的抗干擾性能較差,影響電路設計的品質。隨著數字電路技術的發展,數字鎖相環不僅解決了模擬鎖相環存在的器件飽和、零點漂移以及易受環境和電源的溫度變換影響等缺點,還具備實時處理離散數據的能力。全數字化鎖相環必將是未來發展的趨勢。電動機鎖相控制系統具有調速精度高、給定信號精度高和易于程序實現和計算機控制等優點。本文在數字鎖相環和電機控制理論的基礎上,對全數字鎖相環調速系統進行探究,確定了由FPGA片內資源產生PWM參考波,用鑒相器、變模K加減計數器實現環路濾波器、脈沖加減電路和N分頻電路,以此構成數控振蕩器全數字鎖相環。

1 全數字鎖相環電機調速系統設計

1.1概述

全數字鎖相環包含四個模塊,鑒相器,K變模可逆計數器、脈沖加減電路、模N分頻器。K變模可逆計數器起環路濾波器的作用,其濾波原理是通過設置一個門閥值進行濾波;脈沖加減電路和模N分頻器相當于鎖相環PLL中的頻率振蕩器。全數字鎖相環通過脈沖計數器來實現,從而達到全數字的設計要求,只有計數器的實現還遠遠不夠,還需要同步脈沖控制來實現。同步控制是全數字鎖相環控制系統實現的關鍵。整個系統是在系統時鐘的控制下,進行計數器計數的量化,將模擬信號轉換成數字量。

1.2數字鑒相器

數字鑒相器用計數器實現,將輸入參考信號和反饋信號的相位差Фe=Фin-Фout,經鑒相后輸出包含相位誤差信息的波形Se,控制K變模可逆計數器的計數方向。當環路鎖定時,Se的輸出是占空比為50%的方波,即輸出的絕對相差為π/2。

1.3K變模可逆計數器

K變模可逆計數器濾除異或鑒相器輸出Se的相位誤差中的高頻信號分量,促進環路性能穩定。Se輸出信號控制K變模計數器的加減運算。當Se為高電平時,計數器會執行減運算,若計數器減為零時,就會輸出BORROW信號即脈沖借位脈沖控制信號給脈沖加減電路;當Se為低電平時,加計數器會相應的執行加運算,若是計數的結果達到計數器預先設定的模值,就會輸出進位脈沖CARRY信號。

可逆計數器的模的大小和數字鎖相環的性能有直接關系,數字鎖相環的跟蹤步長由模的大小來決定。模值越小,跟蹤步長會反方向變化越來越大,鎖定時的相位誤差就會越大,但是捕獲時間會變短;模值越大,跟蹤步長越小,相應的相位誤差會變小,但信號捕獲時間變長。可逆計數器的模是2的N次冪,由輸入四位

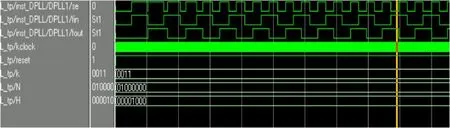

圖1 全數字鎖相環Modelsim仿真圖

二進制信號K預設,當K的取值在0001~1111時,相應的模的變化范圍為23~217。

在鎖相環同步鎖定的狀態下,鑒相器的輸出沒有超前或滯后脈沖的輸出信息,這意味著K計數器正常情況下是沒有輸出的;從而避免噪聲對鎖相環的誤控作用,增強了系統抗噪能力。K值的適當取值對于環路的穩定性能也很重要。K值取得大時,少量噪聲的干擾不會讓計數器計滿,因此也不會產生進借位脈沖。但是大的K值會造成捕捉帶變小,加大環路捕獲時間。反之,K值取得小,雖然可以加快環路的鎖定,但是K計數器會較為頻繁的產生脈沖控制輸出信號,降低環路對噪聲的抑制能力。

1.4數控振蕩器

數控振蕩器由脈沖加減電路和除N計數器構成,實現對輸入參考信號頻率和相位的跟蹤及調整。本文的脈沖加減電路通過JK 觸發器和D 觸發器的組合來實現。當鎖相環路進入鎖定狀態時,加減脈沖電路相當于二分頻的分頻器,此時鎖相環電路并不會產生進位或者借位的脈沖信號。當有進位信號時,加減脈沖電路的功能不僅會將信號二分頻,而且會在信號中加入半個時鐘周期脈沖,以期提高輸出信號的頻率,減小與輸入參考信號的相差。當有借位信號傳入,輸出信號的頻率會降低,即輸出信號中會減去半個時鐘周期的脈沖。脈沖加減控制通過這種方式進行相位調節,最終實現閉環系統的相位鎖定。考慮到實際電路中的延時,可能會有毛刺信號出現在邏輯輸出信號中, 進而導致鎖相環的誤控或是鎖相環鎖相出現問題,鑒于毛刺信號可以在時鐘控制下的D觸發器弱化消除,因此脈沖加減電路用JK 觸發器和D 觸發器實現。

圖1為全數字鎖相環Modelsim仿真圖,可以看出經過一段時間,相差鎖定在90度。

2 結論

本文設計了一種全數字鎖相環,用于電機速度控制,鎖相效果較好。

[1] 魏建瑋,高迎雪. 鎖相環技術綜述[J]. 科技信息職教與成教,2008,36

[2] Thomas Olsson.A digitally controlled PLL for So Capplications[J].IEEE Journal of Solid State Circuits,vol.39,No.5,May 2004.

[3] Ching-Tsai Pan,Fang,E.A Phase-Locked-Loop-Assisted Internal Model Adjustable Speed Controller for BLDC Motors[J].IEEE Journals, 2008, Page(s):3415-3425

[4] 肖龍,楊佩君,湯恩生. 基于軟件鎖相環的電機速度控制系統[J]. 航天返回與遙感,2006,27(3).

[5] 黃保瑞,楊世平. 基于 FPGA 的全數字鎖相環設計[J]. 電子測試-微處理器與可編程控制器,2014.

Digital Phase-locked Loop Motor Speed Control based on FPGA

Chen Huan

(Wuxi Vocational College of Science and Technology,214112)

Digital phase-locked loop has the advantage of anti-interference and well phase-locked. Meanwhile,there is high accuracy in motor phase-locked control system which can be achieved by program. This paper presents an digital phase-locked based on FPGA so as to control the speed of the motor.

Phase-locked Loop;FPGA;Phase Detector;Filter