ROM查表結構的數控振蕩器設計及FPGA實現

王猛,王粵

(1.棗莊學院光電工程學院,山東棗莊 277160;2.棗莊廣播電視總臺,山東棗莊 277100)

?

ROM查表結構的數控振蕩器設計及FPGA實現

王猛1,王粵2

(1.棗莊學院光電工程學院,山東棗莊277160;2.棗莊廣播電視總臺,山東棗莊277100)

為了滿足通信領域數字化技術對頻率合成技術的要求,文章設計并實現了基于ROM查表結構的數控振蕩器,文章首先簡要介紹數控振蕩器的技術發展背景及其在數字頻率合成技術的應用,其次介紹數控振蕩器的技術原理及采用硬件設計的實現方法,重點討論了基于ROM查表結構實現的數控振蕩器,以及該數控振蕩器的FPGA設計,最后對相關理論和技術的發展進行討論和實現.

數控振蕩器,FPGA設計,ROM查表結構①

0 引言

數控振蕩器(NCO,numerically controlled oscillator)是數字通信領域中一個不可缺少的角色,它通常與直接數字頻率合成器(DDS,Direct digital synthesizer)等混為一談,主要是因為其與直接數字頻率合成器技術模塊內容基本相近,其實為直接數字頻率合成器的主要組成部分,NCO的設計也是采用的數字頻率合成器的技術原理來實現的.隨著頻率合成技術的發展,頻率合成技術應用非常之廣泛,特別是在現代電子信息系統領域和通信裝備技術領域,在生成具有較高穩定度和準確度的頻率信號方面已經有了比較成熟的發展過程,從現代技術的意義上來理解的頻率合成技術就是把若干個具有穩定性的標準的頻率經過四則運算即“加、減、乘、除”來生成一系列具有新的穩定性和準確性的頻率的過程.現代信息技術的發展,使得研究者對頻率合成技術的性能方面提出了更高的要求,例如在信號的頻率穩定性,信號的準確度,信號的頻譜純度等的要求越來越高,因此人們不斷研究并對頻率合成技術創新,實現將頻率合成技術廣泛應用到現代科技技術的各個領域中.

1 頻率合成及FPGA設計技術

1.1頻率合成技術介紹

頻率合成技術最早源于國外,在20世紀30年代提出這么一個技術概念,目前可以按照其實現方式分為四種形式,分別為直接類:直接頻率合成技術,直接數字頻率合成(DDS)技術,間接類:間接頻率合成技術(主要是基于鎖相環的),混合式頻率合成技術(不常用).

直接頻率合成技術發展歷史最早,實現方面也較容易,主要是由一系列實現頻率加減法的器件(如混頻器等)、實現頻率乘法倍乘的器件(如倍頻器),實現頻率除法的器件(如分頻器)等來構成的,進而得到所需的各種頻率,但由于其生成的頻率信號在性能方面頻譜純度差,可靠性不好等缺點,并不常用.

直接數字頻率合成技術在頻率合成技術領域上來說是一種革新,追溯其發展歷史來源于1971年,由J.Tierney,和B.Gold第一次提出的,這種技術一提出受到廣泛的認可,是一種產生穩定頻率信號的理想方法,未來的應用前景會更加廣闊.直接數字頻率合成器具有計算機驅動的參與頻率合成,通過大量的數字信號處理和計算機操作,來實現在時域中進行頻率合成,主要優點是輸出頻率分辨力高,另外由于內部相位累加的原因,結果造成在頻率之間的“跳躍”較好,并且變化頻率的時候相位是連續的,這是特別重要的,連續相位調制正是基于這一優勢特點.

間接頻率合成技術是伴隨著數字電路技術的發展而衍生的,間接頻率合成技術一個重要的表現形式就是鎖相頻率合成技術,源于1932年德國科學家初次提出的關于鎖相環路的描述,直到1947年鎖相環用于接受機的同步掃描才開始受到關注,到1970年前后由于集成電路的發展,鎖相環使用更加頻繁,因為它的成本低,容易使用,所以它被逐漸應用到通信技術領域中,主要應用于調制解調、通信發射與傳輸、電視機載波提取等民用設備中.其技術的優點是:易于器件生成、成本較低,而且具有良好的跟蹤、窄帶濾波和記憶功能,特別是在大規模集成電路和數字電路發展的背景下,非常利于小型化、集成化.缺點是由于電子器件的影響,響應速度較慢,另外就是頻譜純度不高,這也是影響頻率合成技術共同的性能指標.

1.2基于FPGA硬件設計技術介紹

最早來源于20世紀70年代的硬件設計技術,主要采用的是分立元件,后來隨著集成電路以及計算機和電子器件的革新,硬件設計技術步入采用中小規模集成電路初級階段,但是由于是簡單的人工焊電路板,所以布圖方法根本就不能滿足產品復雜性的要求,并且太不方便,后來美國ACCEL公司開發了一個可以用二維圖像邏輯與分析的CAD工具代替,即Tango布線軟件.

隨著微電子工藝的發展,加上計算機應用技術的發展,美國研究者研究出支持定制單元電路設計的掩膜編程的門陣列,如可編程邏輯器件(PAL和GAL)等一系列微結構,這也是硬件設計器件的第一次出現,代替了具體化的元件圖設計,20世紀80年代初推出的硬件設計技術,使設計師能提前預知產品的功能和性能,并且最后生成制造產品的相關文件來進行驗證[1].

最后一個階段就是20世紀90年代以后發展起來的電子系統設計自動化階段,也叫EDA,EDA技術的發展,使得廠家為滿足用戶的要求設計出各種各樣的規模的可編程邏輯器件,使設計者能夠通過設計芯片來實現電子系統的功能,讓他們把想設計的電路模型通過系統級設計工具(quartus、modelsim等軟件開發工具)和設計語言(Verilog HDL)設計在自己的專用芯片里,實現產品的功能.

上面所述的EDA技術涉及的面比較廣,包含了硬件描述語言(如verilog),硬件設計開發工具(如quartus軟件),和大規模可編程邏輯器件(如FPGA、CPLD等)等,其中FPGA器件是現代應用最廣泛的可編程邏輯器件,應用非常廣泛,所謂可編程邏輯器件,就是滿足各式各樣的用戶要求可編程的,另外還能便于實現某種邏輯功能的重要邏輯器件,它們在電子設計領域扮演著非常重要的角色,為未來電子系統的設計提供了更多的可能.可編程邏輯器件最早誕生于上面硬件設計的最初階段,也即20世紀70年代,在不斷發展的過程中,邏輯器件的響應速度不斷加快,集成度不斷提高,功耗不斷減小,可靠性不斷提高,結構性不斷合理,使用變得更加靈活與方便.

2 基于ROM查表結構的數控振蕩器原理

2.1數控振蕩器原理

數字控制振蕩器即NCO(Numerically Controlled Oscillator)是用于產生一個理想的、數字可控的正弦或余弦波的數字控制式振蕩器,在實際的通信系統中,攜帶數字信息的信號通常是由某種類型的載波調制方式發送的,傳送信號的帶寬限制在以載波為中心的一個頻段上,如雙邊帶調制,或在鄰近載波的頻段上,如單邊帶調制.無論何種調制方式,在發送端均需要一個高頻載波將信息調制,以減小信號衰落對通信質量的影響,在解調過程中也是同樣的原理,需要解調下來,比如相干解調時需要一個與發送端同頻同相的高頻載波將信息從高頻上解調下來.產生這個高頻載波的方法,目前在數字電路中主要是采用數控振蕩器(NCO),也稱為直接數字頻率合成器〔DDS),它的輸出頻率和相位可以受人為控制,從而滿足各種需要[2].

目前實現數字控制振蕩器有兩種常用的方法,一種是實時計算法,由于在需要產生高速的正交信號時,實時計算法有一定的局限性[3].另外一種為查表法,實現起來最有效、最簡單,其方法原理是事先根據通信正弦波相位的需求來計算相位的正弦值,從而提取出相位作為地址信息來存儲該相位的正弦值數據,該數據就放在查表法的ROM表中[4].

對于基本的正弦信號發生器,它的輸出可以用下面的三角函數式來描述,假設一個角頻率為ω、幅度為A且初試相位θ=0的正弦信號可以表示為

Sout=Asinωt=Asin(2πfoutt)

(1)

上述公式的表述對于時間t來說是連續的,為了在FPGA中或者說在硬件中實現該表達式的處理,必須對表達式進行離散化處理.令正弦信號的相位:

θ=2πfoutt

(2)

(3)

若將三角函數一個周期的相位2π分成M等份(M=2N),則每一份也即最小相位增量為:

(4)

那么最低輸出頻率為

(5)

最后得出其輸出信號為

(6)

NCO(數控振蕩器)電路一般由參考時鐘、相位累加器、波形存通濾波器(LPF)組成.其結構如圖1所示.

圖1 DDS基本結構框圖

2.2基于ROM查表結構的數控振蕩器

在DDS系統中實現最后的波形生成方式較多,本文主要采用的是基于ROM查找表法來實現波形的生成,ROM查表結構的核心是將事先部分周期的波形幅度值存儲在一個ROM中,這樣的在DDS中由相位累加器輸出的相位序列就可以找到ROM查找表中波形幅度值地址,從而實現波形的生成和相位到幅度的轉換.

圖2 基于FPGA+查表結構的NCO設計實現框圖

ROM查表結構是DDS中非常核心的部分,在數字頻率合成器的原理中已有介紹,雖然查表法有一定的缺點,但因其方便快捷的把相位信息轉換為幅度信息,逐漸受到國內外研究者的歡迎,ROM查表結構也可以在FPGA上實現,基于FPGA查表法結構實現DDS意味著包括ROM查表程序的編寫,相位累加器的生成,都是在FPGA直接生成的,也意味著波形存儲器采用ROM結構,在DDS中,由相位累加器的輸出的數字相位信息只有經過ROM查找表結構查找進行轉換才會變換為正弦波[5].

在ROM查表結構中,存儲器的位寬決定著查表法的精度[6],也影響著DDS的性能和輸出波形的精度.ROM查表結構通常由matlab軟件仿真生成,一般為mif格式,在FPGA中調用ROM時候也要加載mif文件,當然這是Altera公司FPGA調用一般采用的,xilinx公司采用的是coe文件,因此實現ROM查表法生成mif文件是首要的操作.

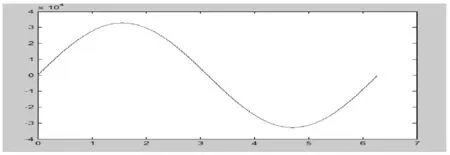

下一步操作就是設定位寬和深度生成波形存儲文件,假定ROM的深度設為1024,ROM的位寬為16,則意味著一個完成正弦信號周期的1024個點量化,量化幅度為16位,生成的量化圖如圖3.14所示:

圖3 對正弦信號的一個周期的1024個點量化圖

在matlab軟件里輸入程序,程序簡略如下:

depth= 1024; //表明采用的存儲深度

width= 16; //表明采用的位寬

address_radix=dec; //設定地址的格式為十進制

data_radix=dec; //設定數據的格式為十進制

ContentBegin//表明內容開始

0 : 6 ; //地址: 數據

1 : 12 ;

...: ....;

1023;

end;

depth= 1024;

width=16;

x=linspace(0,6.28,1024); %6.28為2π,一個周期內等間隔地取1024個點

y1=cos(x);

y2=sin(x);%計算相應的正余弦值

y1=y1*32678;

y2=y2*32768;%量化操作

fid=fopen('d:/cos.mif', 'wt'); %存放mif文件

fprintf(fid, '%16.0f ',y1); %在寫文件時量化成16bit

3 硬件設計及實現

按照上節生成的mif文件后,就可以加載到quartus軟件里IPcore,加載到Ipcore后就可以隨便調用了,IPcore是一個模塊性的設計,通過模塊性的設計,存儲到核里后,硬件設計就可以免去許多重復性勞動,下一次研究者可以直接調用該模塊.加載步驟為:打開quartus軟件,新建操作,選擇新建BLOCKROM,再選擇MegawizardPlug-InManager,選擇ROM-1-port, 選擇位寬為16、深度為1024,然后選擇mif文件并加載到BLOCKROM所生成的ROM中[7].

圖4 FPGA上生成ROM示意圖

在FPGA實現mif文件的加載后,意味著ROM查表結構的完成,然后只需在quartus軟件里編寫DDS其他結構的程序即可,最后在原理圖中調用生成IP核模塊.用Verilog語言編寫實現相位累加器的輸出,實現相位累加器的步驟為:設定系統的工作頻率,這里黑金開發板FPGA內部時鐘頻率為20Mhz,則DDS模塊的輸出頻率公式為:

其中K為頻率控制字,fclk為系統時鐘工作頻率20MHZ,由公式可以進一步計算出K的值,然后在程序里就可以設定不斷地對頻率控制字K進行相位累加[8],在每來一次時鐘激勵下,相位累加器就把頻率控制字累加一次,最后得到累加器輸出的總數據即為所求信號的相位[9].

在quartus軟件中編程,經過仿真運行后,其生成的的RTL原理圖如圖5:

圖5 基于FPGA+ROM的軟件設計原理框圖

軟件仿真生成后如圖6所示,

圖6 仿真示意圖

基于ROM查表結構有其一定的優點,使用便捷,易實現,只需提前計算好相位的正余值,將數據提前存儲在表里即可,用的時候一一對照就可以產生相應的正余弦波,是實際應用中最有效最簡單的方法.然而其也有一定的缺點,它的局限性主要體現在以下幾個方面,一是在硬件資源的消耗較大,比如我們采用20位尋址數據,那么ROM表的容量就得至少達到2的20次方上,因此占用空間較大,更高位的話占用空間會更大,限制了尋址的準確性.二是相位雜散量也較大,在ROM查表結構中,人們總希望查表的精度越高越好,因此希望ROM的容量越大越好,這樣相位累加器的輸出就可以實現更好的分辨率,信號的頻譜純度也越高,但是由于ROM的容量有所限制,并不能無限期的增大.三是實現精度也低,由于ROM查表結構的位數和硬件存儲器的限制[10].

4 結論

本文給出了一種基于FPGA +ROM查表結構來硬件實現NCO的設計,軟件基于Quartus軟件,在Quartus軟件上實現了基于ROM查表結構的NCO設計,并在軟件上實現了仿真,在實際應用過程中可參考本文的原理方法和實踐設計,從而應用在通信等基礎領域中.應用中,只需通過改變頻率控制字、系統采樣頻率、存儲正余弦查找表的深度和存儲表的位寬[11],即可控制不同頻率的輸出,對于通信里面調制信號領域非常實用.同時本文分析了該方法實現的缺點,如果涉及需要的精度及頻率較高,可以通過改變算法,或者設計FPGA硬件的配合實用,從而達到輸出的設計要求.

[1]劉小俊. 基于 EDA 技術的兼容 MCS-51 單片機 IP 核設計[D]. 武漢理工大學, 2005.

[2]吳邊. 數字中頻擴頻收發機的關鍵技術研究及FPGA實現[D]. 南京航空航天大學, 2004.

[3]楊勛. 軟件無線電中上下變頻技術的設計和實現[D]. 西安電子科技大學, 2007.

[4]謝英浩, 李紹榮. 基于軟件無線電的GMSK通信收發機及其FPGA實現[C].電子科技大學電子科學技術研究院學術交流會. 2007.

[5]王培元, 孫南海. 基于 FPGA 的 DDS 數字調頻系統仿真研究[J]. 襄樊學院學報, 2007, 27(5): 76-79.

[6]De Caro D, Napoli E, Strollo A G M. ROM-less direct digital frequency synthesizers exploiting polynomial approximation[C]//Electronics, Circuits and Systems, 2002. 9th International Conference on. IEEE, 2002, 2: 481-484.

[7]隗聰. 基于 FPGA 的三角函數數字發生器設計[J]. 計算機與數字工程, 2010, 38(9): 187-189.

[8]高士友, 胡學深, 杜興莉, 等. 基于 FPGA 的 DDS 信號發生器設計[J]. 現代電子技術, 2009, 32(16): 35-37.

[9]陳楠. FPGA 在 DDS 技術中的應用[J]. 廣西輕工業, 2011 (7): 61-62.

[10]聶強. 基于CORDIC算法的直接數字頻率合成器的設計與實現[D]. 西安電子科技大學, 2011.

[11]張阿寧, 趙萍. 基于FPGA的正交數控振蕩器(NCO)的設計與實現[J]. 電子設計工程, 2011, 19(17):149-152.

[責任編輯:閆昕]

Design and FPGA Implementation of Numerically Controlled Oscillator

WANG Meng1, WANG Yue2

(1.School of Opto Electronic, Zaozhuang University, Zaozhuang 277160,China;2.Zaozhuang Radio and Television Station,Zaozhuang 277100,China)

In order to meet the requirements of the communication in the field of digital technology on frequency synthesis technology, the article design and realize the ROM look-up table structure of numerically controlled oscillator based on, firstly, this paper briefly introduces numerically controlled oscillator technological development background and application in digital frequency synthesis technology, secondly introduces the numerically controlled oscillator technology principle and the realization method of the hardware design,discussed in detail based on the ROM look-up table structure to achieve the numerically controlled oscillator, and the numerically controlled oscillator FPGA design. Finally, the development of related theories and technologies are discussed and implemented.

numerical controlled oscillator; FPGA design; ROM look up table structure

2016-07-02

2015年棗莊學院校級科研基金項目(項目編號:2015QN05).

王猛(1987-),男,山東棗莊人,棗莊學院光電工程學院助教,工學碩士,主要從事抗干擾通信、硬件實現等方向的研究.

U283.4

A

1004-7077(2016)05-0116-07