40nm工藝32x32b雙端口SRAM的設(shè)計(jì)與優(yōu)化

摘 要 這篇文章主要論述了在具體的工程實(shí)踐中,由于6TSRAM在40nm工藝下的集成電路設(shè)計(jì)中表現(xiàn)出的性能和功耗均達(dá)不到設(shè)計(jì)要求,而在物理設(shè)計(jì)當(dāng)中由寄存器組成的存儲(chǔ)體的面積和功耗更難以勝任,所以需要定制設(shè)計(jì)一款32X32雙端口8TSRAM。在先進(jìn)工藝下8TSRAM所表現(xiàn)的性能和功耗均勝于前兩者,在FT-X的芯片上運(yùn)用該結(jié)構(gòu)有效優(yōu)化了時(shí)序和功耗。

【關(guān)鍵詞】SRAM 定制設(shè)計(jì) 性能 功耗

1 引言

Cache的設(shè)計(jì)是芯片集成電路設(shè)計(jì)重要的一部分。高效、快速的SRAM一直以來(lái)都是集成電路設(shè)計(jì)者始終追求的目標(biāo)。

對(duì)于SRAM存儲(chǔ)單元來(lái)說(shuō),它第一個(gè)必須具備的優(yōu)點(diǎn)就是高穩(wěn)定性,這樣才能保證存儲(chǔ)體進(jìn)行正確的讀、寫(xiě)操作。在0.18u工藝、0.13u工藝,6T單元具有很好的穩(wěn)定性,而且由于它面積小的特點(diǎn),一直備受設(shè)計(jì)者的青睞。但是,隨著CMOS工藝尺寸的發(fā)展,在進(jìn)入65nm、45nm、32nm甚至22nm之后,6管SRAM由于其存儲(chǔ)結(jié)構(gòu)的特點(diǎn),數(shù)據(jù)輸出皆是通過(guò)敏感放大器檢測(cè)位線電壓差,并將電壓差進(jìn)行放大輸出。但是隨著工藝尺寸的縮小和電源電壓的降低,6管存儲(chǔ)單元的穩(wěn)定性越來(lái)越差,抗噪聲能力越來(lái)越弱,使得敏感器的開(kāi)啟與關(guān)斷時(shí)間很難控制,而且時(shí)常會(huì)發(fā)生位線的一個(gè)噪聲電壓被敏感放大器放大輸出的錯(cuò)誤操作。由寄存器組合成的存儲(chǔ)模塊其面積和功耗是所有低功耗設(shè)計(jì)者的噩夢(mèng)。

本文通過(guò)實(shí)際工程項(xiàng)目中出現(xiàn)的問(wèn)題,由于6TSRAM和寄存器組成的SRAM在后端物理設(shè)計(jì)當(dāng)中出現(xiàn)面積、功耗和時(shí)序的問(wèn)題制約了芯片性能的提升,用8TSRAM進(jìn)行全定制設(shè)計(jì)替代芯片中的部分存儲(chǔ)模塊,最后進(jìn)行數(shù)據(jù)對(duì)比證明了8TSRAM在納米級(jí)工藝下的重要作用。

2 電路設(shè)計(jì)

2.1 寫(xiě)路徑

寫(xiě)IO模塊由32個(gè)1倍的DFF和64個(gè)4倍的反相器組成,寫(xiě)數(shù)據(jù)在寫(xiě)門(mén)控時(shí)鐘WCLK控制下,產(chǎn)生WBL<31:0>以及WBLB<31:0>,在寫(xiě)字線WWL<31:0>控制下寫(xiě)入存儲(chǔ)單元。

2.2 讀路徑

IO讀出電路分為全局與局部?jī)杉?jí)電路進(jìn)行讀出,每根局部讀位線上掛8個(gè)cell,一個(gè)局部讀出單元電路對(duì)兩根局部位線進(jìn)行預(yù)充,局部IO電路是16選1。

2.3 時(shí)鐘模塊

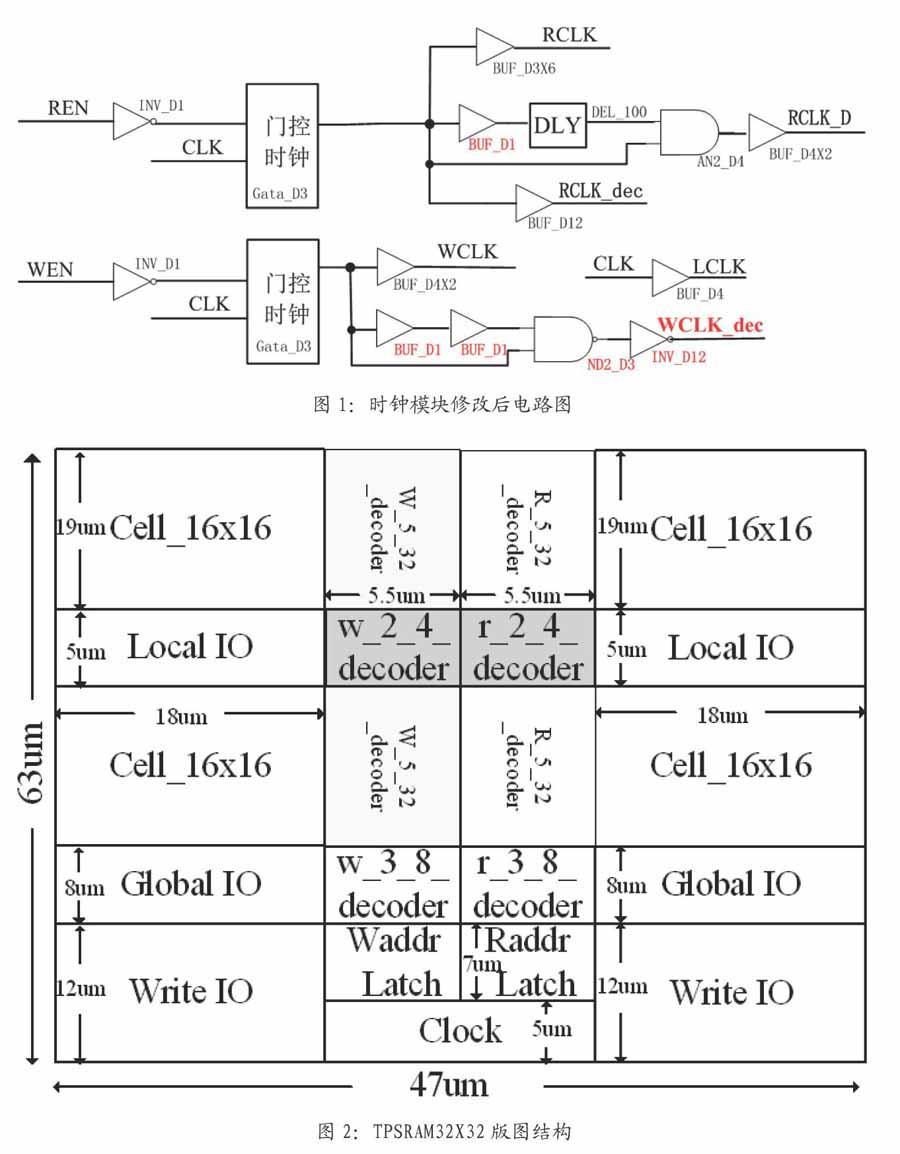

圖1為時(shí)鐘模塊修改后電路圖。為解決寫(xiě)時(shí)序中寫(xiě)字線先于寫(xiě)數(shù)據(jù)穩(wěn)定的問(wèn)題,適當(dāng)推遲寫(xiě)譯碼時(shí)鐘WCLK_DEC(推遲約90ps)的開(kāi)啟時(shí)間,且不推遲寫(xiě)譯碼時(shí)鐘的關(guān)斷時(shí)間(防止字線產(chǎn)生毛刺);為解決讀時(shí)序中讀出數(shù)據(jù)存在毛刺的問(wèn)題,適當(dāng)推遲求值時(shí)鐘RCLK_D(推遲約20ps)的開(kāi)啟時(shí)間。

3 版圖設(shè)計(jì)

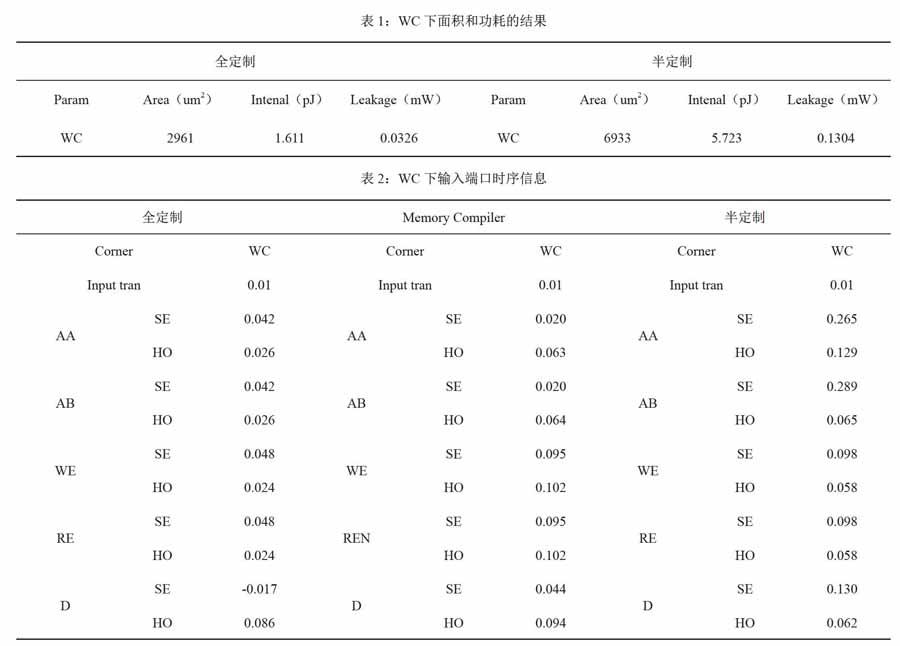

版圖結(jié)構(gòu)按功能進(jìn)行劃分,主要包括以下幾個(gè)部分:中間部分從上至下依次為讀寫(xiě)地址二級(jí)譯碼、讀寫(xiě)地址預(yù)譯碼、讀寫(xiě)地址鎖存器、時(shí)鐘模塊;左右兩側(cè)為陣列模塊,陣列cell中間為L(zhǎng)ocal IO模塊,陣列下面依次為Global IO模塊、Write IO模塊。

整個(gè)版圖左右兩邊為陣列,中間為譯碼及時(shí)鐘,左右兩邊距離邊界阱不小于1.3um;整個(gè)版圖上下各加一行DCAP單元,高度為1.68um。圖2是存儲(chǔ)器的版圖布局規(guī)劃圖,下面分別對(duì)這幾個(gè)部分進(jìn)行說(shuō)明:

3.1 陣列模塊

陣列位于整個(gè)存儲(chǔ)器的左右兩邊,由32個(gè)32位cell單元組成,陣列左邊和右邊各有32×16個(gè)cell單元,其中上下各有16×16個(gè)。

3.2 時(shí)鐘模塊

為減緩電路電壓的波動(dòng),時(shí)鐘模塊被DCAP單元包圍;為減小時(shí)鐘線上電流密度,時(shí)鐘線線寬加寬至0.08um;為降低時(shí)鐘線的耦合串?dāng)_,時(shí)鐘線盡量不與除電源地線外的長(zhǎng)線互連線并行走線或者加大與信號(hào)線間的間距,盡量被電源線或者地線包圍。

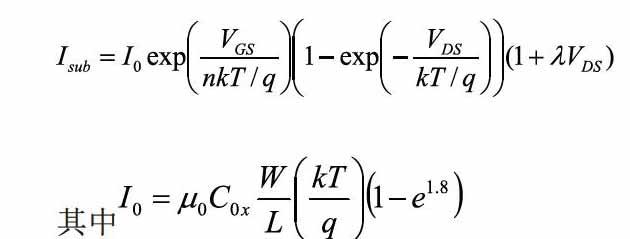

4 面積、時(shí)序和功耗

TPSRAM32X32的版圖面47um×63um,在TSMC40G的WC和WCL工藝拐角下頻率可達(dá)到1.8GHz,時(shí)鐘信號(hào)的最小脈沖寬度為200ps,在TSMC40G的TC和LT工藝拐角下時(shí)鐘信號(hào)的最小脈沖寬度為130ps。

5 結(jié)論

在40nm工藝下,由于電源電壓的降低,6T結(jié)構(gòu)SRAM為了保證讀操作的正確性,每一代工藝遷移晶體管尺寸的減小都有限,尤其是從45nm工藝遷移到32nm工藝,6T結(jié)構(gòu)的下拉N管尺寸幾乎沒(méi)改變,所以面積也會(huì)大于8T結(jié)構(gòu)。

在功耗方面亞閾值漏電流的計(jì)算公式如下:

可知,亞閾值漏電流與尺寸大小關(guān),在40nm下8T結(jié)構(gòu)可以選用更小尺寸的下拉管接地,從而有效減少漏電流。

最終的數(shù)據(jù)結(jié)果比對(duì)可以查看表1、表2。

參考文獻(xiàn)

[1]E.J.Marinisen,B.Prince,D.Ketel-Schulz,etal.Challenges in Embedded Memory Design and Test[C].Proceedings of Desgin.Automation and Test in Europe,2005:722-727.

[2]S.Kundu,etal.Test Challenges in Nanometer Technologies[J].J.ElectronicTesting:Theory and Applications,2001,17(3/4):209-218.

[3]賽普拉斯36-Mbit和18Mbit容量的四倍速和雙倍速SRAM[EB/OL].

[4]Y.Morita et al.An Area-Conscious Low-Voltage-Oriented 8T-SRAM Design under DVS Environment[J].Digest of Tech.Papers,Symp.VLSI Circuits,2007:256-257.

[5]M.A.Turi,J.G.Delgado-Frias et al.High-Performance Low-Power SelectivPrecharge Schemes for Address Decoders[J].IEEE Transactions on Circuits and Systems,2008,55(9).

[6]K.Zhang et al.A 3-GHz 70-Mb SRAM in 65nm CMOS technology with integrated column-based dynamic power supply[J].EEE J.Solid-State Circuits,2006:146-151.

[7]C.T.Chuang,S.Mukhopadhyay,J.J.Kim,K.Kim.High-Performance SRAM in NanoscaleCMOS:Design Challenges and Techniques[J].EEE JSSCC,2007:4-12.

作者簡(jiǎn)介

唐駿(1990-),男。現(xiàn)為國(guó)防科學(xué)技術(shù)大學(xué)計(jì)算機(jī)學(xué)院碩士研究生在讀。主要研究方向?yàn)榧呻娐吩O(shè)計(jì)。

作者單位

國(guó)防科學(xué)技術(shù)大學(xué)計(jì)算機(jī)學(xué)院 湖南省長(zhǎng)沙市 410073