基于PCIE的高速圖像采集卡設計

龔曉華

摘 要:本文基于Xilinx Artix-7系列FPGA的PCIe接口設計了一套高速圖像采集卡方案,通過面向WinDriver的 PCIe設備驅動程序開發,在Windows7系統中實現了PC機對采集卡的讀、寫、DMA操作和中斷處理。經測試,PCIe x1@5GHz接口單向峰值傳輸速率達463.14MB/s,可以滿足實際應用中的高性能和可靠性要求。

關鍵詞:PCIE;FPGA ; WinDriver 圖像采集

隨著圖像處理走向高清化、智能化,人們對設備間數據傳輸速率的要求越來越高,PCIe作為計算機和外圍設備間數據交互的主流接口,已被廣泛的應用于圖像采集卡設計中。目前,實現PCIe接口有兩種方法:使用FPGA內置的PCIe專用IP,使用PCIe橋接芯片。由于FPGA應用更加靈活、成本更低,本文基于FPGA設計高速圖像采集卡。

一、圖像采集卡設計

(一) PCIe圖像采集卡設計

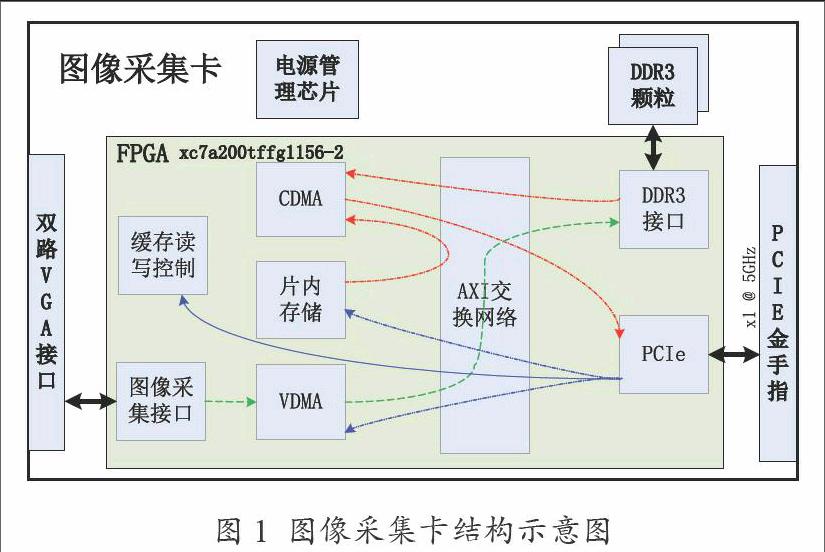

如圖1所示,圖像采集卡基于Xilinx公司的Artix-7系列xc7a200tffg1156-2 FPGA芯片,該型FPGA內集成有PCIe硬核,用于實現采集卡和PC間的數據交換,本設計使用x1模式,傳輸速率5Gbps,理論帶寬500MB/s。圍繞FPGA構建常用外設,如雙路差分VGA接口和DDR3存儲,用于圖像采集和數據存儲;電源管理模塊實時檢測采集卡上的關鍵電壓信號。

(二)圖像采集卡工作原理

數據流方面,如圖1所示,圖像數據通過差分VGA接口進入FPGA內部,接口適配模塊實現VGA時序向AXI-Stream[1]時序的轉化,VDMA模塊將圖像流緩存到DDR3中的循環緩沖中,并以中斷方式向緩存讀寫控制模塊報告寫入情況;當緩存讀寫控制模塊判定循環緩沖中有剩余數據時,通知CDMA模塊發起PCIe寫DMA,將DDR3中數據通過PCIE模塊發送到PC緩存,再以消息方式告知PC DMA發送完畢,PC機最終向圖像流數據緩存寫特定數據報告循環緩沖讀取情況。

控制流方面,PC需通過PCIe寫VDMA和CDMA模塊以分配板載DDR循環緩沖地址,并將PC端的緩存地址寫入片內存儲器中以配置CDMA模塊的鏈式DMA功能。

二、軟硬件程序開發

(一) FPGA硬件程序開發

如圖1所示,FPGA中各組件通過AXI協議互聯,構成了一個小型SoC網絡[2]。利用vivado工具提供的Block Design設計流程,添加各標準IP,按實際訪存需求進行連線,并分配全局地址。其中關鍵的PCIe模塊參數配置如下:Endport device, Lane Width x1, Link Speed 5.0GT/s, PCIE:BAR0 Memory 64KB Translation DDR_ADDR(PC對片上DDR訪問),PCIE:BAR1 Memory 64KB Translation C/VDMA_ADDR(PC對DMA控制器訪問),AXI:BARS:用1個且動態可配,AXI:System:32位地址128位數據。

(二) PC端PCIe驅動開發

PCIe驅動開發使用Jungo公司的WinDriver工具。首先在圖形界面下打開待測PCIe設備,并對FPGA典型地址進行讀寫測試,最終生成驅動代碼。其次提取xxx_bsp.h和xxx_lib.c等核心文件,構建PCIe驅動動態鏈接庫,實現DeviceFindAndOpen、DeviceClose、WDC_DMAContigBufLock、WDC_DMABufUnlock、ReadReg32、WriteReg32等基本函數。最終,按采集卡工作原理編寫應用程序。

三、驗證結果

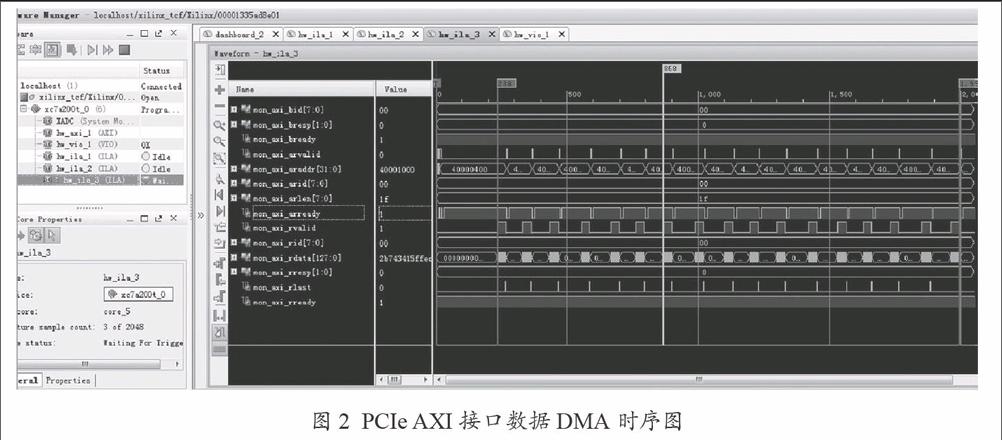

在該設計中,我們設計了基于PCIe接口的高速圖像采集卡,構建了FPGA片上SoC系統,通過PC端PCIe驅動的開發,實現了完整的圖像數據采集功能,在x1、5GHz傳輸速率條件下實現了PCIe接口實際傳輸帶寬463.14MB/s,滿足實際圖像采集要求,系統運行是穩定可靠的。圖2為Vivado環境下Hardware Manager工具提取的PCIe IP AXI接口數據傳輸時序圖。

四、結論

本文設計了一款基于FPGA的PCIe高速圖像采集卡,并通過FPGA實測,系統穩定可靠運行,滿足實際系統應用需求。

參考文獻:

[1] AXI Video Direct Memory Access v6.2. Xilinx, 2015.

[2] PCI Express Endpoint-DMA Initiator Subsystem. Xilinx, 2013.