多帶Chirp發射機在USRP2上的實現

黃世盼

(桂林電子科技大學 信息與通信學院,廣西 桂林 541004)

?

多帶Chirp發射機在USRP2上的實現

黃世盼

(桂林電子科技大學 信息與通信學院,廣西 桂林 541004)

多帶Chirp通信系統是在Chirp通信系統中引入多載波技術,使系統的抗干擾能力和調制效率得以增強。在基于USRP2射頻平臺上實現了總帶寬為20 MHz的多帶Chirp通信系統發射機,利用USRP2板載FPGA實現收發基帶信號處理。結合Chirp調制波形的特點,對存儲Chirp波形數據的雙口ROM進行復用,從而節省了FPGA的存儲空間,實現的收發系統在1 km距離上進行了高速通信。

線性調頻信號;多帶發射機;USRP2

0 引言

線性調頻(Chirp)信號既是作為雷達信號,也是一種有效的通信信號。由于Chirp信號為多普勒寬容信號[1],其幅值是恒定的,利于提高峰值功率受限系統的發射效率[2];其具有良好抗干擾能力[3]和脈沖壓縮特性[4]。因為同時具有探測和通信能力,近年來獲得了廣泛的關注。

USRP2作為軟件無線電外設的典型代表[5-6],可以很好地解決傳統Chirp通信系統中集成度低、可復制性差、易于受外界干擾和系統性能不穩定等問題[7]。應用USRP2實現Chirp通信系統,具有易于實現、修改和擴展等優勢,具有相當高的研究價值。

常規USRP2僅支持基于PC端GUNRadio的主機工作模式,對于大帶寬信號要求的高采樣速率,主機工作模式很難滿足。本文采用對USRP2板載FPGA直接編程的方式,將基帶處理轉移到USRP2上實現。

1 Chirp信號時頻特性

Chirp信號是一種瞬時頻率隨時間線性變化的信號,Chirp信號的表達式為:

s(t)=Aej[2π(f0t+μt2/2)+θ0], |t|≤T/2。

(1)

式中,A為Chirp信號幅度;T為Chirp信號符號周期;f0為Chirp信號的中心頻率;μ為Chirp信號的調頻斜率;θ0為Chirp信號的初始相位。可得Chirp信號的瞬時頻率表達式為:

(2)

Chirp信號的斜率μ表示信號瞬時頻率的變化速率,當μ>0時稱為上掃頻(UpChirp)信號,Chirp信號的瞬時頻率隨時間的增加不斷增大;當μ<0時稱為下掃頻(DownChirp)信號,Chirp信號的瞬時頻率隨時間的增加不斷減小。

根據最佳接收原理可知對于一個線性的信號,匹配濾波器的沖擊響應同樣是一個線性的信號,調頻斜率互為相反數。則有Chirp信號的脈沖壓縮可以利用匹配濾波器實現,其匹配濾波器的沖擊響應h(t)是s(t)反演后再取共軛,對于式(1)來說,時間反轉相當于調頻斜率取相反數。即DownChirp相應的匹配濾波器的沖擊響應為UpChirp,而UpChirp相應的匹配濾波器的沖擊響應為DownChirp。當Chirp信號經過匹配濾波器之后輸出的結果為s(t)和h(t)卷積的結果,即[8]

sMF(t)=s(t)*h(t)=

(3)

2 多帶Chirp發射機設計

在高速率的大帶寬Chirp通信系統中,單頻帶進行數據傳輸時符號寬度會小于大量的多徑時延擴展,此時會引起嚴重的ISI,無法保障Chirp通信系統的可靠性。多載波技術是將數據流分成若干個子數據流,從而使子數據流具有低得多的傳輸比特速率,然后利用這些數據流分別去調制若干個載波,最后將調制信號合成后傳輸。多載波調制對于信道的時間彌散性不敏感,在Chirp通信系統中引入多載波技術可以增強系統抗衰落性能,利于實現高速無線通信。

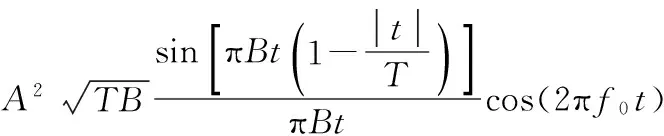

Chirp通信系統中引入多載波技術形成多帶Chirp通信系統,其頻譜結構如圖1所示,總帶寬被分為N個子頻帶,各個子頻帶內都進行調制。

多帶Chirp發射機的設計框圖如圖2所示。可以看到,整個發射機設計先將二進制碼元輸入串并轉換器進行串并轉換,降低數據傳輸的速率;再將低速的數據分別輸入各自的調制器進行調制,調制后的信號在時域上直接進行累加;最后將累加得到的多帶調制信號經DAC轉換后,進行上變頻將信號搬移至發射頻段進行發射。

圖1 多帶Chirp通信系統頻譜結構

圖2 多帶Chirp發射機框圖

3 USRP 2硬件配置

要實現多帶Chirp發射機,需要對USRP2的硬件進行配置。配置時鐘芯片AD9510給PFPGA,DAC和ADC提供時鐘;配置本振頻率合成器ADF4360-0將基帶信號進行上變頻;配置數模轉換器AD9777將信號由數字信號轉換為適合在信道中傳輸的模擬信號。具體配置如下:

3.1時鐘芯片

USRP2中采用的時鐘分配芯片是AD9510。AD9510提供多路輸出時鐘分配功能,它具有低抖動和低相位噪聲特性,能夠極大地提升數據轉換器的性能[11]。在USRP2中,AD9510為其他模塊提供時鐘,包括FPGA,數模轉換器和模數轉換器。

AD9510的串口控制端口支持SPI協議,因此可以通過SPI來實現寄存器的讀寫操作。通過SPI配置地址為0x40,0x42,0x45,0x4F,0x54,0x5A的寄存器以滿足系統設計需求,其他寄存器均為默認值。地址0x40,0x42的寄存器設定值為0Eh表示COMS輸出,禁止反向COMS驅動;地址0x45的寄存器設定值為01 h表示CLK1作時鐘輸出;地址0x4F的寄存器設定值為80 h表示設置DAC工作時鐘;地址0x54的寄存器設定值為11 h表示設置本振工作時鐘;地址0x5A的寄存器設定值為01 h表示將配置寫入對應的寄存器。AD9510通過SPI進行配置時,注意要先將管腳21(CSB)置低,然后輸入指令到SDIO口,每配置完一個寄存器后需將CSB置高保持3 ns,然后將CSB置低后再配置下一個寄存器。

3.2本振合成器

RFX2400子板上使用的頻率合成器是一款完全集成的整數N分頻合成器和VCO的ADF4360-0[12]。ADF4360-0中晶振的輸出頻率和本振的輸出頻率滿足關系式:

fVCO=N×fPD=(P×B+A)×(fREFIN/R)。

(6)

要實現本振頻率合成,需要對R Counter Latch、Control Latch和N Counter Latch三個寄存器進行配置。以設計2.44 GHz本振頻率為例:寄存器R設定值為300 015 h,表示Band Clock(小于1 MHz)選擇8分頻,反后沖脈沖寬度3.0 ns,R計數器配置;寄存器C設定值為c6f124 h,表示預分頻器設定值為32/33,電荷泵增益為1,電荷泵電流為1.25 mA,輸出功率等級為11 mA,-6 dBm(50 Ω),相位檢測為負極,MUXOUT引腳輸出數字鎖定探測信號,核心功率等級為10 mA;寄存器N設定值為000f22 h,表示本振輸出不分頻,計數器A配置,計數器B配置。需要注意的是,寄存器配置寫入時是有順序要求的,寫入的順序依次為R Counter Latch、Control Latch、N Counter Latch。

3.3數模轉換器

USRP2的主數模轉換器(DAC)是雙通道16 bit的AD9777[13]。通過SPI標準接口對寄存器配置可以完成AD9777的所有寄存器配置。地址為0x00的寄存器控制AD9777的全局工作狀態,設定值為04 h表示SDIO作為SPI的輸出,MSB優先,1R模式。地址為0x01~0x04的寄存器配置AD9777的功能實現。地址為0x01的寄存器可控制調制方式、調制效率和內插速率等,設定值為84 h表示4倍內插,無正交調制,插值無0填充,選用實數模式,8管腳輸出輸入數據時鐘(DATACLK)。地址為0x02的寄存器可配置輸入數據格式,輸入模式(單雙口)等,設定值為00 h表示輸入為有符號數據輸入模式為雙口。地址為0x03的寄存器可配置DAC的分頻比以及設定管腳53或管腳8作為輸出功能管腳,設定值為00 h表示DAC的分頻比為1,管腳8作為輸出DATACLK。地址為0x04的寄存器可配置PLL的工作狀態等,設定值為80 h表示啟用鎖相環,自動控制電荷泵。

4 多帶Chirp發射機在USRP2上的實現

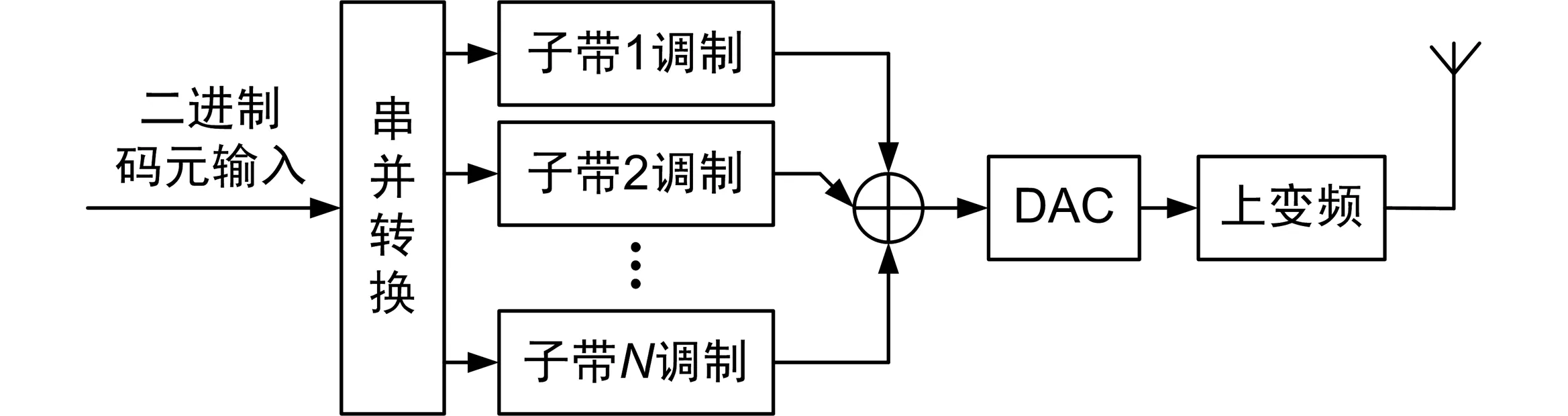

Chirp信號產生的主要方式為直接數字波形合成(DDS)[14-15],在工程當中,Chirp信號的實部和虛部存在USRP2中FPGA的雙口ROM中。由于UpChirp信號實部/虛部鏡像翻轉后可以得到DownChirp信號的實部/虛部,故雙口ROM中只需存入UpChirp與DownChirp信號其中一種信號即可,這樣可以使數據少存儲一半,節省了FPGA的資源。雙口ROM復用基本原理如圖3所示,雙口ROM中存儲UpChirp信號的實部和虛部數據,當碼元為1時選用UpChirp地址發生器,同時從地址1和地址N+1往下讀取實部和虛部數據,輸出即為UpChirp信號;當碼元為0時選用DownChirp地址發生器,同時從地址N和地址2N往上讀取實部和虛部數據,輸出即為DownChirp信號。圖3中的N由碼元速率和DAC采樣頻率確定。

圖3 雙口ROM復用基本原理

由于USRP2使用的射頻子板RXF2400射頻帶寬有限,故在USRP2上實現為單子帶帶寬為2.5 MHz,碼元速率為0.5 MHz,總帶寬為20 MHz,8子帶的多帶Chirp發射機系統。USRP2中主DAC為16 bit的AD9777,其工作頻率為100 MHz,故N=100 MHz/0.5 MHz=200。設置雙口ROM位寬為16 bit,存儲深度為400。ROM前半部分[0:200]存儲實部,ROM后半部分[201∶400]存儲虛部。使用雙口ROM后輔以邏輯控制,可以節省FPGA中一半的存儲資源。

在產生Chirp波形時為了抑制子帶間的互干擾,在時域中加入了成型濾波器,所以每個碼元調制輸出的信號兩端都有衰減,但是Chirp信號的特征值不變,所以不會影響接收端的檢測。

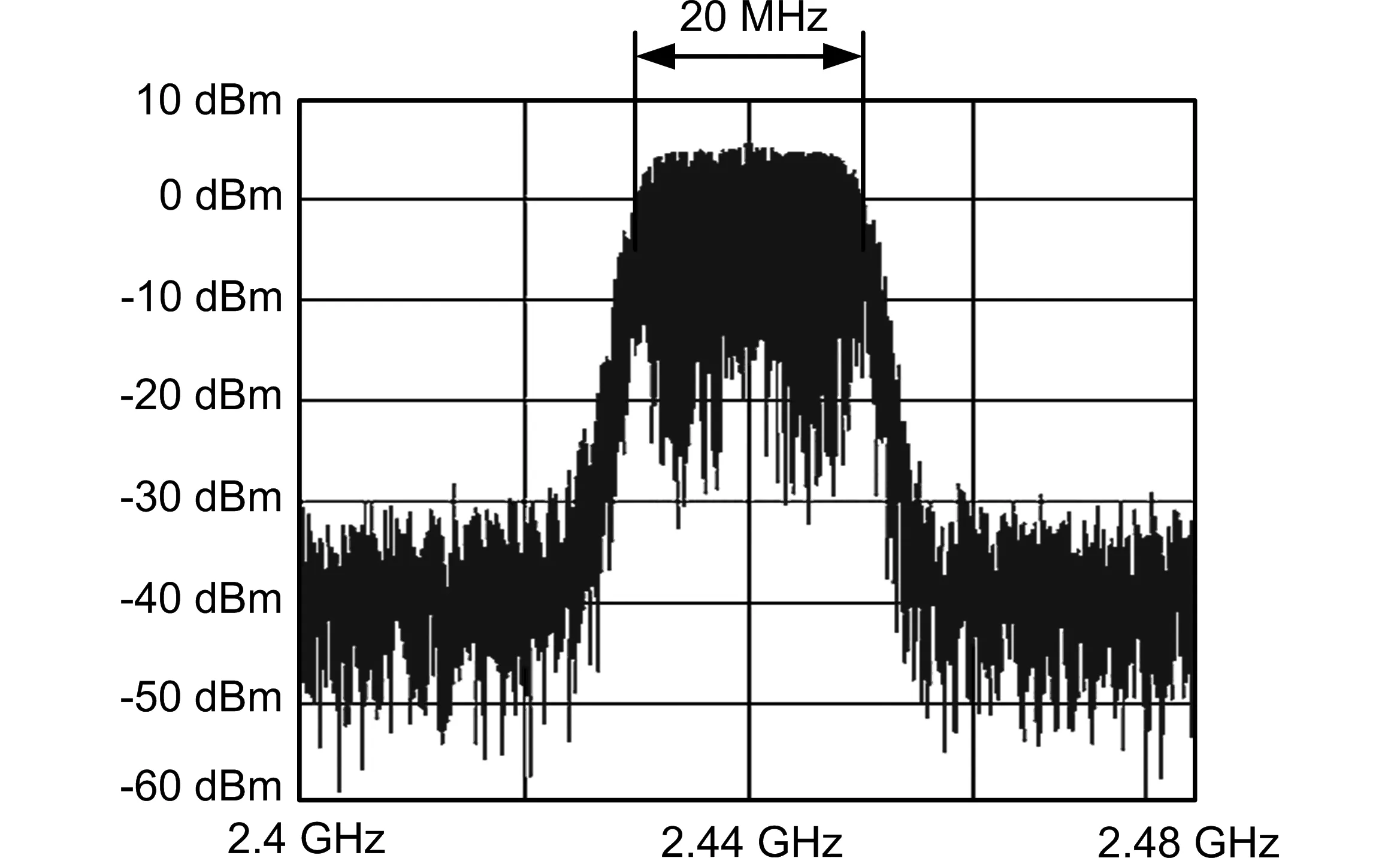

Xilinx ISE的ChipScope捕獲的8個子帶實部以及8子帶實部累加后的波形如圖4所示。因為系統使用的是復調制,中間的2個子帶最高頻率相同,越往兩邊,子帶的最高頻率就越大,而DAC轉換頻率不變,所以就得到了如圖4所示的波形。在USRP2平臺上實現的總帶寬為20 MHz的多帶Chirp發射機的發射頻譜如圖5所示。從圖5中可以看到使用成型濾波器后的帶內頻譜平坦,帶寬外的噪聲得到了抑制,利于接收端進行子帶分離。

圖4 ChipScope捕獲的8個子帶的實部波形

圖5 多帶Chirp發射機實時頻譜

5 結束語

本文提出了Chirp通信系統和多載波技術結合的多帶Chirp通信系統,用直接數字波形合成方式實現產生Chirp信號。在USRP2上Verilog HDL語言編寫信號處理程序和配置主要芯片,并對雙口ROM進行復用,減少了FPGA上資源的消耗,實現了8個子帶。總帶寬為20 MHz多帶Chirp發射機系統。

[1]KIM K T.Focusing of High Range Resolution Profiles of Moving Targets Using Stepped Frequency Waveforms[J].IET Radar,Sonar & Navigation,2010,4(4):564-5-175.

[2]PATTON L,FROST S,RIGLING B.Efficient Design of Radar Waveforms for Optimized Detection in Colored Noise[J].IET Radar,Sonar & Navigation,2012,6(1):21-29.

[3]周昱昕,包衛東.一種基于Frft的BOK-Chirp信號擴頻通信的方法[J].無線電工程,2014,44(9):32-34.

[4]YOON C,LEE W,SONG J H,et al.New Baseband Pulse Compression for Chirp Coded Excitation[C]∥IEEE International Ultrasonics Symposium (IUS),2013:906-909.

[5]HUMPHRIES J R,GALLAGHER M W,GALLAGHER D R,et al.Interrogation of Orthogonal Frequency Coded SAW Sensors Using the USRP[C]∥Frequency Control Symposium & the European Frequency and Time Forum (FCS),2015 Joint Conference of the IEEE International.Denver,2015:530-535.

[6]黃凌.基于GNU Radio和USRP的認知無線電平臺研究[D].廣州:華南理工大學,2010.

[7]李賽.基于Chirp信號的超寬帶認知無線電(CUWB)技術研究[D].北京:北京郵電大學,2009.

[8]CHARLES E.COOK M B.Radar Signals:an Introduction to Theory and Application[M].USA:Academic Press,1967:168-185.

[9]隋占菊,劉麗哲,陳強輝.2Mbps Chirp-QPSK調制解調器設計與實現[J].無線電通信技術, 2010,36(5):46-48.

[10]王力男.衛星通信系統中Chirp信號設計與捕獲[J].無線電通信技術,2011,37(6):58-60.

[11]Analog Device Inc.AD9510Datashteet [EB/OL],2005.http://www.analog.com/media/cn/technical-documentation/data-sheets/AD9510_cn.pdf

[12]Analog Device Inc.ADF4360-0Datashteet [EB/OL].2012-11.http://www.analog.com/media/cn/technical-documentation/data-sheets/ADF4360-0.pdf

[13]DEVICES A.AD9777 16-Bit,160 MSPS 2/4/8 Interpolating Dual TxDAC+ D/A Converter[Z],2002.

[14]常文革,祝明波,梁甸農.寬帶線性調頻信號產生技術研究[J].信號處理,2002,18(4):125-130.

[15]霍志勇,張軍.DDS線性調頻信號產生技術研究[J].無線電工程,2006,36(1):27-29.

黃世盼男,(1989—),碩士研究生。主要研究方向:Chirp通信與傳感一體化。

Implementation of Multi-band Chirp Transmitter on USRP2

HUANG Shi-pan

(SchoolofInformationandCommunicationEngineering,GuilinUniversityofElectronicTechnology,GuilinGuangxi541004,China)

Multi-band Chirp communication system is a Chirp communication system that introduces multicarrier.It makes the anti-interference performance and modulation efficiency of the system enhanced.In this paper,a multi-band Chirp transmitter system with a total bandwidth of 20 MHz is implemented based on USRP2 platform.Combined with the characteristics of the Chirp modulation waveform,the dual port ROM which stores the Chirp waveform data is multiplexed,thus saving the storage space of FPGA.The implementation of the transceiver can communicate at high speed in the 1 km distance.

chirp signal;multi-band chirp transmitter;USRP2

10.3969/j.issn.1003-3106.2016.10.16

2016-07-05

國家自然科學基金資助項目(61362006);廣西自然科學基金資助項目(2014GXNSFBA118288);省部共建認知無線電重點實驗室課題(2013ZR08);桂林電子科技大學研究生教育計劃資助項目(YJCXS201517)。

TP391.4

A

1003-3106(2016)10-0065-04

引用格式:黃世盼.多帶Chirp發射機在USRP2上的實現[J].無線電工程,2016,46(10):65-68.