基于FPGA的ADS-B信號解碼的設計

胡安營,王 濤

(山東航空股份有限公司,山東 濟南 250000)

基于FPGA的ADS-B信號解碼的設計

胡安營,王 濤

(山東航空股份有限公司,山東 濟南 250000)

文章介紹了基于1090ES數據鏈技術的廣播式自動相關監視設備(ADS-B)的解碼流程;給出了FPGA和DSP信息提取的實現方案。通過ADS-B標準解碼方式,文章采用Verilog編程語言和C語言完成了其各個功能模塊的設計。實驗結果表明,該方案可以實現ADS-B信號信息的提取,并可以提取ADS-B信號所包含的信息。

ADS-B;現場可編程門陣列;數字信號處理

廣播式自動相關監視(ADS-B)接收機是基于衛星定位系統的飛行器運行監視技術的地/空、空/空信息地面設備。1090 ES ADS-B是基于S模式數據鏈的通信技術,可以提供通信數據帶寬為1M Bit/s。ADS-B 接收機能夠以較小的成本實現航空器動態的監視。本文主要進行了基于1090ES ADS-B接收機信號處理及解碼功能的設計與實現。

1 方案設計

1.1 系統組成

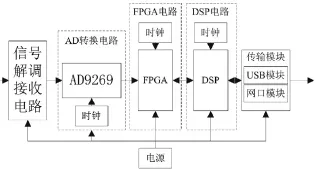

1090 ES ADS-B接收機主要由DSP處理器和現場可編輯門陣列(Field-Programmable Gate Array,FPGA)處理器、ADC電路組成。首先ADS-B載波信號經過信號解調電路,轉換為ADS-B信號,并進行ADC電路10Mbps采樣,送入FPGA和DSP中。其采樣信號在FPGA中經過一系列的數字信號處理,得到所需要的ADS-B數字信息并送入DSP處理器中,通過DSP處理器提取相關信息送至上位機。系統的框圖設計如圖1所示。

圖1 系統框圖

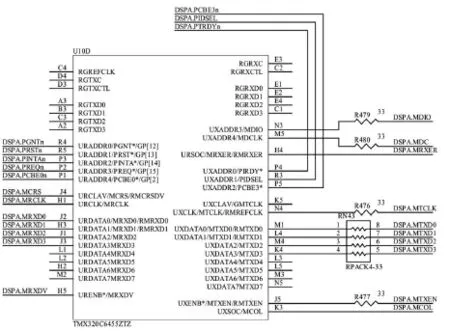

1.2 DSP處理模塊

如圖2所示,D S P處理模塊由T I的D S P處理器TMS320C6455、時鐘電路、電源模塊組成。DSP處理模塊主要用于ADS-B消息處理,對ADS-B的信號進行解碼,得到ADS-B的明文信息。

圖2 DSP電路圖

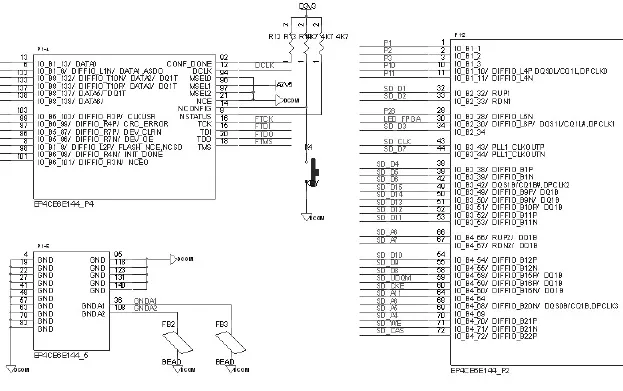

1.3 FPGA控制模塊設計

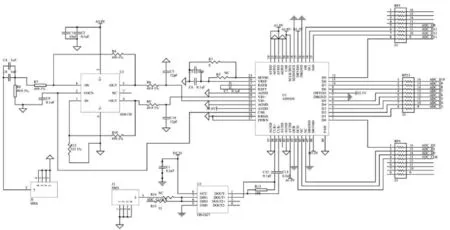

FPGA控制模塊選用ALTERA公司的EP2C5Q208C8芯片。它具有144個引腳,其中102個I/O通信口,4608個邏輯單元,288個LAB。其并行處理的特點完全以較高的速率完成ADS-B信息解碼處理,同時設計EMIF接口與DSP進行數據通信,完成ADS-B數據的提取。FPGA部分電路圖如圖3所示。

1.4 AD轉換電路設計

模數轉換電路采用ADI公司的AD 9269芯片,轉換速率可以到達60 Mps,信號分辨率高,滿足高頻小信號ADS-B的信號采樣的要求。其轉換電路如圖4所示。

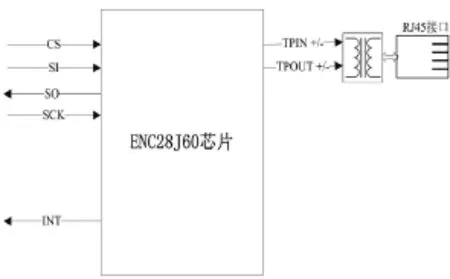

1.5 網口電路設計

數據傳輸采用網口輸出,物理芯片用的是ENC28J60。ENC28J60芯片是千兆網芯片,具有超低功耗模式和功率降低模式,能夠滿足當前設計需要。如圖5所示,其模塊主要是用戶傳遞ADS-B明文信息。

圖3 FPGA電路

圖4 模數轉換電路

圖5 網絡模塊原理圖

2 程序設計

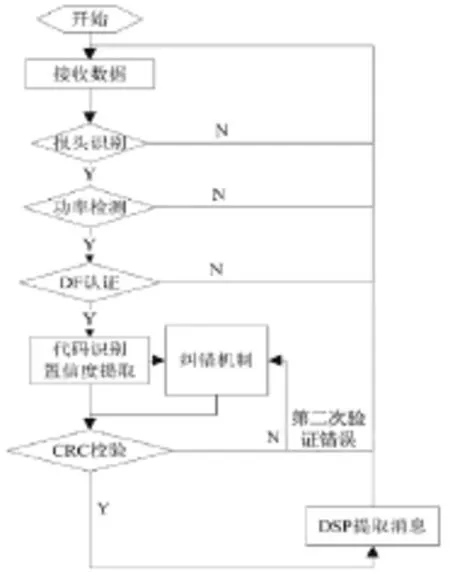

該設計的程序流程包括接收數據、判斷報頭、計算參考功率、檢測功率一致性、CRC校驗等部分。

2.1 報頭識別

判斷脈沖的位置:4出現時間分別為0 μs,1 μs,3.5 μs,4.5 μs,考慮到容錯需要,可以超前或者延后一個采樣點。

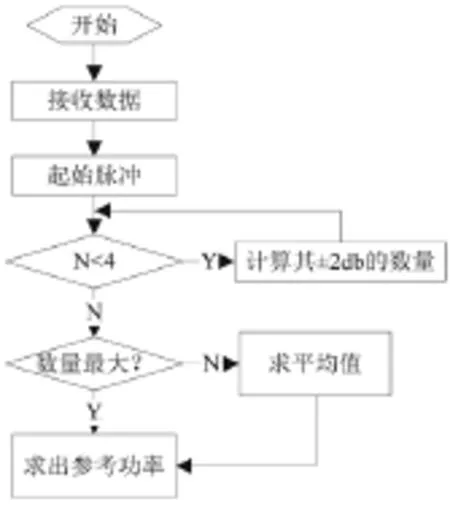

2.2 參考功率計算

在報頭識別的處理過程中,需要計算該參考的功率數值REM_PWOER,并使用該功率的參考值用于后面步驟的數據位的提取和置信度的計算,其流程如圖6所示。

圖6 參考功率計算流程圖

2.3 檢測功率一致性

ADS-B接收的解碼需要計算報頭脈沖5個采樣點的平均數值。如果報頭脈沖的平均值在報頭脈沖幅度能夠滿足在參考信號幅度的±3 dB內,則認為通過功率的一致性檢測,否則應該返回數據采集步驟,并重新判斷報頭。其程序流程如圖7所示。

2.4 總體設計的流程

如圖8所示,總體的程序流程包括接收數據、判斷報頭、計算參考功率、檢測功率一致性、CRC校驗等部分。

2.5 FPGA的實現

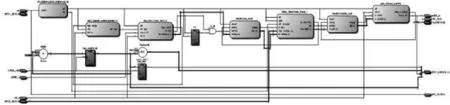

利用FPGA設計的RTL電路如圖9所示。

2.6 實驗結果分析

通過串口和網絡輸出ADS-B提取的消息:

*10780233;No-Call ;;;;;;;000;000;0;00000;

*1078056C;CSZ9676;ZH9676;ShenzhenAirlines;116.682 2;040.5287;A;34100;382;235;0;00000;

3 結語

本文研究了ADS-B接收機信號處理的設計方案,并在FPGA和DSP上實現ADS-B信號的解碼與消息的提取。下一步的設計中,ADS-B中的重疊信號的處理方法和糾錯算法還有待進一步研究。

圖7 功率檢測流程圖

圖8 總體設計流程圖

圖9 RTL電路

[1]RAJESH S,RAGHAVAN,ANALEX.Performance analysis of 1090 MHz automatic dependent surveillance broadcast(ADS-B)using OPNET modeler[M].Ohio:Brook Park,2002.

[2]朱蕓.模式S應答接收機數字處理系統設計[D].成都:電子科技大學,2006.

[3]陳士毅.模式S應答處理中的數據處理[D].成都:電子科技大學,2006.

[4]鄭超,劉志剛,王玉章.基于1090ES的ADS-B OUT系統的設計與實現[J].航空維修與工程,2010(1):56-58.

Design and implementation of ADS-B receiver signal processing based on FPGA

Hu Anying,Wang Tao

(Shandong Airlines Co.,Ltd.,Ji'nan 250000,China)

This paper introduces decoding process of broadcast automatic monitoring equipment (ADS-B)based on 109ES data chain technology and gives a implementation scheme of field-programmable gate array and DSP information extraction.Through the way of ADS-B standard decoding method,the paper complete design of moduals of all kinds of functions with Verilg programming language and C language.The experiment result showed that this scheme could realize the extraction of signal information of ADS-B and the information in it.

ADS-B;FPGA(Field-Programmable Gate Array);DSP(Digital Signal Processing)

胡安營(1983—),男,山東濟南,本科;研究方向:交通信息工程及控制。