快速鎖定的全數字延遲鎖相環研究

保慧琴,尹國福

(1.西北工業大學明德學院,西安710124;2.中國兵器工業第213研究所,西安710000)

快速鎖定的全數字延遲鎖相環研究

保慧琴1,尹國福2

(1.西北工業大學明德學院,西安710124;2.中國兵器工業第213研究所,西安710000)

為了消除芯片內部各模塊間的時鐘延時,減小時鐘相位偏移,設計了一種快速鎖定的全數字延遲鎖相環結構,只需一次調節過程即可完成輸入輸出時鐘的同步,鎖定時間短,噪聲不會積累,抗干擾性好。在監測相位差時利用一種新的相位選擇方法,配合相應的控制邏輯電路,完成DLL的快速鎖定,通過調整延遲單元的延時、個數及相應控制電路的大小,實現寬范圍的相位鎖定。SMIC 0.18μm CMOS工藝下的仿真結果表明,本設計能夠在18個周期內完成輸入時鐘和輸出時鐘的相位同步,鎖定范圍是25MHz~300MHz,最大時間抖動為35ps。

時鐘延時;時鐘補償;數字延遲鎖相環;寬范圍;快速鎖定;相位

1 引 言

隨著集成電路加工尺寸的不斷縮小,時鐘的偏斜和抖動對系統性能的影響日益明顯。為了保證芯片的內部時鐘和外部時鐘信號在高速數據交換和傳輸中保持精確同步,延遲鎖相環(DLL:Delay-Locked Loop)越來越多地被引入芯片中,用來生成穩定的延遲或多相位的時鐘信號。DLL主要分為模擬DLL和數字DLL兩種,模擬DLL[1]可以獲得好的時鐘抖動性能,但物理實現比較復雜,需要使用飽和電流源,另外,當電源電壓降低時,模擬DLL器件會遇到電壓死區問題。數字DLL的抖動性能要差一些,但是它有鎖定時間短、工藝敏感度低、低功耗等優點,并大大降低了設計難度。

現有的數字DLL大多由鑒相器、延時鏈[2]、相位選擇、控制邏輯組成。參考時鐘被傳送到系統內部所有需要觸發時鐘的寄存器,同時產生反饋時鐘,鑒相器監測參考時鐘與反饋時鐘的相位差,參考時鐘經過延時鏈產生一系列不同延遲的時鐘,數據選擇器根據相位差選擇其中一條時鐘輸出。其中相位選擇有很多種方法,但是為了實現數字DLL的快速鎖定,一般采用二進制搜索算法或時間數字轉換器(TDC)[3-5]。然而數字電路的傳播時間是有限的,為了避免二進制搜索控制器[6]發生故障,必須降低時鐘速度。另外,采用二進制搜索控制器的DLL鎖定時間比采用TDC的DLL鎖定時間長。TDC用于快速地將輸入時鐘與輸出時鐘間的時間差轉換為數字代碼,然而這些數字代碼通常由D觸發器產生,需要消耗大量的面積和功耗。

這種快速鎖定全數字DLL,在監測相位差時利用一種新的選擇信號產生電路,根據鎖存器采樣值的特性選擇相應的時鐘相位,配合特定的控制邏輯電路,在18個周期內完成輸入時鐘和輸出時鐘的相位同步,該DLL抖動時間短,頻率范圍寬,易于實現。

2 全數字DLL工作原理

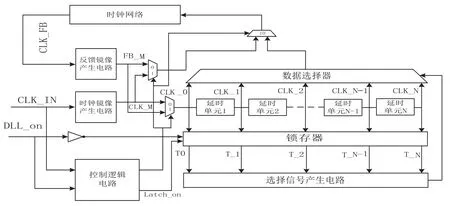

全數字DLL結構如圖1所示,由延遲單元計數電路(延時鏈、鎖存器)、數據選擇器、選擇信號產生電路以及控制電路組成。全數字延遲鎖相環的工作過程分為以下三個步驟:

第一步:輸入時鐘CLK_IN首先直接輸入至時鐘網絡形成反饋時鐘[7]CLK_FB,該反饋信號進入延遲鏈,產生一系列中間時鐘信號,鎖存器對這一系列中間時鐘信號的值進行采樣。采樣時間為反饋信號的上升沿到緊接著的輸入時鐘信號上升沿之間的時間。

第二步:選擇信號產生電路根據采樣結果產生數據選擇器的選擇信號,控制數據選擇器輸出相應的中間時鐘信號。此時,輸入時鐘進入延遲鏈,產生一系列中間時鐘信號提供給數據選擇器以選擇正確的延時補償時鐘。

第三步:數據選擇器的輸出信號輸入至時鐘網絡形成反饋信號,此時,反饋信號和輸入時鐘的相位實現了同步。

圖1 全數字DLL結構圖

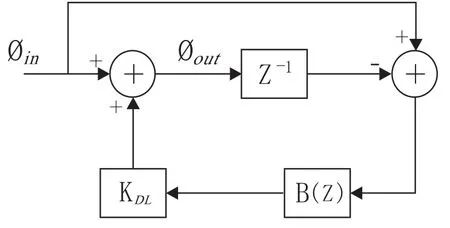

該DLL可以用圖2的線性模型分析[8],圖中KDL為延遲單元的增益,Z-1代表延遲,B(Z)為延時補償調節電路(包括數據選擇器和選擇信號產生電路)的傳輸函數,可以表示為:

圖2 DLL線性模型

該DLL的系統函數可以表示為:

其中K=0.707[7],根據公式2可以證明該DLL是穩定的。

3 全數字DLL關鍵電路設計

3.1延時單元計數電路

設計中用的延遲單元由兩個串聯的CMOS反相器組成,延遲鏈中延遲單元的個數為:

其中Tmax是最小輸入時鐘頻率,tdelay是延遲單元的延遲時間。

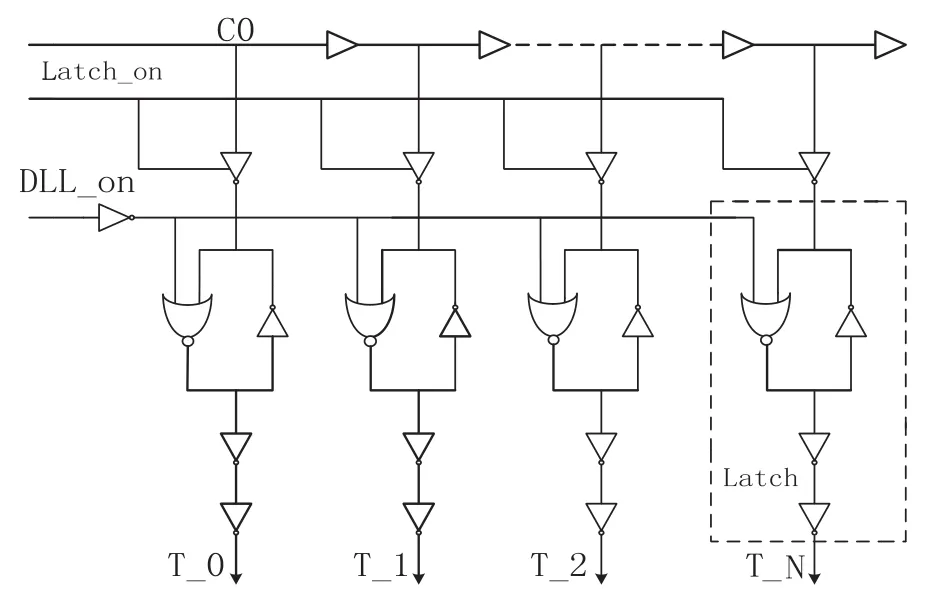

每一個延時單元都需要一個鎖存器對其輸出值進行鎖存,如圖3所示。當DLL_on=0時,鎖存器被清零,當DLL_on=1時,鎖存器開始工作。若此時控制端Latch_on為高電平,則鎖存器接收來自延時鏈的輸出信號,若控制端為低電平,則輸入端關斷,關斷前的輸入值被鎖存。輸入時鐘CLK_IN的鏡像信號CLK_M直接進入時鐘網絡產生反饋信號CLK_FB,其鏡像時鐘FB_M進入延時鏈。鎖存器鎖存時間為FB_M中間的上升沿到緊接著的輸入時鐘的上升沿。鎖存器鎖存到的“1”的個數就是需補償延時單元的個數。

圖3 延時單元計數電路結構圖

3.2選擇信號產生電路

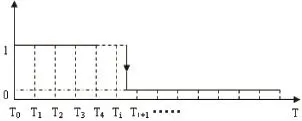

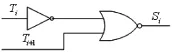

選擇信號產生電路根據鎖存器的輸出產生數據選擇器的選擇信號,控制數據選擇器輸出相應的延時時鐘。通過控制邏輯電路使得延遲調節前鎖存器的輸出Ti滿足如下特性:設延遲鏈中延遲單元的個數為N,則N位鎖存器的值T[1:N]的前i(1≤i≤N)位均為1,后N-i位均為0,如圖4所示,i由需要調節的延遲決定。通過識別Ti從1到0的跳變時刻產生數據選擇器的選擇信號Si,選擇信號產生電路單元如圖5所示。

圖4 T[1:N]值分布圖

圖5 選擇信號產生電路單元

3.3時鐘鏡像產生電路

時鐘鏡像產生電路使反饋時鐘與輸入時鐘的相位差轉化為需補償的延時單元個數,其電路圖如圖6所示。考慮到選擇信號產生電路的特殊性,為了防止延遲鏈的中間時鐘信號產生錯誤的選擇信號,必須考慮時鐘鏡像產生電路中觸發器的個數。

圖6 時鐘鏡像產生電路

圖6中的觸發器是帶置位端的上升沿D觸發器,D觸發器的個數C由下式決定:

其中Tmax為輸入到DLL的最小時鐘頻率對應時鐘周期,Tmin為最大時鐘頻率對應時鐘周期。

4 仿真

為了驗證設計方案的有效性,采用SMIC 0.18μm CMOS工藝進行了數字DLL設計,工作電壓1.8伏,輸入時鐘的頻率范圍為25MHz- 300MHz。綜合考慮精度和面積等因素,所設計的延時單元的延時為80ps。延時鏈包含500個延遲單元,時鐘鏡像產生電路中觸發器的個數為13個。

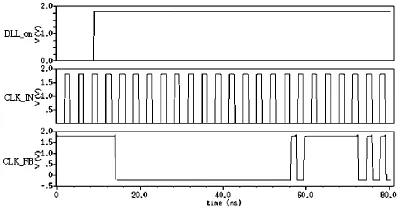

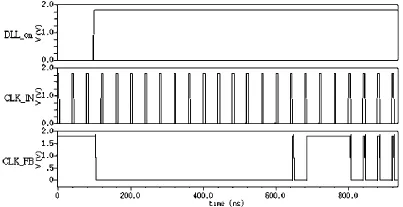

圖7和圖8分別給出輸入時鐘頻率為25MHz和300MHz時的仿真結果。通過對比輸入時鐘CLK_IN和反饋時鐘CLK_FB可以看出,延時補償在DLL_on變為高電平的十八個周期內完成。輸入時鐘與輸出時鐘的最大延時為35ps。

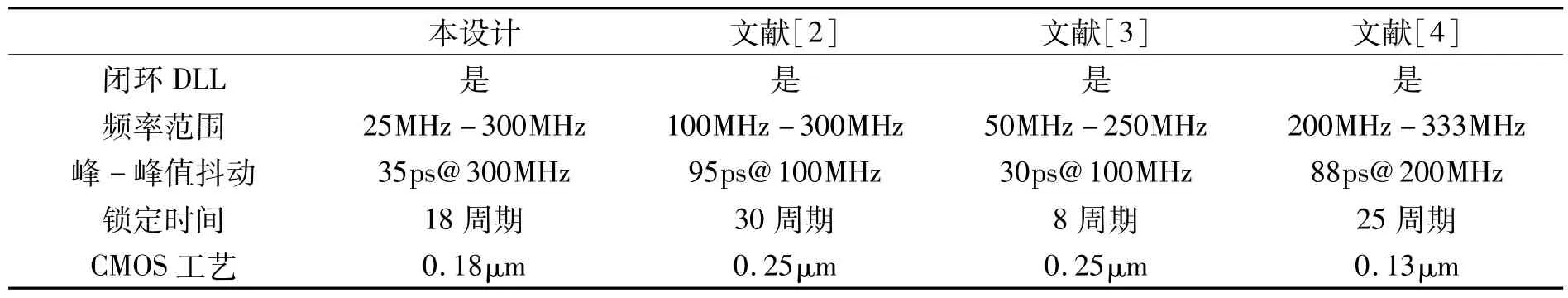

表1給出了所設計的全數字DLL與文獻中DLL的性能參數比較。可以發現,所設計的全數字DLL鎖定頻率范圍寬,能夠快速鎖定,且具有較小的抖動。無論是抖動特性還是鎖定時間,本設計都好于文獻2和文獻4。雖然與文獻3比,鎖定時間較長,抖動特性也略差,但是本設計只在控制邏輯部分使用了少許觸發器,大大降低了功耗。

圖7 25MHz時的仿真波形

圖8 300MHz時的仿真波形

表1 全數字DLL性能比較

5 結束語

隨著集成電路工藝和集成系統的不斷發展,時鐘信號在高速數據交換和傳輸中必須保持同步。數字DLL以設計難度低、鎖定時間短、工藝敏感度低、低功耗等優點,越來越多地被引入系統芯片中,但其抖動性能要差于模擬DLL。本文設計了一種快速鎖定的全數字延遲鎖相環結構,在輸入時鐘頻率不變的情況下,只需一次調節過程即可完成輸入輸出時鐘的同步,且噪聲不會積累。仿真結果表明,在0.18μm CMOS工藝下,對于25MHz-300MHz的鎖定范圍,該DLL能夠在18個周期內完成輸入時鐘和輸出時鐘的相位同步,最大時間抖動為35ps。另外,該結構適用于各種加工尺寸的CMOS工藝,通過調整延遲單元的延時、個數及相應控制電路的大小,進而調整鎖定范圍和精度,可以使得該DLL勝任不同領域的應用。

[1]You-Jen Wang,Shao-Ku Kao.All-Digital Delay-Locked Loop/Pulsewidth-Control Loop with Adjustable Duty Cycles[J].IEEE Journal of Solid-state circuits,2006,41(6):653-712.

[2]G K Dehng,J M Hsu,C Y Yang.Clock-deskew buffer using a SAR-controlled delay-locked loop[J].IEEE J.Solid-State Circuits,2000,35(8):1128-1136.

[3]J S Wang,Y M Wang,C H Chen.An ultra-low-power fast-lock-in small-jitter all-digital DLL[J].IEEE Int.Solid-State Circuit Conf,2005,41(6):422-423.

[4]T Hamamoto,K Furutani,T Kubo.A 667-Mb/s operating digital DLL architecture for 512-Mb DDR SDRAM[J].IEEE J.Solid-State Circuits,2004,39(6):194-206.

[5]S Kao,S I Liu.All-digital clock deskew buffer with variable duty cycle[J].IEICE Trans.Electron,2006,40(6):753-760.

[6]J.-T.Kwak,C.-K.Kwon,K.-W.Kim.Low cost high performance register-controlled digital DLL for 1 Gbps_32DDR SDRAM[J].in Symp.VLSI Circuits Dig.Tech.Papers,2003,40(5):283-284.

[7]Shao-Ku Kao,Bo-Jiun Chen,Shen-Iuan Liu.A 62.5-625-MHz Anti-Reset All-Digital Delay-Locked Loop[J].IEEE Transactions on circuits and systems,2007,54(7):182-204.

[8]Yi-Ming Wang,Jinn-Shyan Wang.An all-digital 50%duty-cycle corrector[J].IEEE International Symposium on Circuits and Systems,2004,2(3):925-928.

A Fast-locking All-digital Delay-locked Loop

Bao Huiqin1,Yin Guofu2

(1.Ming De College,Northwestern Polytechnical University,Xi'an 710124,China;2.The 213 Research Institute of China Ordnance Industry,Xi'an 710000,China)

In order to eliminate the clock delay among the different modules on a chip and reduce the phase shift of the clock,a new structure of a fast-locking all-digital delay-locked loop is presented in this paper,which can complete input and output clock synchronization with only once adjustment.Utilizing a new method of phase selector when detecting the phase difference to achieve the fast locking of DLL,by adjusting the delay of delay units,the number of delay units and the size of the corresponding control circuit,a wide range of phase-locking can be obtained.The simulation results in the SMIC 0.18μm CMOS technology show that this design can complete the phase synchronization of input clock and output clock within 18 cycles,with the locking frequency range of 25MHz~300MHz and the peakto-peak jitter of 35ps.

Clock delay;Clock compensation;Digital delay-locked loop;Wide range;Fastlocking;Phase

10.3969/j.issn.1002-2279.2016.01.003

TN79

A

1002-2279(2016)01-0011-04

保慧琴(1986-),女,青海省西寧市人,助教,碩士研究生,主研方向:數字延遲鎖相環。

2015-05-28