3D SRAM中TSV開路測(cè)試算法研究與實(shí)現(xiàn)*

趙振宇,鄧 全,李 鵬,蔣劍鋒,曲連華,唐皓月

(國防科技大學(xué) 計(jì)算機(jī)學(xué)院, 湖南 長(zhǎng)沙 410073)

?

3D SRAM中TSV開路測(cè)試算法研究與實(shí)現(xiàn)*

趙振宇,鄧 全,李 鵬,蔣劍鋒,曲連華,唐皓月

(國防科技大學(xué) 計(jì)算機(jī)學(xué)院, 湖南 長(zhǎng)沙 410073)

基于三維集成電路技術(shù)實(shí)現(xiàn)的三維靜態(tài)隨機(jī)存儲(chǔ)器,其電路中使用了大量的過硅通孔。目前過硅通孔制造工藝尚未成熟,使得過硅通孔容易出現(xiàn)開路或短路故障,從而給三維靜態(tài)隨機(jī)存儲(chǔ)器的測(cè)試帶來新的挑戰(zhàn)。現(xiàn)有的過硅通孔專用測(cè)試方式雖然能夠探測(cè)出過硅通孔的故障,但需要特定的測(cè)試電路來實(shí)現(xiàn),這就增加了額外的面積開銷,同時(shí)加大了電路設(shè)計(jì)的復(fù)雜度。因此,提出一種使用測(cè)試算法來探測(cè)過硅通孔開路故障的方法。在不增加額外面積開銷的情況下,通過內(nèi)建自測(cè)試電路解決三維靜態(tài)隨機(jī)存儲(chǔ)器中過硅通孔的開路故障檢測(cè)問題。結(jié)果顯示,該過硅通孔測(cè)試算法功能正確,能夠準(zhǔn)確探測(cè)到過硅通孔的開路故障,并快速定位過硅通孔的開路位置。

三維集成電路;過硅通孔;開路故障;測(cè)試;算法

基于三維集成電路(Three Dimensional-Integrated Circuit, 3D-IC)技術(shù)的三維靜態(tài)隨機(jī)存儲(chǔ)器(Three-Dimensional Static Random Access Memory, 3D SRAM)采用多層器件結(jié)構(gòu)組成,通過內(nèi)在的垂直互連介質(zhì)過硅通孔(Through Silicon Via, TSV)完成不同層器件之間的通信[1]。3D SRAM擁有2D SRAM所不具有的很多優(yōu)勢(shì),例如可以縮短管芯(die)與管芯(die)之間的互連線長(zhǎng)度,提高輸入/輸出(Input/Output, IO)帶寬,從而減小互連線延遲,提升性能,并降低功耗[2]。3D SRAM還可以進(jìn)行異質(zhì)集成,以此縮小設(shè)計(jì)面積和制造成本。

3D SRAM中有超過數(shù)以萬計(jì)的TSV,由于TSV的制造工藝尚不成熟,銅柱內(nèi)約有42%的概率產(chǎn)生氣泡或空隙[3],從而導(dǎo)致TSV產(chǎn)生開路故障;又由于TSV之間寄生耦合電容的影響,TSV存在開路故障時(shí),浮空導(dǎo)線與相鄰導(dǎo)線之間的寄生耦合電容對(duì)浮空端的電壓影響很大。在TSV尺寸繼續(xù)減小的情況下,TSV之間的間距也越來越小,這種耦合效應(yīng)也越明顯,不僅影響自身,而且還可能影響周圍的電路,最終導(dǎo)致SRAM失效。相關(guān)研究表明,規(guī)模為104個(gè)TSV的芯片中出現(xiàn)TSV失效的概率為63.214%[4],嚴(yán)重影響3D芯片的良品率。因此,如何有效地對(duì)TSV進(jìn)行測(cè)試是3D-IC中急需解決的問題。近年來學(xué)術(shù)界和工業(yè)界對(duì)片上TSV測(cè)試結(jié)構(gòu)的研究從未中斷過。

文獻(xiàn)[5]提出了一種用于TSV故障診斷的內(nèi)建自測(cè)試(Built-In Self Test, BIST)結(jié)構(gòu),并將TSV建模為2D矩陣的形式。盡管這種測(cè)試結(jié)構(gòu)擁有面積開銷小的優(yōu)勢(shì),但一次只能測(cè)試TSV矩陣中的一行,當(dāng)TSV數(shù)量較多時(shí),將耗費(fèi)很長(zhǎng)的測(cè)試時(shí)間。而另一種BIST結(jié)構(gòu)[6]使用基于KAF(Kth-Aggressor-Fault)可編程模型產(chǎn)生有效測(cè)試序列,用于探測(cè)TSV之間的串?dāng)_故障,這種結(jié)構(gòu)可以提供更精準(zhǔn)的TSV測(cè)試結(jié)果。然而,由于每個(gè)TSV都需要單獨(dú)的發(fā)送器和接收器,這將需要很大的面積開銷。輸出閾值分析測(cè)試結(jié)構(gòu)[7]通過使用環(huán)形振蕩器來探測(cè)TSV的故障。這種結(jié)構(gòu)能有效處理由TSV故障引起的信號(hào)延時(shí)問題,并且具有面積開銷小的優(yōu)勢(shì),但能探測(cè)的TSV故障類型有限。

針對(duì)3D SRAM中字線和位線TSV的全開路故障,提出了一種有效的片上TSV測(cè)試方法。將TSV測(cè)試機(jī)制與Memory BIST結(jié)構(gòu)相結(jié)合,使用測(cè)試算法來探測(cè)TSV開路故障。由于共用Memory BIST,本文所提測(cè)試方法可以有效縮短測(cè)試時(shí)間和面積開銷。結(jié)果顯示,該TSV測(cè)試算法功能正確,能夠準(zhǔn)確探測(cè)到TSV的開路故障,并快速定位TSV的開路位置。

1 TSV開路故障行為

1.1 TSV開路故障耦合模型

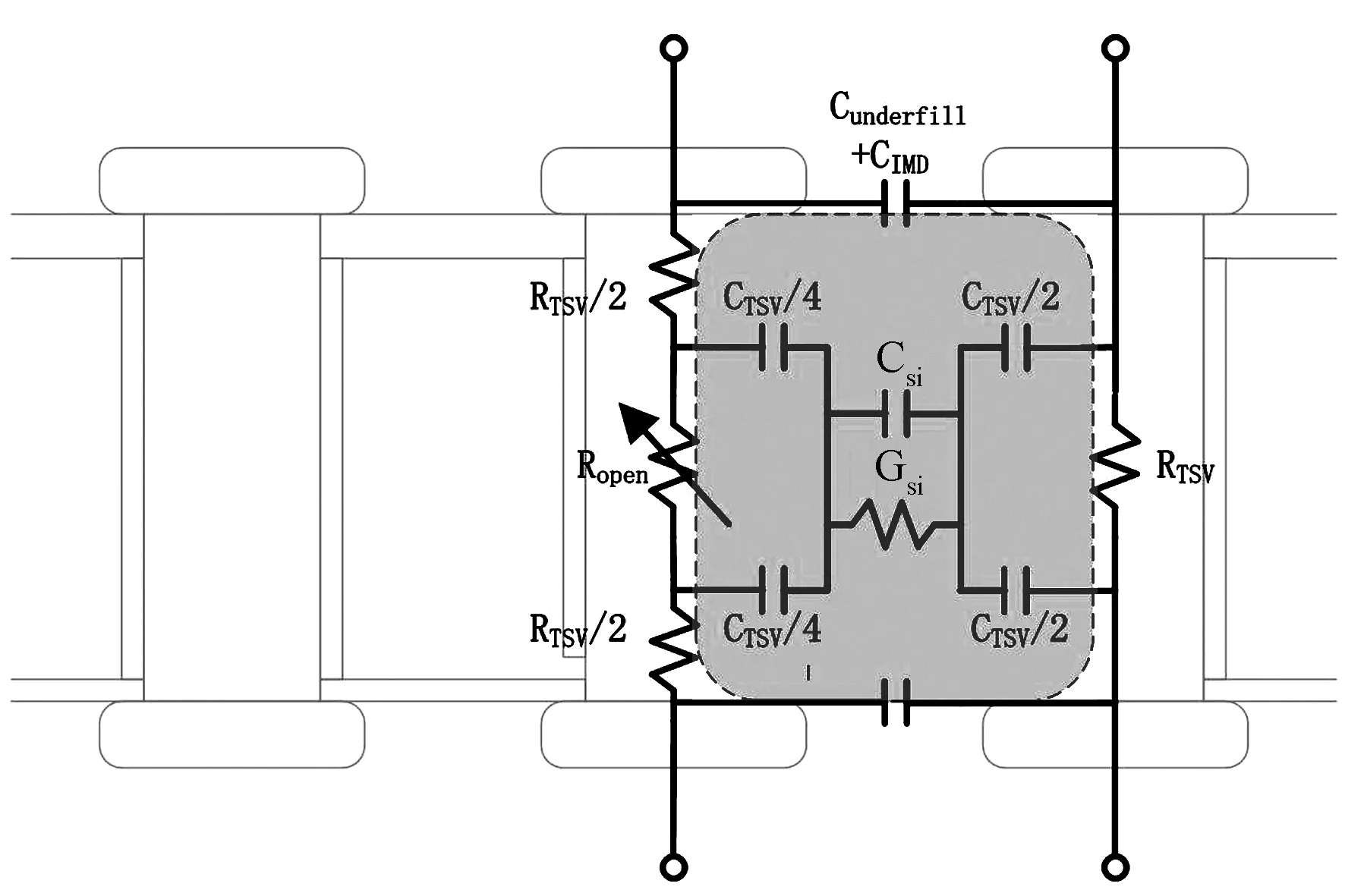

目前,對(duì)TSV的耦合電學(xué)建模研究已經(jīng)相當(dāng)深入,相比傳統(tǒng)的使用固定故障、橋接故障來分析TSV的故障,MAF(Maximum Aggressor Fault)故障模型[8]則被廣泛地應(yīng)用于探測(cè)TSV的耦合故障。文獻(xiàn)[9]結(jié)合TSV的生產(chǎn)工藝建立了TSV的串?dāng)_Spice電路模型。文獻(xiàn)[10]全面考慮了TSV的寄生分量建立了TSV耦合電學(xué)模型。為了更好地實(shí)現(xiàn)對(duì)3D SRAM中字線TSV和位線TSV的全開路故障進(jìn)行模擬以及分析TSV開路故障對(duì)存儲(chǔ)器的影響,從TSV之間的耦合效應(yīng)入手,基于TSV開路故障電學(xué)模型和TSV耦合電學(xué)模型,建立了TSV開路故障耦合效應(yīng)電學(xué)模型,如圖1所示。該模型既考慮了TSV的開路故障,同時(shí)又考慮了TSV之間的耦合效應(yīng),模型中的參數(shù)均可由文獻(xiàn)[11]中的公式計(jì)算得到。

圖1 TSV開路故障耦合效應(yīng)電學(xué)模型Fig.1 TSV open defect coupling model

1.2 TSV故障定位

3D堆疊存儲(chǔ)器可以通過多種方式來實(shí)現(xiàn),一種有效的方式是用TSV做垂直總線,將多個(gè)SRAM層連起來,接到處理器上[12];另外一種方式是將存儲(chǔ)陣列分很多小塊,并在垂直方向上進(jìn)行堆疊,用TSV代替原有互連線充當(dāng)字線和位線,并通過TSV連接到底層的外圍電路[13];本文依據(jù)第二種堆疊方式建立了圖2所示的3D SRAM電路模型。

圖2 3D SRAM電路模型Fig.2 3D SRAM model

分析電路結(jié)構(gòu)可知,TSV的開路故障既可以發(fā)生在字線上,也可以發(fā)生在位線上,且均位于TSV互連線上。根據(jù)電路結(jié)構(gòu)對(duì)稱性特點(diǎn)以及TSV開路故障的隨機(jī)性,可以將TSV開路故障的植入位置定位在四個(gè)地方(Df1~Df4)。由于存儲(chǔ)單元以陣列形式布放,字線和位線分別位于不同的邊,TSV也是按順序布放,相對(duì)位置都是對(duì)稱的,所以這四處開路故障位置足以表征整個(gè)3D SRAM中的所有TSV開路故障情況。

1.3 TSV開路故障模擬

將TSV開路故障逐一注入圖2故障位置中,采用圖1所示TSV開路故障耦合效應(yīng)電學(xué)模型,并用Hspice進(jìn)行模擬。模擬環(huán)境設(shè)置為:65 nm工藝,1.2 V電源電壓,常溫(25℃),典型corner(TT)。故障位置、操作類型、最小開路電阻值以及最大失效概率阻值整理如表1所示,TSV開路引起的SRAM失效在考慮工藝偏差情況下的最大失效率用Fmc來表示。

表1 TSV開路導(dǎo)致3D SRAM失效的最小電阻值

表1中,定義Dfi-nom為在標(biāo)稱條件下導(dǎo)致SRAM失效的TSV最小開路電阻值;定義最大失效概率阻值Dfi為在考慮工藝偏差時(shí),導(dǎo)致SRAM最大概率(100%)出現(xiàn)功能故障的TSV開路最小電阻值。

對(duì)應(yīng)的曲線圖如圖3所示,圖中橫坐標(biāo)為TSV開路電阻的相對(duì)最小阻值(Dfi-rel),由式(1)獲得;縱坐標(biāo)為SRAM失效率,最大值為100%。

(1)

圖3 3D SRAM失效率隨TSV開路電阻變化Fig.3 3D SRAM failure probability change under TSV open-circuit resistance

通過圖3中曲線數(shù)據(jù)可得出如下結(jié)論:

在考慮工藝偏差的情況下:

1)當(dāng)注入故障位置的開路電阻阻值等于該故障位置在標(biāo)稱條件下最小可探測(cè)開路電阻值時(shí),引起的存儲(chǔ)器失效概率大約在40%~60%之間(即Dfi-rel=1)。換句話說,在標(biāo)稱條件下,TSV存在開路故障時(shí)會(huì)導(dǎo)致存儲(chǔ)器產(chǎn)生故障行為的最小可探測(cè)值,在考慮工藝偏差對(duì)電路影響的情況下,失效率不到60%。

2)隨著TSV開路電阻值的增加,存儲(chǔ)器的失效率也隨之升高。從圖3中還可以看到,當(dāng)Dfi-rel處在0.5~1.5之間時(shí),TSV的開路電阻只有小幅增加,但由此引起的存儲(chǔ)器失效率卻呈直線上升,最高達(dá)到100%。這說明當(dāng)考慮工藝偏差對(duì)電路的影響時(shí),TSV的開路故障對(duì)存儲(chǔ)器功能故障的影響更嚴(yán)重。

3)對(duì)于Df1處開路故障位置,最小開路電阻值是標(biāo)稱條件下TSV開路電阻值的3.0倍(B_WL),即Dfi-rel=3.0;相應(yīng)地,對(duì)于Df2處開路故障位置,最小開路電阻值是標(biāo)稱條件下TSV開路電阻值的2.5倍(M_WL),即Dfi-rel=2.5;對(duì)于Df3處開路故障位置,最小開路電阻值是標(biāo)稱條件下TSV開路電阻值的1.5倍(B_BL_W),即Dfi-rel=1.5;對(duì)于Df4處開路故障位置,最小開路電阻值是標(biāo)稱條件下TSV開路電阻值的2.0倍(M_BL_S_R),即Dfi-rel=2.0。

除此之外,本小節(jié)還分別對(duì)字線和位線的操作類型以及開路位置進(jìn)行廣泛的模擬研究,模擬結(jié)果如表2所示。

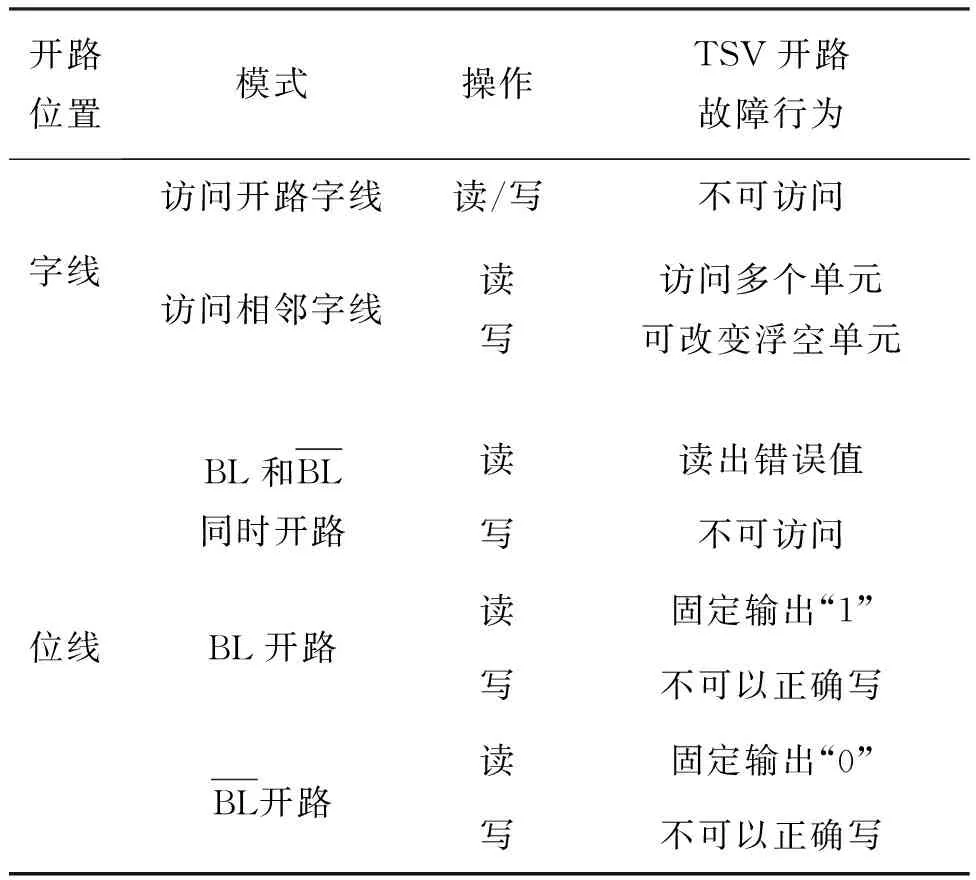

表2 3D SRAM中TSV開路故障行為

字線TSV存在開路故障時(shí),存儲(chǔ)器所對(duì)應(yīng)的故障行為主要有三類,即“不可訪問”“訪問多個(gè)單元”以及“可以改變浮空單元里的值”。位線TSV存在開路故障時(shí),存儲(chǔ)器所對(duì)應(yīng)的故障行為有四類,分兩種情況:當(dāng)兩根位線同時(shí)開路時(shí),故障行為有“讀出錯(cuò)誤值”和“不可訪問”兩類,當(dāng)其中某一根位線開路時(shí),故障行為有“不可以正確寫”和“固定輸出0或1”兩類。

2 故障原語及TSV開路測(cè)試算法

2.1 故障原語定義

功能故障檢測(cè)的兩個(gè)基本組成部分為:讀寫操作序列以及相應(yīng)單元的狀態(tài)變化。因此,3D SRAM中每一種TSV開路故障的單一單元故障原語可采用S,F(xiàn),R的組合來表示存儲(chǔ)器的故障行為;多單元故障用

2.2 故障行為與March元素

訪問多個(gè)單元故障行為,普通的測(cè)試算法就可以檢測(cè)到。針對(duì)訪問多個(gè)單元故障的最簡(jiǎn)化March元素為:(r0,w1)或(r1,w0),其中“”為地址增序,“”為地址降序。

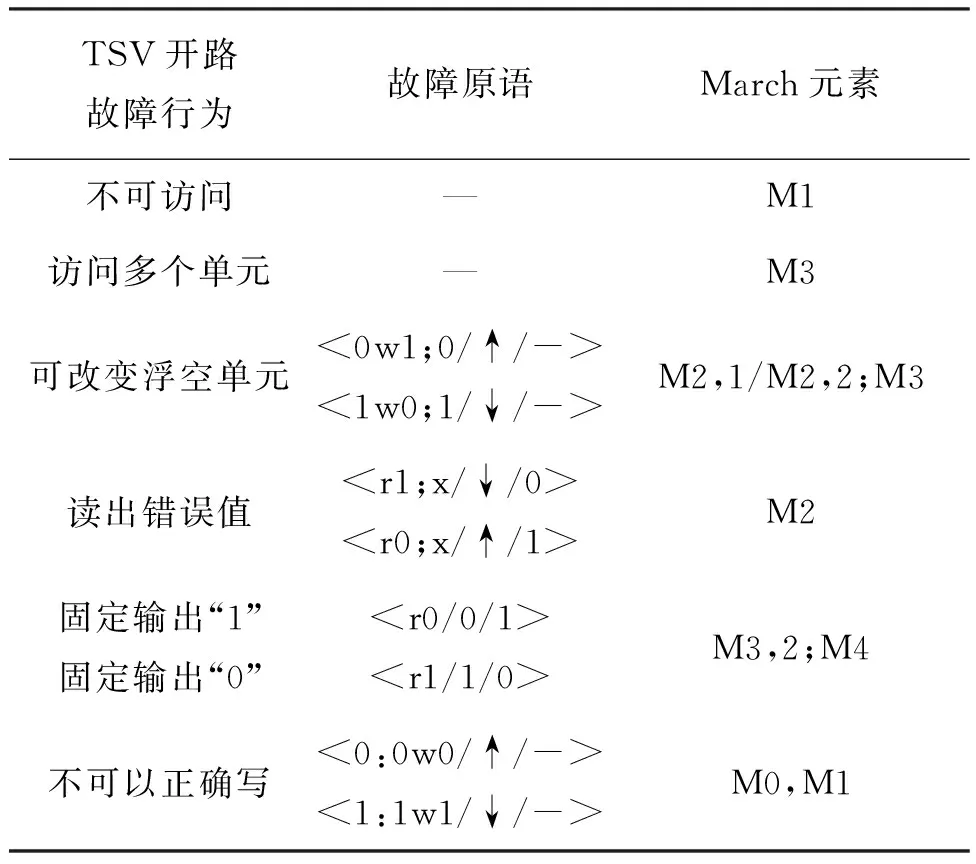

因此,根據(jù)前述3D SRAM中每一種TSV開路故障行為的故障原語定義,可以得到3D SRAM中TSV開路故障的故障原語及其March元素,結(jié)果如表3所示。

表3 TSV開路故障的故障原語及其March元素

2.3 TSV開路測(cè)試算法

表3中所提的這些基本故障類型的March元素可以為本節(jié)TSV開路測(cè)試算法的研究提供基礎(chǔ),通過對(duì)所有測(cè)試序列進(jìn)行算法合并與優(yōu)化,從而得到符合設(shè)計(jì)要求的測(cè)試算法。經(jīng)合并優(yōu)化之后的算法如式(2)所示:

① ②③ ④⑤⑥ ⑦⑧ ⑨

(2)

M0 M1 M2 M3 M4

此算法共九個(gè)操作步驟,分為五個(gè)狀態(tài),分別為①~⑨九個(gè)操作步驟和M0~ M4五個(gè)狀態(tài):

M0:存儲(chǔ)單元初始化為狀態(tài)“1”;

M1:按地址增序?qū)λ写鎯?chǔ)單元進(jìn)行w1和r1的操作;

M2:按地址降序?qū)λ写鎯?chǔ)單元進(jìn)行r1,w0和r0的操作;

M3:按地址降序?qū)λ写鎯?chǔ)單元進(jìn)行r0和w1的操作;

M4:按地址增序?qū)λ写鎯?chǔ)單元進(jìn)行r1操作。

式(2)檢測(cè)故障的原理總結(jié)如表4所示。

表4 TSV開路故障及其March元素檢測(cè)原理

表4中March元素列,Mi表示測(cè)試算法中對(duì)第i個(gè)March元素,Mi,j表示測(cè)試算法中第i個(gè)March元素的第j個(gè)操作,如M2,2表示第2個(gè)March元素中的第2步操作“w0”。

3 TSV開路測(cè)試算法實(shí)現(xiàn)與驗(yàn)證

前面已經(jīng)從理論上推導(dǎo)出了TSV開路故障的測(cè)試算法,本節(jié)將根據(jù)以上研究成果實(shí)現(xiàn)具體的TSV開路測(cè)試算法,并驗(yàn)證提出的TSV測(cè)試算法的正確性和有效性。

3.1 算法代碼實(shí)現(xiàn)

TSV開路測(cè)試算法共五個(gè)狀態(tài),本文采用Verilog語言實(shí)現(xiàn)TSV測(cè)試算法有限狀態(tài)機(jī)的設(shè)計(jì),算法的偽代碼描述如算法1所示。

算法1 TSV開路測(cè)試算法有限狀態(tài)機(jī)

完成整個(gè)TSV測(cè)試算法需要9×N個(gè)循環(huán),因此所有數(shù)據(jù)完成讀寫操作所需的總時(shí)間為9×N×D,其中N為地址深度,D為數(shù)據(jù)位寬。

3.2 算法電路實(shí)現(xiàn)

本文所提測(cè)試算法的一大優(yōu)勢(shì)就是可以采用2D的測(cè)試方法來完成TSV開路故障的測(cè)試,所以該算法的測(cè)試電路依然可以采用典型的BIST測(cè)試電路,如圖4所示。

圖4 BIST測(cè)試電路Fig.4 BIST test circuit

系統(tǒng)工作流程如圖5所示。

圖5 系統(tǒng)工作流程Fig.5 Systematic work flow

當(dāng)進(jìn)入BIST模式時(shí),外部控制信號(hào)BIST_start有效,系統(tǒng)進(jìn)入測(cè)試模式,多路選擇器MUX將選擇從FSM控制器中產(chǎn)生的數(shù)據(jù)作為系統(tǒng)輸入,存儲(chǔ)器輸出的數(shù)據(jù)被送到輸出響應(yīng)比較器,與BIST控制器產(chǎn)生的理想數(shù)據(jù)進(jìn)行比對(duì),進(jìn)而判斷存儲(chǔ)器是否存在故障,如果存在故障,輸出響應(yīng)器的故障標(biāo)志位有效,并向冗余修復(fù)模塊發(fā)送故障地址和故障類型,便于后續(xù)修復(fù)工作。最后,當(dāng)FSM狀態(tài)控制器根據(jù)算法步驟完成所有測(cè)試步驟后,BIST_done信號(hào)有效,表示存儲(chǔ)器完成了自測(cè)試。

當(dāng)BIST_start無效時(shí),系統(tǒng)進(jìn)入正常的功能模式,多路選擇器MUX將選擇從System_in輸入的數(shù)據(jù)作為系統(tǒng)輸入,System_in和System_out有效,如果有錯(cuò)誤單元,系統(tǒng)將按照重新分配的新地址進(jìn)行數(shù)據(jù)存儲(chǔ),并由System_out輸出。

3.3 算法驗(yàn)證

本文采用Verilog和Nanosim仿真工具,對(duì)3D SRAM進(jìn)行測(cè)試。仿真中加入TSV開路故障模型,通過觀察字線開路和位線開路在TSV開路測(cè)試算法中的測(cè)試情況,分析了TSV開路測(cè)試算法的有效性及正確性。

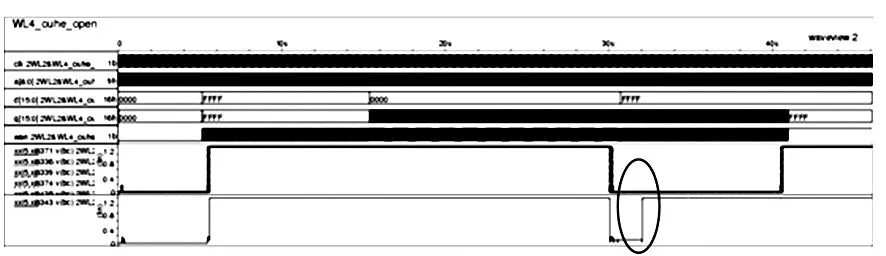

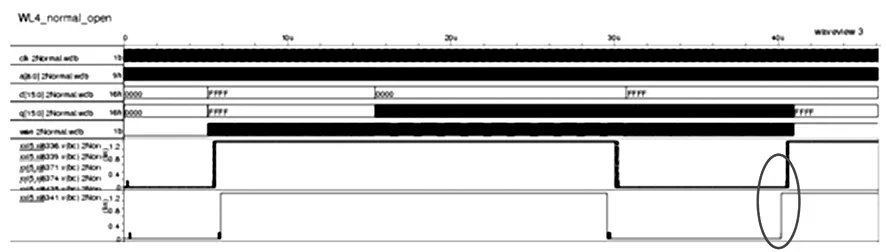

字線TSV存在開路故障的模擬結(jié)果如圖6所示(模擬的是WL2和WL4)。

(a) 注入故障(a) With fault injection

(b) 未注入故障(b) Without fault injection圖6 字線TSV注入開路故障模擬結(jié)果Fig.6 Result of open-circuit fault injection on word line

圖6中,橢圓為TSV測(cè)試算法中的某一步寫操作。從圖6(b)中橢圓可以看出,WL2和WL4上所接單元都在期望的時(shí)間點(diǎn)上寫入了正確的數(shù)據(jù),而圖6(a)橢圓中的波形明顯不同步,這是由于WL4所接的TSV產(chǎn)生了開路故障,在WL4期望的訪問時(shí)間點(diǎn)上并沒有成功寫入數(shù)據(jù),且在訪問WL2的時(shí)候,由于耦合效應(yīng),與WL2的寫操作同步了,所以在WL2寫操作的同時(shí),WL4也進(jìn)行了相同的寫操作。

類似地,可以得到位線的模擬驗(yàn)證結(jié)果。首先往任意一根與圖2中BL相連的位線TSV中注入開路故障,模擬結(jié)果如圖7所示。

圖7 位線TSV注入開路故障模擬結(jié)果Fig.7 Result of open-circuit fault injection on bit line

對(duì)于普通字線和普通位線的模擬結(jié)果可以采用類似的方法得到,整理結(jié)果如表5所示。

表5 開路故障類型統(tǒng)計(jì)

4 結(jié)論

針對(duì)綁定后3D SRAM中TSV的全開路故障展開全面分析,提出一種使用測(cè)試算法來探測(cè)TSV開路故障的方法。該方法將TSV測(cè)試機(jī)制與Memory BIST結(jié)構(gòu)相結(jié)合,可以在不使用TSV專用測(cè)試電路且不增加額外面積開銷的情況下解決3D SRAM中TSV的開路測(cè)試。模擬結(jié)果表明,該TSV測(cè)試算法功能正確,能夠準(zhǔn)確探測(cè)到TSV的開路故障,并快速定位TSV的開路位置,實(shí)現(xiàn)了探測(cè)TSV開路故障的目的。

References)

[1] Koyanagi M, Fukushima T, Tanaka T. Three-dimensional integration technology and integrated systems[C]//Proceedings of Asia South Pacific Design Automation Conference, Asp-Dac 2009, Yokohama, Japan, 2009: 409-415.

[2] Khan N, Rao V S, Lim S, et al. Development of 3-D silicon module with TSV for system in packaging[J]. IEEE Transactions on Electronic Components and Packaging Technologies, 2010, 33(1): 3-9.

[3] Gong S Q, Liu W, Tan J B, et al. Foundry TSV integration and manufacturing challenges[C]//Proceedings of IEEE International Interconnect Technology Conference / Advanced Metallization Conference, 2014: 385-388.

[4] Swinnen B, Ruythooren W, De Moor P, et al. 3D integration by Cu-Cu thermo-compression bonding of extremely thinned bulk-Si die containing 10μm pitch through-Si vias[C]//Proceedings of Electron Devices Meeting, 2006: 1-4.

[5] Huang Y J, Li J F, Chou C W. Post-bond test techniques for TSVs with crosstalk faults in 3D ICs[C]//Proceedings of International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), 2012: 1-4.

[6] Pasca V, Anghel L, Benabdenbi M. Configurable Thru-Silicon-Via interconnect Built-In Self-Test and diagnosis[C]// Proceedings of Test Workshop, 2011: 1-6.

[7] Lin Y H, Huang S Y, Tsai K H, et al. Parametric delay test of post-bond through-silicon vias in 3-D ICs via variable output thresholding analysis[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2013, 32(5): 737-747.

[8] Cuviello M, Dey S, Bai X, et al. Fault modeling and simulation for crosstalk in system-on-chip interconnects[C]//Proceedings of IEEE/ACM International Conference on Computer-aided Design, 1999: 297-303.

[9] Yoon K, Kim G, Lee W, et al. Modeling and analysis of coupling between TSVs, metal and RDL interconnects in TSV-based 3D IC with silicon interposer [C] //Proceedings of the 11th Electronics Packaging Technology Conference. Los Alamitos: IEEE Computer Society Press, 2009: 702-706.

[10] Kim J, Cho J, Kim J. TSV modeling and noise coupling in 3D IC[C]//Proceedings of Electronic System-Integration Technology Conference, 2010: 1-6.

[11] 賀翔.面向三維集成的硅通孔互連信號(hào)完整性與電氣建模研究[D].南京:南京航空航天大學(xué), 2012.

HE Xiang. Signal integrity analysis and electrically modeling of through silicon via connection in 3D integration[D]. Nanjing: Nanjing University of Aeronautics and Astronautics, 2012. (in Chinese)

[12] Woo D, Seong N, Lewis D, et al. An optimized 3D-stacked memory architecture by exploiting excessive, high-density TSV bandwidth [C]//Proceedings of IEEE 16th International Symposium on High Performance Computer Architecture (HPCA), 2010: 1-12.

[13] Loh G H. 3D-stacked memory architectures for multi-core processors[C]//Proceedings of International Symposium on Computer Architecture. IEEE, 2008: 453-464.

Research and implementation of TSV open test algorithm in 3D SRAM

ZHAO Zhenyu, DENG Quan, LI Peng, JIANG Jianfeng, QU Lianhua, TANG Haoyue

(College of Computer, National University of Defense Technology, Changsha 410073, China)

In 3D-IC (three dimensional-integrated circuit) technology based 3D SRAM(three-dimensional static random access memory), a large number of TSVs (through silicon vias) have been implemented in circuits. The manufacturing process of TSV is not mature,which makes TSVs more prone to open defects and brings new challenges to the 3D SRAM test. The existing method of TSV test can find out where the faults are, but it needs extra specific circuit to implement, which increases both the area overhead and its design complexity. In consideration of what was discussed above, a new idea to detect the open defects of TSV based on a test algorithm was proposed. It proved to be an effective method to detect the open defects of TSV in 3D SRAM using BIST(built-in self test) without any extra overhead. Results show that the proposed method has no functional problem with the algorithm and it can realize the purpose of TSV open fault detection.

three dimensional-integrated circuit; through silicon via; open defects; test; algorithm

10.11887/j.cn.201605002

http://journal.nudt.edu.cn

2015-05-30

國家自然科學(xué)基金資助項(xiàng)目(61176030,61272139)

趙振宇(1973—),男,遼寧朝陽人,教授,博士,碩士生導(dǎo)師,E-mail:zyzhao@nudt.edu.cn

TN47

A

1001-2486(2016)05-007-07